基于FPGA的MAC层地址表设计与仿真详情解析

FPGA/ASIC技术

描述

为解决高速以太网链路接口中软件方式实现的MAC层地址表机制在处理效率上受到制约的问题,提出了一种基于FPGA (现场可编程门阵列)硬件电路方式实现以太网交换机中MAC地址表的查找,学习和老化。该方法采用hashing算法建立地址表项索引值与MAC地址之间的对应关系,完成满足平均时间复杂度为O (1)的地址查找。由于实际交换机中地址表容量有限,地址学习只能是MAC地址的子集,通过优化hashing函数降低地址冲突发生的概率以及设计一种地址老化机制提高地址表查找能力。仿真结果表明,地址表机制采用硬件电路方式实现比软件方式处理效率更高。

引 言

在计算机网络中,数据链路层完成节点到节点的通信,二层以太网交换机属于数据链路层设备[1]。MAC (介质访问控制)地址是在网络通信用来识别主机的标识。交换机的缓存中有一个MAC地址表,需要转发数据时,交换机会在地址表查询是否有与目的MAC地址对应的表项,如果有,交换机立即将数据报文往该表项中的转发端口发送;如果没有,交换机则会将数据报文以广播的形式发送到除了接收端口外的所有端口,尽最大能力保证目的主机接收到数据报文。因此,交换机地址表的构建和维护决定了数据转发的方向和效率。

MAC层地址表存储查找多基于hash表。Hashing是一种用于以常熟平均时间插入、删除和查找的技术,hash表通过把关键码值映射到表中一个位置来访问记录。这个映射函数叫做hashing函数,存放记录的数组叫做hash表。交换机地址表存储的是全部MAC地址的一个子集因此必然会发生地址冲突,文献[2-3]对比了几种解决冲突的方法。

MAC地址表的容量是有限的,因此交换机采用老化机制来维护MAC地址表,以保证最大限度地利用地址表项资源。交换机在构建某条表项时,会相应地开启该表项的老化定时器[4],如果在老化时间内,交换机始终没有收到该表项中的MAC地址的报文,交换机就会将该表项删除,失效的表项不会继续占用MAC地址表资源。这样,即使网络中的设备更换或者移除,交换机的MAC地址表始终能保持网络中最新的拓扑结构记录。合适的老化时间可以提高MAC地址表项资源的利用率,但过长或过短的老化时间,反而影响交换机的性能。如果老化时间过长,交换机中保存的MAC地址表项的数量过多会将地址表资源消耗完,网络中的拓扑变化就无法及时更新;如果老化时间过短,则有效的MAC地址表项会被交换机过早删除,从而降低交换机的转发效率。

传统的MAC地址表处理机制主要采用软件的方式实现[5]。随着以太网链路接口的速率从1Gb/s发展到10Gb/s,基于软件的算法在速度上受到串行计算机系统的制约。新一代现场可编程门阵列(FPGA)的出现以后,算法通过硬电路描述,所有的延迟只来源于门电路,而一般门电路的延迟都在ns级别。减少了系统运行所需的时钟周期数,实现了真正的高速率。

1 地址表处理机制

本数字电路设计中,采用单一时钟域的同步时序设计,所有的触发器都是在同一个时钟节拍下进行翻转。这样就简化了整个设计,后端综合、布局布线的时序约束容易实现。

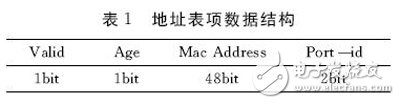

地址表占用的空间由片内存储器RAM 提供,片内存储器是基于FPGA的系统可使用的最简单的存储器,存储、读取是在FPGA内部完成,电路板上无需外部连线,具有最高吞吐量和最低反应延时的,适用于缓存和查找表。地址表表项中至少记录mac物理地址,端口号。每个mac地址表项的数据结构见表1。

定义如下:

Valid:表项有效指示,1代表有效表项,0代表空闲表项。

Age:老化比特,地址表更新时查询的位段,1代表年轻,0代表老化。

Mac address:48bit物理地址。

Port_id:物理地址对应的端口号。

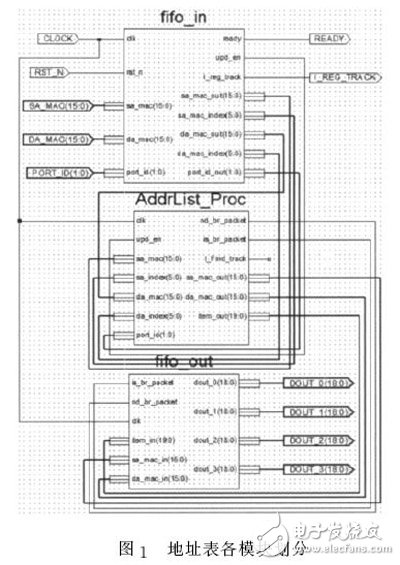

地址表项写入表中的位置即地址学习由源地址(MAC地址)经过hashing算法求得的索引值决定。地址表项的读取即地址表查询由目的地址(物理地址)经过hashing算法求得的索引值决定。Hashing算法本身消耗一部分时序,物理地址的学习和查询就需要等待这部分时序,为了使得地址表处理起来更加清晰、明确,整个设计分为3个模块(如图1所示):地址表的输入调整、地址表处理机制、地址表的输出调整。

模块划分后,本级模块向下一级模块一次性交付需要处理的所有并行数据。

1.1 地址表输入调整(fifo_in)

Fifo_in模块完成两种操作,对输入的MAC地址求解hashing索引值(xx_mac_index);间隔4s产生地址表更新信号(upd_en),更新信号为高电平有效,持续时间由地址表的深度决定,遍历地址表,一个时钟周期处理一个表项。

Hashing算法:为了快速的存取地址表项,采用hashing算法[6]建立地址表项索引值与实际MAC地址之间的对应关系(每个MAC地址只能对应一个索引值,但是每个索引值有可能对应多个MAC地址,即发生了地址冲突)。

使用复杂的hashing算法,会延长计算索引的时间,降低地址表的查找速度,增加交换机的包转发时延。

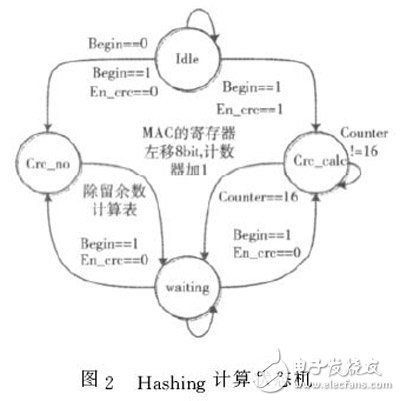

在交换控制芯片设计中本项目算法使用CRC-CCITTD多项式 为hashing函数,48位MAC地址由CRC[7-8]校验方法后的结果通过hashing函数求得16位余数,取结果16位余数中11个比特用于2KB地址表项索引值。Hashing函数计算的状态机如图2所示。

交换机MAC层容纳的地址表大小是有限的,理论上实际的物理地址有2的48次方个,地址表只能记录其中一个很小的子集,因此hashing函数不可避免地将不同的MAC地址映射到相同的地址表项索引值。如果以太网中地址表项索引值与MAC地址存在多对一的情况,就是发生了“地址冲突”。地址冲突的存在也说明总有部分MAC地址丢失,不能被交换机学习到。地址冲突的解决方法在1.2中予以实现。

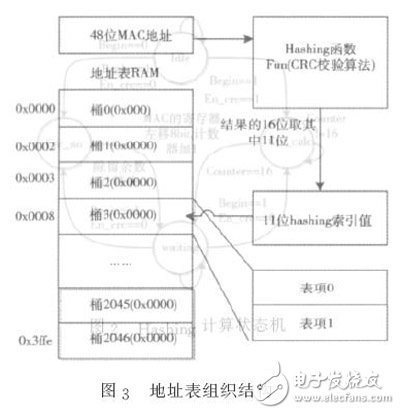

地址表组织结构如图3。图3左边列出的是地址表RAM 中每个hashing桶内表项0在RAM 中的地址。在开始地址存储和查找时,通过CRC校验得到的索引值指向的hashing桶内表项0与表项1被读出,通过对MAC地址域进行比较确定匹配的表项,得到转发端口的信息。

1.2 地址表处理机制的实现方法(AddrList_Proc)

1.2.1 地址学习和查找的实现

以太网帧结构中的源地址(sa_mac)用于地址学习。目的地址(da_mac)用于地址查找。

对于较大吞吐量的交换芯片,能做到平均时间复杂度满足线性的学习和查找。学习和查找采用hashing算法,发生碰撞采用hashing算法,碰撞后采用相邻空间开放定址法(open addressing hashing)[9-10]。

学习的过程如下:

(1)根据hashing索引值sa_index,检索MAC 地址表。

(2)表项中Valid字段若为1代表该表项已占用,转(3),否则表项空闲,转(7)。

(3)表项内容中的MAC地址与sa_mac进行比较,若相同I_Find置1,转(7),否则转(4),此时发生地址冲突。

(4)sa_index+1表项中Valid字段若为1代表此处表项已占用,转(5),否则表项空闲转(7)。

(5)表项内容中的MAC地址与sa_mac进行比较,若相同I_Find置1,转(7),否则转(6),此时发生地址冲突。

(6)此时有超过两个不同的MAC地址映射同一索引值,并且先到的写入sa_index和sa_index+1处。后面到达的MAC地址覆盖掉sa_index处表项,完成一次学习。

(7)写入该位置,Valid置1,Age置1,完成一次学习。

查找的过程如下:

(1)判断是不是广播包,若是转(10),否则转(2)。

(2)根据hashing索引值da_index,检索MAC 地址表。

(3)da_index和da_index+1的Valid字段组成二元组<valid0,valid1>,<0,0>转(4)、<0,1>转(5)、<1,0>转(6)、<1,1>转(7)。

(4)da_mac不在地址表中,转(9)。

(5)da_index+1表项内容中MAC地址与da_mac比较,若两者相同,转(8),否则转(9)。

(6)da_index表项内容中MAC地址与da_mac比较,若两者相同,转(8),否则转(9)。

(7)da_mac在地址表中转(8),否则转(9)。

(8)读取表项内容中的端口号,与da_mac组成一组数据发给到fifo_out,完成一次查找。

(9)广播该MAC地址,发送da_mac和需要广播标志位给fifo_out,完成一次查找。

(10)I_Find标志位为1代表地址表中有广播请求的MAC地址,不需要继续广播下去。I_Find标志位为0代表需要继续广播下去,转(11)。

(11)发送sa_mac和需要广播标志位给fifo_out,完成一次查找。

1.2.2 地址老化的实现

交换机通过端口发送和接收帧的源地址(源MAC地址、端口号)将存储到地址表中。老化时间是一个影响交换机学习进程的参数。为地址表中每条地址项添加一个计数器用于表示该地址项的更新时间,通过查询计数器位是否为零判断一个地址是否已经老化。在更新过程中,所有的输出引脚处于“悬挂”。

老化过程如下:

(1)检测到更新信号upd_en为高电平时,开始遍历整个地址表。

(2)表项中Age字段为1,代表上一次遍历周期到此遍历周期内该表项对应的MAC 地址被重新写入过,转(3),否则(4)。

(3)表项中的Valid字段保持1,Age字段置0。

(4)表项中的Valid字段置0 (删除已老化的)。

(5)等待upd_en为低电平时停止遍历,完成一次地址老化。

3 地址表的输出调整(fifo_out)

Fifo_out模块根据前一级提供的各种标志信号,实现对输出的控制。输入的数据信号有源地址,目的地址,查找到的表项,输入的标志信号有nd_br_packet (需要广播标志),Is_br_packet(是广播包标志)。

Is_br_packet=1,nd_br_packet=0代表“是广播包,不需要广播”,对应地址表处理机制中的事件—接收到广播包中的MAC地址存在地址表中。没有输出。

Is_br_packet=1,nd_br_packet=1代表“是广播包,需要广播”,对应地址表处理机制中的事件—继续广播下去。sa_mac经过封装由dout0~dout3输出。

Is_br_packet=0,nd_br_packet=0代表“不是广播包,不需要广播”,对应地址表处理机制中的事件—单播包中目的地址存在地址表中。表项经过封装,对应端口输出。

Is_br_packet=0,nd_br_packet=1代表“不是广播包,需要广播”,对应地址表处理机制中的事件—目的地址不存在地址表中。da_mac经过封装由dout0~dout3输出。

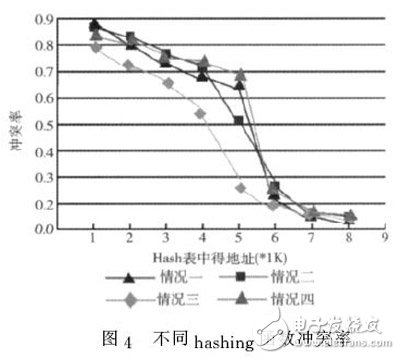

2 不同hashing函数的冲突率

Hashing算法的主要原理就是把大范围映射到小范围,冲突率和hashing函数的选取有密切的关系,图4中选取了4种不hashing函数下发生地址冲突的概率。情况一采用的Hashing函数为MAC地址和自身倒序做异或运算所得的结果经过CRC计算后取最后11位索引值;情况二采用的Hashing函数为MAC地址和自身倒序做异或运算所得的结果经过CRC计算后取前11位索引值;情况三采用的Hashing函数为MAC地址平方后取中间11位为索引值,情况四采用的Hashing函数为将MAC地址分割成位数相同的3部分,叠加这三部分的和取后11位为索引值。

仿真过程描述如下:

48位二进制数表示的范围划分为三子段,每个子段随机生成3000个数。一共有9000个随机MAC地址,依次按照4种情况提供的hashing函数计算结果,索引值一样冲突加一,分别在不同的地址表容量下求冲突率。

不同hashing函数冲突率如图4所示。

仿真结果表明地址表项容量和MAC地址数量接近时基本不发生冲突,在地址表较小情况下对于本次实验给出的信源情况三的hashing函数有较小的冲突率。所以在选取hashing函数时要结合该节点实际收发MAC地址的概率模型,这样才能有效的降低地址冲突发生。

3 设计与验证

仿真过程中,时钟周期100ns,MAC地址取48bit中的后16bit,地址表深度为64,hashing算法采用CRC8取结果的后6bit。这样处理的理由有两点:第一48bit与16bit原理相同,16bit占用的资源少;第二MAC地址前24bit是由设备厂商分配的序列号,对于一部分MAC地址只有后16bit不同。

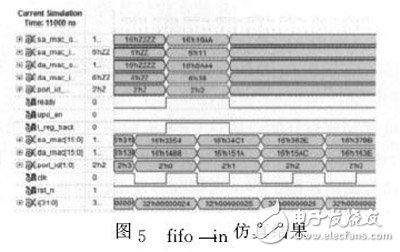

sa_mac既是输入也是输出,fifo_in内的寄存器保存一次输入信号,待hashing算法后和索引值同步输出,如图5所示。

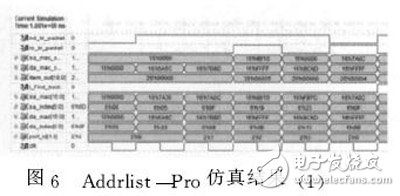

图6的仿真结果中可以看到,1200ns学习到MAC地址(16′h7A0C),1500ns接收到对该MAC地址的广播包,停止继续广播下去。

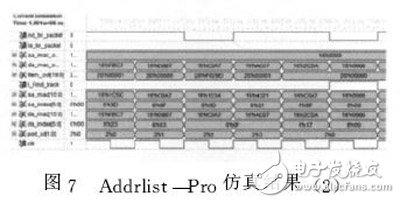

图7的仿真结果中可以看到2100ns查询的目的地址(16’hC0A7)存在于地址表中,它是2000ns写入地址表中的。

图8中所示2600ns开始地址更新,消耗64个时钟周期,遍历所有的表项。9000ns后的输入和地址表更新前得输入相同,可以看出有相同的输出。

图9所示不同的标志信号控制不同的输出,可以看到1700ns和1800ns都是向端口2转发数据。1400ns向4个端口广播。

4 结束语

对于以太网交换机来说,主要工作是根据收到数据帧中的目的MAC地址,对MAC地址表进行查找,把数据帧转发到相应的端口。MAC地址表的查表效率直接影响交换机的性能。Hashing算法可以实现高效率的存储和查找,但存在地址冲突,选择合适的hashing函数是解决问题的有效途径之一。比如可以统计交换机各端口hashing索引值的概率分布,找出发生冲突较高的区域,对这些区域按照概率进行排序,hashing函数针对冲突域中概率大的几个MAC地址来构造。

-

科普|什么是MAC地址、MAC码、OUI码、蓝牙串号2026-04-16 285

-

MAC地址的作用范围,MAC地址怎么申请?2024-12-19 3052

-

怎么绑定IP地址和MAC地址2024-12-01 3449

-

怎么申请MAC地址?MAC地址申请流程分享2024-07-10 1891

-

MAC地址申请MAC码购买流程MAC地址哪里申请MAC地址作用2023-03-01 4929

-

认知无线电MAC层与应用层仿真平台2021-09-15 788

-

mac地址和ip地址有什么区别2018-03-06 9178

-

交换机MAC地址表特性配置2016-12-27 775

-

三层交换机MAC地址表特性配置2016-12-25 619

-

10-MAC地址表特性配置命令2016-12-17 694

-

ARP地址解析协议简介2012-02-24 3891

-

mac_mac地址是什么2011-12-14 5677

-

什么是MAC地址表2010-01-08 1155

-

MAC地址2009-12-26 1480

全部0条评论

快来发表一下你的评论吧 !