一种基于FPGA的多通道数据采集系统设计与实现

FPGA/ASIC技术

描述

摘要:基于PCI 总线和FPGA 的特点,设计了具有高精度、高稳定性及高准确性的多通道信号采集传输系统。系统采用以FPGA 为主控单元,通过控制模拟选择开关ADG706 及A/D 转换器AD7667 实现对模拟信号的采集,并由FIFO 缓存经过PCI总线将所采集的数据上传至上位机显示分析。经实际应用,系统性能稳定,符合设计要求。

数据采集就是将被测对象( 外界、现场) 的各种参量( 物理量、化学量、生物量等) 通过各种传感元件做适当转换后,再经调理、采样、量化、编码、传输等步骤,最后送到控制器进行数据处理或存储记录的过程[1]。数据采集技术可以将许多抽象的模拟量数字化,进而给出其量值,或通过信号处理对该模拟量进行分析。基于FPGA 器件的高时钟频率、内部延时小、时序简便精确控制、编程配置灵活等优点,故本系统以FPGA 为核心来控制通道切换模数、转换、数据编帧及传输。此外基于PCI 总线稳定性高,数据传输速度快,扩张性强的优点,本设计中采用PCI 总线实现上位机与FPGA 的无缝连接,完成上位机与FPGA 控制模块之间的数据传输。

1 系统设计

1. 1 系统组成

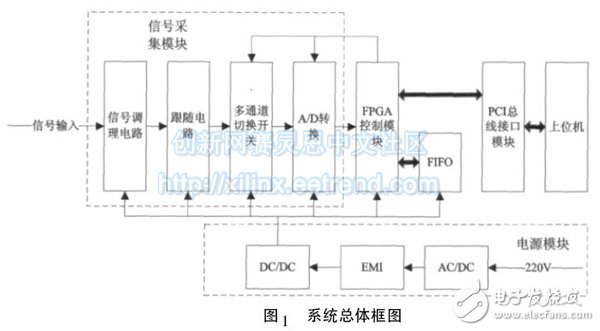

本系统对29 路高频压力信号进行采集( 其中速变信号4 路采样率40 K,缓变信号25 路采样率6. 6 K) 。设计采用模块化设计。各个模块之间既整体协调又相互独立构成整个系统。系统主要由信号采集模块、FPGA 控制模块、PCI 总线接口模块、电源模块组成。模块化设计既有利于电路调试、编程和扩展,又能很方便的快速定位问题和解决问题。本系统中考虑到控制程序占用较多的逻辑资源,FPGA 控制模块采用Xilinx 公司spartan—3 系列芯片XC3S400 作为主控芯片与外围器件进行连接。系统总体框图如图1 所示。

1. 2 系统原理

本系统上电随即实现采集与传输功能,无需等待命令字。模拟信号通过运放OPA4340 进行放大,再进入一阶滤波电路和电压跟随器进行信号调理,之后在FPGA 的时序控制下通过模拟选择开关ADG706的选通进入AD7667 进行模数转化,转换后的数据缓存到FIFO 中,最后经PCI 总线接口电路上传至上位机进行显示和分析。整个系统的供电由电源模块提供,电源模块自带EMI 模块进行滤波保护,向FPGA控制模块提供所需的5 V、3. 3 V 和1. 2 V 电压,向信号采集模块提供所需的5 V、3. 3 V 电压。

2 硬件电路设计

2. 1 信号调理及跟随电路

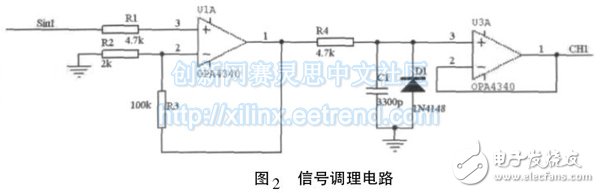

高频压力信号进入系统后,首先要经过信号调理电路完成对信号的放大、滤波、跟随保持,调理电路如图2 所示,经过信号放大电路,将信号幅值调节到0—5 V 的范围内,之后通过一阶滤波电路,其中滤波电路截止频率为,,这样把输入信号的频率范围调理成系统采集信号的频率范围内,最后进入模拟开关ADG706。图2 中的D1 起到了反向保护的作用。

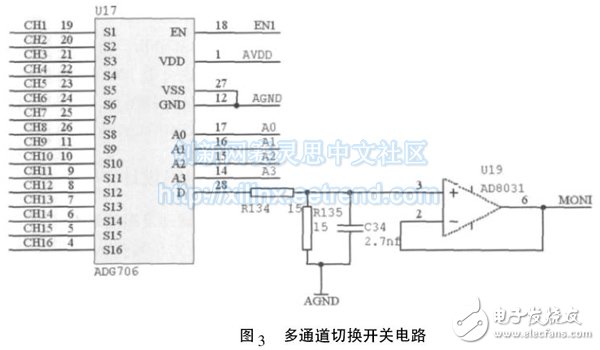

2. 2 多通道切换开关电路

16 路选择模拟开关ADG706 把各路模拟信号切换依次送入模数转换器AD7667 进行A/D 转换,设计中可使用2 个ADG706 实现29 路模拟信号的切换。在设计过程中FPGA 控制模块对于模拟开关

ADG706 的使能控制和通道切换控制是设计中应该注意的问题。此外信号在通过ADG706 后将进入电压跟随器,这里的跟随器选用的高速运放AD8031,根据芯片资料知其最大可带容性负载为15PF,远远高于AD8031 的驱动能力。因此有可能会造成振荡问题。设计中增加一阶有源滤波电路可以滤除高频振荡。多通道切换开关电路如图3 所示。

2. 3 A \D 转换电路

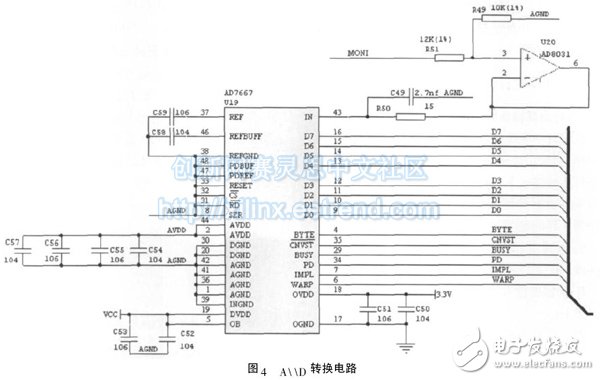

本系统中模数转换器AD7667,具有16 bit /1 M的采样能力。输入信号经其转换后变成16 位数字信号,在FPGA 控制下依次取其高8 位与低8 位,根据设计的帧结构的顺序依次写入FIFO 缓存器。设计中模拟信号在进入AD7667 之前经过调理后稳压在0 ~ 5 V 范围内。由于AD7667 内部具有2. 5 V 的基准电压源,所以进入AD7667 前信号通过电阻网络进行分压,经过分压处理后的电压范围为:

( 0 ~5 V) ×10 K/( 12 K +10 K) = ( 0 ~2. 25 V) 。

结果在AD7667 的电压输入范围之内。此外C49 为去耦电容,作用是用来降低电源、噪声等产生的干扰。A\ \D 转换电路如图4 所示。

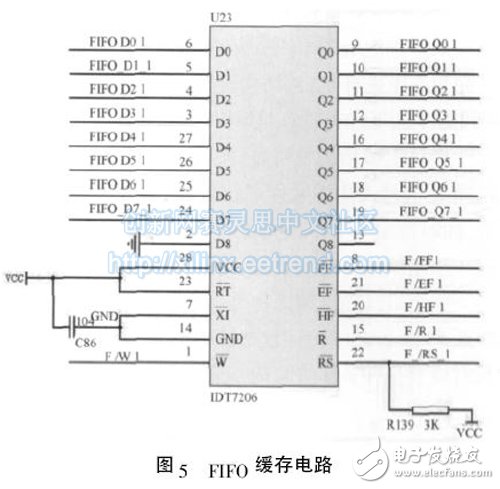

2. 4 FIFO 缓存电路

本系统采用外部FIFO IDT7206,这是由于外部FIFO 引脚功能较多,尤其是半满信号以及空信号都易于判断,此外也不会占用FPGA 的内部资源。本设计中IDT7206 采取半满即读的工作方式,这样不会发生FIFO 缓存数据溢出现象,并且可以将缓存的数据高速读出,达到高速缓存的目的。FIFO 缓存电路如图5 所示。

2. 5 PCI 接口模块设计

PCI 总线接口模块采用PLX 公司的PCI 总线通用接口芯片PCI9054,PCI9054 符合PCI V2. 1 和V2. 2 规范,具有两个独立的可编程DMA 控制器,数据宽度32 位,理论数据传输速率最高可达132 MBps[2]。为了满足上位机与PCI 总线模块之间的高速传输,PCI9054 采用DMA 突发传输模式来实现。

FPGA 控制模块检测到FIFO 的“半满”信号为低电平时,将FIFO 中的数据读取出来,组成规定的数据包,控制PCI9054 向上位机传输数据。

3 系统时序设计

3. 1 信号采样帧结构的设计

在设计中采样帧结构即信号采样顺序( 通道切换顺序) 是最需要优先考虑的部分。在保证各路信号采样率的情况下,在一个帧结构中平均同一信号的各采样点时间间隔是设计的关键之处。在本系统中需采样的速/缓变模拟信号参数如下:

S: 为速变信号,4 路( S1 ~ S4 ) ,采样率: 40Ksps,8 bit;

H: 为缓变信号, 25 路( H1 ~ H25) ,采样率: 6. 6Ksps,8 bit;

速变信号采样率为缓变信号采样率的6 倍,因此不需要提升系统总体采样率。首先确定帧结构的行数: 将采样率高的S 放置在帧结构的最起始位置,因其采样率为6. 6 Ksps 的6 倍,所以一帧中S信号采样点应为H 信号的6 倍,由此确定帧结构中一列为6 个采样点,帧结构行数为6,且帧结构的前4 列为S 的采样点,所以帧结构列数应大于4。

再确定帧结构的列数: 由于一列为6 个采样点,这样H 信号占用的采样点数为25,需要5 列才能放下,同时空出5 个空位正好用来放置帧计数与帧标记。于是帧结构的列数为: 4 + 5 = 9。

于是可以确定帧结构是一个6 × 9 的矩阵,总采样点54 个。其中帧计数与帧标记占用5 个采样点,我们得到一种采样帧结构如表1 所示。

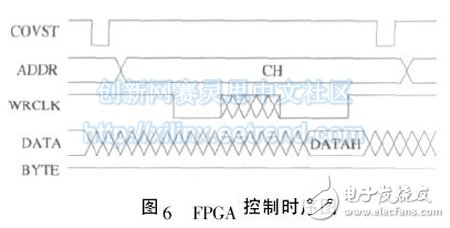

3. 2 FPGA 的时序设计

本系统中模拟开关的选通,A \ \D 的控制,FIFO的读写均是由FPGA 进行控制,信号的总采样率为

6. 6 K × 54 = 360 Ksps。FPGA 的时钟频率为54MHz,因此FPGA 内部逻辑在每一次采样点上均有150 个状态机可供使用,这对于模拟开关通道切换、A\ \D 模数转换和FIFO 缓存已经完全足够。此外模拟开关切换与启动A \ \D 转换被尽量分开,这样安排主要是为了让模拟信号在通道切换后,A \ \ D采样前有足够的时间稳定下来,以提高采样精度[3]。FPGA 控制时序图如下图6 所示。

图6 中: COVST 为AD 采样控制信号,低电平有效; ADDR 为输出的模拟开关切换地址; WRCLK 为FIFO 写信号,上升沿有效; DATA 为将写入FIFO 中的数据; BYTE 为字节输出控制信号,低电平时取数据的低8 位,高电平时取数据的高8 位。

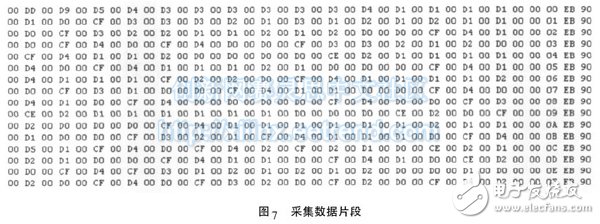

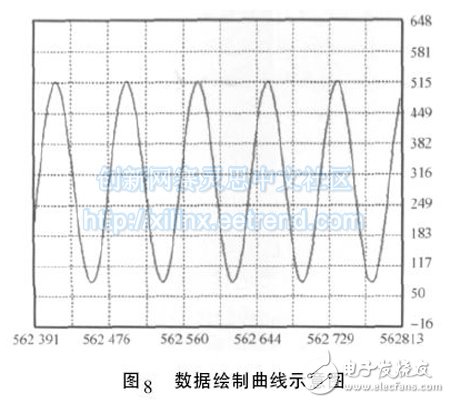

4 测试结果分析

在实际应用中,通过PCI 总线将采集到的数据上传至上位机,其中上传的一部分数据如图7 所示。由图7 可知上传的数据帧格式完整,帧标志对齐,帧计数正确,没有丢数现象。数据通过上位机处理后绘制出的曲线如图8 所示。其中信号输入为正弦波。由图8 可知系统采样功能正常,波形完整。综上所述,本系统功能完整,性能满足设计要求。

5 总结

本设计针对采集传输技术要求及当前技术实现手段,完成了多通道信号采集传输系统设计,将FPGA 和PCI 总线技术进行了有机的结合,充分利用了各自的优点,使采集系统具备实时采集、即时显示、即时反馈、自动处理、自动传输的功能,为现场采集数据的真实性、有效性、实时性、可用性提供了可靠保证。

-

FPGA的多通道数据采集传输系统2024-12-09 1788

-

多通道数据采集串扰问题怎么解决2024-07-02 4069

-

多通道数据采集系统的优缺点2024-07-01 3808

-

旋转环境下基于FPGA的多通道数据采集系统设计2023-08-08 2453

-

求一种多通道同步数据采集及压缩系统的设计方案2021-04-28 1661

-

一种基于FPGA的多通道频率测量系统的实现方法介绍2019-06-27 1866

-

一种支持Android的多通道数据采集卡设计_苏湘2017-01-19 904

-

一种多通道数据采集系统设计研究2012-10-17 1046

-

基于FPGA和USB接口的多通道数据采集系统2011-12-28 794

-

基于FPGA的多通道同步数据采集存储系统2010-12-27 1217

-

基于FPGA的多通道数据采集系统设计2009-10-25 1792

全部0条评论

快来发表一下你的评论吧 !