基于FPGA的AFC环解调FSK信号原理及设计

FPGA/ASIC技术

描述

摘要:介绍了相乘微分型AFC环解调FSK信号的原理,分析了环路的控制模型。采用模块化的设计思想,利用VHDL语言设计了相乘微分型AFC环路,阐述了关键部件的设计方法。在Xilinx的FPGA器件XC3S200-4FT200上对AFC环进行了实现,利用Modelsim6.0软件进行了仿真测试。仿真结果表明,环路工作稳定,满足性能要求。

1 引言

FSK(Frequency Shift Keying ,频移键控)是继ASK(Amplitude Shift Keying,振幅键控)之后出现比较早的一种调制方式。由于FSK的抗衰落能力较强,因而在一些衰落信道的传输中得到了广泛的应用[1]。近年来,数字调频技术有了相当大的发展。CPFSK(Continuous Phase Frequency Shift Keying ,连续相位频移键控)在调制指数h=0.7及采用相干检测及延迟判决的条件下,功率与频带利用方面可以达到比BPSK(Binary Phase Shift Keying,二进制相移键控)好1dB的水平。MSK(Minimum Shift Keying,最小频率键控)在功率与频带的利用方面都与4PSK相当,而且它的频谱特性比PSK信号优越,已在数字卫星通信系统中采用[2]。

FSK信号的解调方法很多,总的来讲可以分为相干解调法和非相干解调法两类。相干解调法是指需要获取相干载波信号的解调方法,非相干解调法则不需在解调前获取相干载波。从抗干扰性能看,相干解调法是最佳的,但从FSK信号中提取相干载波比较困难,实现技术相对较为复杂,所需硬件资源也较多,故目前多采用非相干解调法。文献[1]给出的一种最佳非相干解调器结构,在相同误码率的条件下,所需的信噪比只比相干解调法高1~2dB。非相干解调法的种类很多,如基于FFT的频谱分析法[3、4]、基于自适应滤波的解调法[5]、差分检波算法[6]、AFC(Automatic Frequency Control,自动频率控制)环解调法等。

近年来,随着可编程逻辑器件的发展,采用FPGA实现信号解调等数字系统具有速度快、使用灵活、可编程配置等一系列优点,已逐渐成为数字通信系统设计与实现的首选方案。本文主要讨论相乘微分型AFC环解调FSK信号的原理及FPGA(Field Programmable Gate Array,现场可编程门阵列)实现方法。

2 AFC环解调FSK信号的工作原理

2.1 相乘微分型AFC环原理

AFC环是一个负反馈系统,从电路结构上看,AFC环主要有3种结构形式[7]:相乘微分型、延迟叉积型以及离散傅立叶变换型。本文只讨论应用比较广泛的相乘微分型AFC环路。

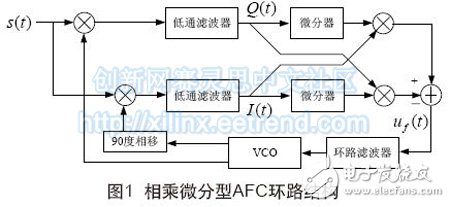

相乘微分型AFC环路的结构如图1所示[7]。如果接收信号与本振信号存在频差,则在一定时间间隔内必然存在相差,将鉴相器输出的相位误差信号微分后,得到反映频差的误差信号,此信号经环路滤波器平滑处理后,控制VCO(Voltage Controlled Oscillator,压控振荡器)的振荡频率向输入信号频率靠近,最终使得频差近似为零。

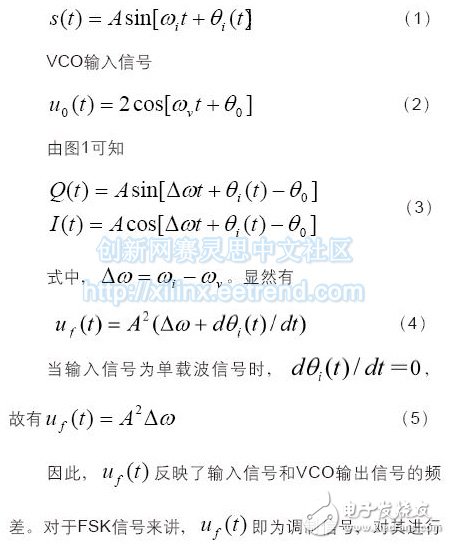

设输入信号

滤波判决,即可完成FSK信号的解调。

2.2 AFC环的数学模型分析

由相乘微分型AFC环路的工作原理可知,AFC环是一个频率负反馈系统,可以得到图2所示的AFC环路的频率控制模型。环路中,鉴频器的输出电压与频率误差信号成正比。对于无线通信中常用的锁相环路来讲,VCO的输出信号对相位信号有一个积分关系,压控振荡器是锁相环路中的固有积分环节[9];在AFC环路中,VCO的输出信号与信号频率成正比,环路不再具有积分环节,因此,整个AFC环不是一个二阶线性系统,而是更为简单的一阶线性系统。

AFC环路的工作过程完全可以采用通用的一阶线性环路模型来进行分析。根据一阶线性环路的工作原理可知[8],环路锁定的条件是环路增益K 必须大于固有频差Δω ,且环路增益越大,则捕获及锁定时间越短。由图2可以看出,环路增益由鉴频器、滤波器、VCO增益组成,控制环路总增益的方法比较灵活,可以通过增加环路中任何一个环节的增益来实现提高环路总增益的目的。

3 AFC环的VHDL设计

工程实例中,输入数据为连续相位的2FSK信号,量化位数为8比特,原始数据速率为4Mbit/s,采样速率为32MHz,载波频率为6MHz,调制指数为0.715,FPGA系统时钟速率为32MHz。

3.1 环路参数设计

(1) 滤波器参数设计

由图1所示,AFC环中有3个滤波器,其中两个正交支路的低通滤波器完全相同,用于滤除前级混频后的高频分量;环路滤波器用于滤除鉴频器(由微分器及乘法器组成)输出产生的高频分量,产生VCO的控制信号。低通滤波器通带截止频率选择与信号带宽一致,考虑发射端成形滤波器的作用,本实例中取3.6MHz。过渡带带宽的选择原则为[9]:一是必须确保滤除相邻的A/D镜像频率成分;二是需要滤除数字下变频引入的倍频分量,本实例中取8.4MHz。

根据AFC环的工作原理,鉴频器的输出信号反映了原始调制数据的变化情况,为进一步简化解调器结构,可以将环路滤波器也设计成FIR低通滤波器,这样就可以直接从环路滤波器的输出信号中获取解调数据。环路滤波器的带宽、过渡带等参数与混频器的低通滤波器保持一致。

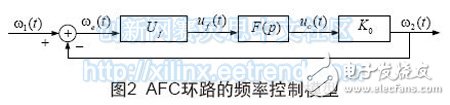

采用MATLAB很容易根据滤波器参数设计出FIR滤波器的系数并画出频率响应图,如图3。

设计出FIR滤波器系数后,还需要对其进行量化处理,以适应FPGA处理。13比特量化后的滤波器系数如下:

h_pm=[ 20,77,28,-197,-319,123,1145,2047,2047,1145,123,-319,-197,28,77,20]

由于中频信号的采样位数为8比特,本地振荡器的输出载波信号也选用8比特。根据二进制乘法原理,考虑节约寄存器字长,同时保留全部有效数据位,AFC环前端混频乘法器为8 × 8的乘法器,取低15比特的有效位输出数据。混频器的低通滤波器取全部的28比特有效位输出数据。环路滤波器的滤波器系数与混频器中的滤波器完全相同,但输入输出数据位宽不同,输入数据位宽由积分器及后端的加法器决定。本实例中,环路滤波器输入有效数据位宽取17比特,输出信号取全部30比特有效数据。

(2) 微分器参数设计

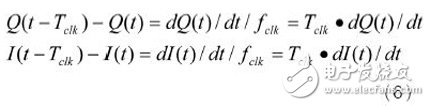

采用FPGA进行数学意义上的微分运算十分困难。根据微分的运算规则,可以采用一种简单的近似处理方法,即通过求取前后两个数据之差来代替微分运算。前后两个数据之间的时间间隔为一个系统时钟周期,则有

根据式(6)可知,采用前后两个数据之差来代替微分运算,相当于数学上的微分运算乘以系统时钟速率这个常数,反映在整个AFC环路上则相当于环路增益乘了一个常数。

由图1所示,微分运算后还需要进行乘加运算,考虑到FPGA芯片中集成的硬件乘法器IP核大多数都是18x18比特的,综合考虑运算速度、硬件资源及运算精度,微分器后面直接采用18x18比特的乘法器,且取36比特输出数据,这样乘法后面的减法运算不再需要进行符号位扩展,可直接相减。

根据上面的分析,环路滤波器的输入数据位宽为36比特。如果采用所有36比特数据作为滤波器输入,则需耗费大量的硬件资源,滤波器输出数据位宽也将达到49比特。这样多的数据位宽虽然可以获得极高的运算精度,但所需的代价是硬件资源的成倍增加,以及运算速度的降低。综合考虑各种因素的影响,该实例采用17比特有效数据作为环路滤波器的输入,滤波器的有效输出数据位宽为30比特。

(3) NCO参数设计及环路增益计算

FPGA中可以采用NCO(Numerical Controlled Oscillator,数字控制振荡器)来实现VCO的功能。NCO的参数设计比较简单,驱动时钟频率取系统时钟即可,为32MHz;频率字位宽取环路滤波器输出的有效数据位宽,为30比特;频率字更新周期取一个系统时钟周期;输出的本地载波信号数据位宽与输入数据位宽相同,为8比特。则NCO的频率分辨率

解调,环路增益K 只要大于1.43M即可, K 值越大,则环路锁定速度越快。

对于AFC环来讲,整个AFC环路为线性一阶环,环路的增益实际上就是NCO的输入电压幅值与频率字更新周期的乘积。考虑到微分运算对环路增益的贡献,由于NCO的输入数据有效位宽为30比特,则环路总增益因此,环路能够稳定跟踪FSK信号的变化,解调出原始数据。

3.2 环路的VHDL设计

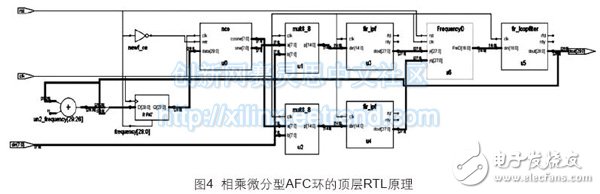

根据图1的结构,在完成AFC环路各部件的参数设计之后,本文采用VHDL语言对相乘微分型AFC环进行了设计,图4是AFC环顶层文件用Synplify Pro综合后的RTL原理图。由图4中可以清楚地看出系统由1个NCO模块(u0),2个8×8 bit的乘法器模块mult8_8(u1,u2),2个低通滤波器模块fir_lpf(u3,u4),1个环路滤波器模块(u5),1个鉴频器模块FrequencyD(U6)以及少量逻辑电路组成。其中的nco模块、乘法器模块、低通滤波器模块、环路滤波器模块均由ISE提供的IP核直接产生。鉴频器由两个微分器、两个乘法器及一个减法器组成,其中微分器采用前后两个数据相减的方法获取。

4 AFC环的FPGA实现及仿真测试

本实例的目标器件为XC6SLX16-2CSG225,FPGA实现后,查找表资源(Slice LUTs)占用了491个(5%),存储块资源(RAMB8BWERs)占用了1个(1%),乘法器DSP资源(DSP48A1s)占用了28个(87%),全局时钟资源(BUFG/BUFGMUXs)占用了1个(6%)。最高系统时钟频率可达83.25MHz,显然满足工程实例中要求的32MHz。从系统所占用的资源来看,普通逻辑资源占用较少,乘法器资源用得比较多,乘法器资源主要用于滤波器等乘法运算。

进行系统的FPGA测试之前,首先需要编写测试激励文件代码产生测试数据。测试数据通过MATLAB软件仿真产生,并将量化后的数据写入TXT文本文件中,激励文件通过读取TXT文件内容产生测试数据。

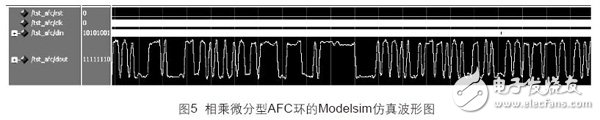

图5为采用Modelsim 6.0软件仿真AFC解调FSK信号的工作波形图。从仿真图中可以清楚地看出环路滤波器的输出信号,即FSK的解调信号dout呈现规则波形,只需对解调信号进行抽样判决即可完成FSK信号的数据解调。

5 结束语

FSK信号的解调方法很多,非相干解调法因为实现简单,性能优良而得到了更为广泛的应用。本文对相乘微分型AFC环的模型进行了讨论。在进行环路的FPGA实现时,关键在于设计环路各部件的参数,以及运算中数据有效字长的处理。仿真结果表明,设计的相乘型AFC环可以有效解调FSK信号。

-

fsk调制解调原理 Fsk调制体制的主要优点2024-02-03 6976

-

怎样用FPGA实现FSK调制解调呢?2023-04-06 3486

-

FSK调制解调方法简析2023-03-31 6555

-

FSK信号的解调原理 自适应解调FSK原理2020-11-03 49379

-

基于FPGA的DSTFT算法对FSK信号解调的改进2017-11-15 1177

-

利用锁相环芯片NE564和CD4046实现FSK信号的调制与解调电路的设计2017-10-30 49419

-

基于Duffing振子的微弱FSK信号解调万云朝2017-03-19 983

-

FPGA实现2FSK数字信号调制解调2012-03-23 3434

-

FSK信号非相干解调的数字实现2011-12-28 1797

-

新型FSK解调算法在来电显示中的应用2011-09-02 1312

-

基于傅里叶变换(DSTFT)的移频键控(FSK)信号的解调2009-10-23 5689

-

车载FSK信号的2种解调算法及其DSP的应用实现2009-07-08 810

-

FSK信号解调电路MT8841原理及应用2009-04-29 1679

-

FSK解调电路图2008-04-21 7089

全部0条评论

快来发表一下你的评论吧 !