基于SERDES时钟的频率跟随的设计

FPGA/ASIC技术

描述

前言

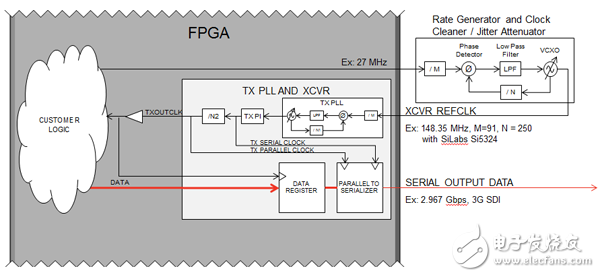

在很多无线或者有线的系统应用中,都需要器件的接收端能够和链路的发送端的频率做跟随。通常的实现方案都是通过将SERDES的恢复时钟引到芯片外部,然后通过一个cleanup PLL过滤抖动,然后同时再生出低相位抖动的跟随时钟,然后将此时钟作为SERDES的参考时钟。其典型场景如下:

图1 传统频率跟随方案

但这类解决方案,对于要求做频率跟随的接口非常多的应用如POS接口,显然是非常不合适的。XILINX的7系列SERDES发送侧的PI(Phase Interpolator)功能,给这类应用场景提供了非常完美的解决方案。

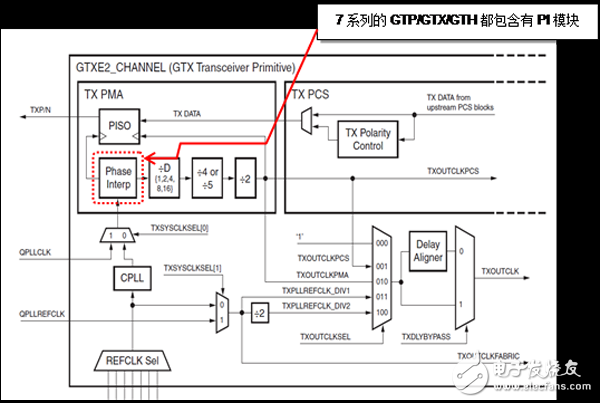

XILINX SERDES发送侧PI功能介绍

XILINX的7系列SERDES的发送方向的结构图如下:

图2 7系列SERDES发送方向结构图

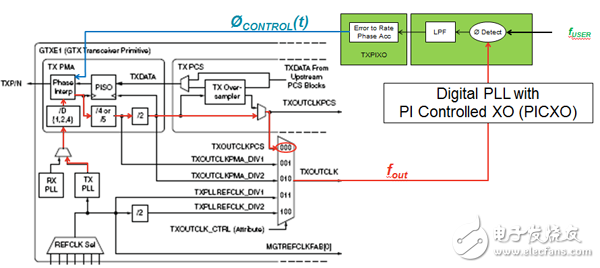

这个PI模块能够根据要求对SERDES的发送串行时钟进行插相处理以达到对频率进行调整。利用这个功能,如果我们能以发送侧的时钟和接收端的恢复时钟的偏移作为依据,对SERDES的发送串行时钟进行调整,那么我们所需要的频率跟随功能就将实现。基本实现框图如下:

图3 XILINX 7系列SERDES的频率跟随方案基本框图

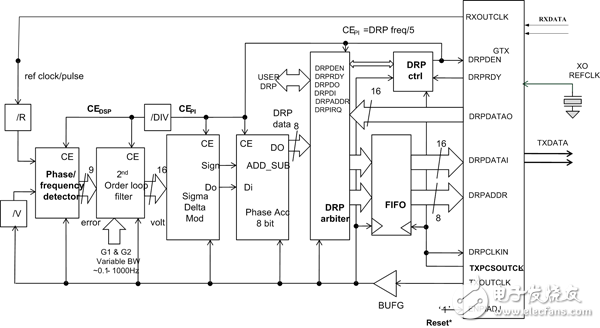

PICXO IP介绍

针对图2所示的系统结构,XILINX提供了一个完整IP解决方案,详细情况可以参阅XAPP589( )。PICXO IP的框图如下:

图4 PICXO 框图

PICXO IP的关键是其提供的DPLL功能。此IP提供了丰富的配置接口,方便用户生成自己需要的环路滤波带宽。也提供了Hold功能,以满足某些需要Holdover功能的场景应用。

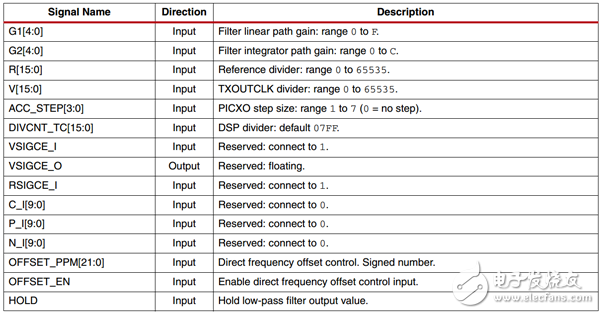

图5 PICXO的配置接口

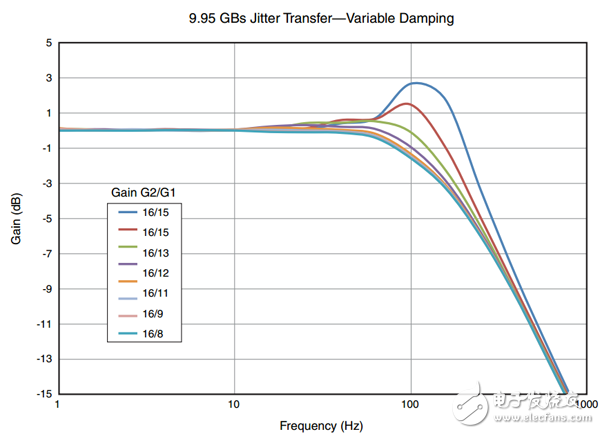

通过调整DPLL的参数(G1,G2,R,V,ACC_STEP,DIVCNT_TC),可以生成各种带宽的数字低通滤波器。下图就是各种配置下的抖动传递函数。

图6 PICXO的抖动传递函数

性能测试结果

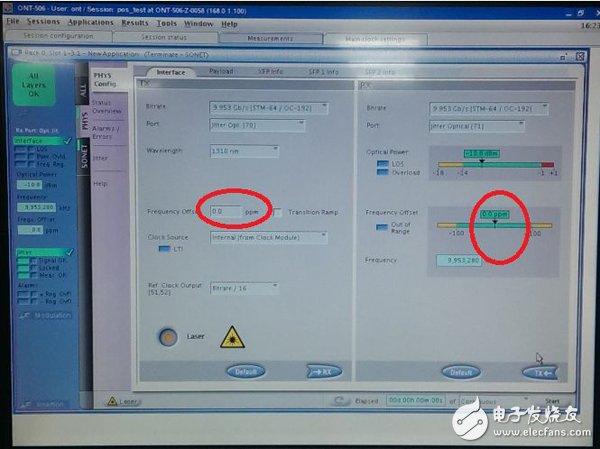

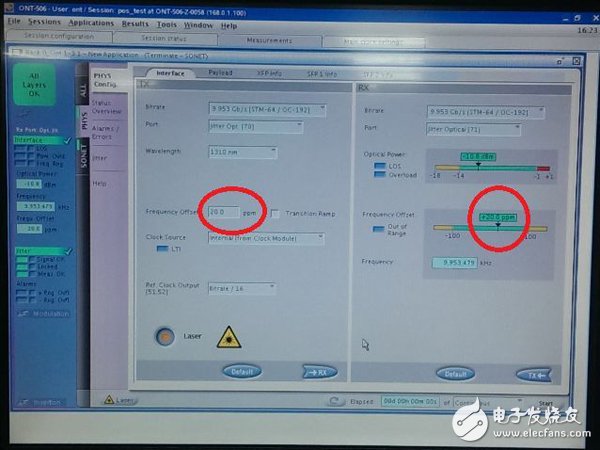

采用XILINX 7系列SERDES提供的PI功能,能满足目前通讯应用中的大部分频率跟随应用。以常见的POS接口和OTUe2接口测试为例,其都能满足要求。下面的附图为OC-192的测试结果:

图7 PI功能演示图1

图8 PI功能演示图2

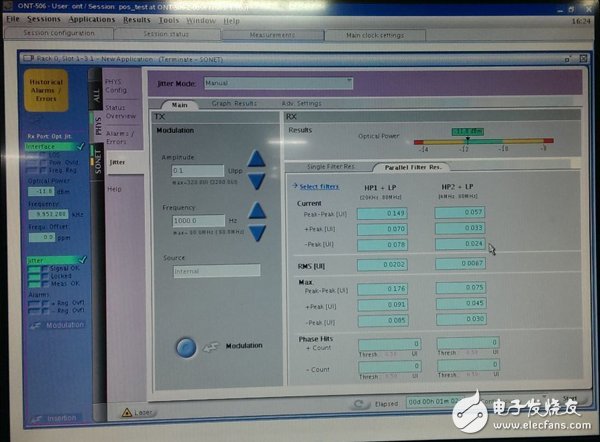

图9 OC-192应用下的发送抖动测试

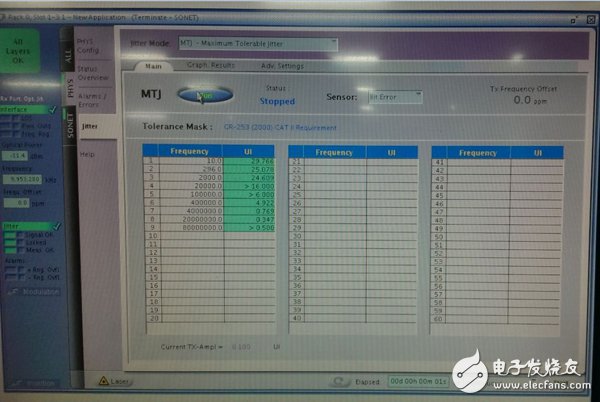

图10 OC-192应用下的接收抖动容忍测试

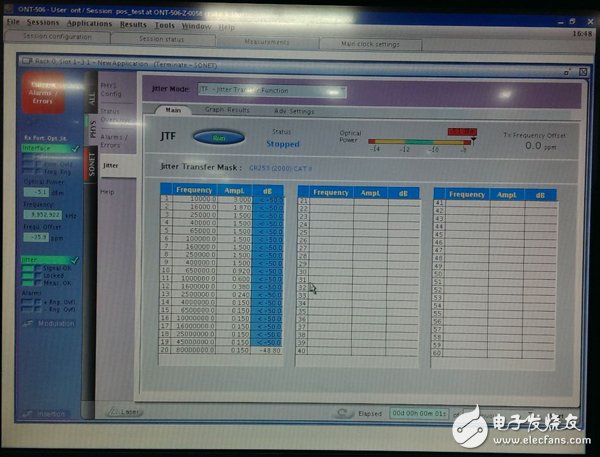

图11 OC-192应用下的接收抖动传递函数测试

后记

得益于XILINX的QPLL和PI的优良性能,给大家在需要做频率跟随时提供了一个非常有竞争力的解决方案。成本,单板面积以及功耗都能面面兼顾。目前已经在大型设备商得到大规模应用。

-

电压跟随器的频率响应2025-02-18 1054

-

SerDes是怎么设计的?(一)2023-10-16 3063

-

怎样去设计SerDes2021-10-18 1995

-

SerDes知识详解 精选资料推荐2021-07-28 1596

-

SerDes知识详解 精选资料分享2021-07-26 1318

-

SERDES的优势 SERDES演变的看法2021-07-23 5186

-

单通道56G的SERDES,参考时钟如何选取?2020-11-12 5825

-

Virtex7的SERDES运行的最大频率是多少?2020-07-30 1435

-

SERDES接口电路设计2019-05-29 3688

-

请教关于C6678的serdes模块2018-08-06 2544

-

什么是时钟频率_时钟频率详解和编程2018-04-28 46753

-

SERDES数字系统高效时钟设计解析2017-10-26 1227

-

参考时钟对SERDES性能的影响2017-02-10 6641

-

SERDES在数字系统中高效时钟设计方案2012-02-16 11098

全部0条评论

快来发表一下你的评论吧 !