一种基于FPGA的SDRAM设计与逻辑时序分析

FPGA/ASIC技术

描述

摘 要: 由于同步动态随机存储器SDRAM 内部结构原因导致其控制逻辑比较复杂。现场可编程逻辑门阵列FPGA作为一种半定制电路具有速度快、内部资源丰富、可重构等优点。本文设计了一种基于FPGA 的SDRAM 控制器, 在介绍控制器的逻辑结构的基础上, 对FPGA 与SDRAM 间数据通信进行了时序分析, 实现SDRAM 带有自动预充电突发读写和非自动预充电整页读写。

0 引 言

SDRAM( Synchronous Dy namic Random Access Memory) 具有价格低廉、容量大、速度快等优点, 但是SDRAM 的控制逻辑相对复杂, 对时序要求也比较严格, 这就需要有一个专门的控制器。而FPGA( Field Programmable Gate Array) 具有高速率、多接口、可重构等特点, 基于FPGA 的SDRAM 控制器设计能够大大缩短开发周期, 简化设计方法。以往有很多关于SDRAM 控制器设计的文章, 但很少从FPGA 时序分析的角度考虑读写数据的准确性, 本文应用FPGA 构建SDRAM 控制器, 并对FPGA 与SDRAM 构建模型进行时序分析, 完成功能仿真和时序仿真, 最终通过板级调试实现SDRAM 的正常读写。

1 控制器系统设计

1. 1 SDRAM 简介

SDRAM 的功能管脚可分为控制信号、地址信号和数据信号三类。

控制信号主要有片选信号、时钟信号、时钟使能信号、行列地址选择信号、读写信号及数据有效信号。

地址信号分为块地址、行地址和列地址, 其中行列地址是分时复用的。在行激活命令时锁存行地址, 在读写命令时锁存列地址。

数据信号为双向信号以减少管脚连接, 受数据有效信号控制。

SDRAM 在正常工作前需要有初始化过程:

( 1) 上电后等待200us 使电源及时钟信号稳定。

( 2) 对SDRAM 所有的BANK 进行一次预充电, 使器件中的存储阵列处于准备状态。

( 3) 完成至少8 次自动刷新操作, 使SDRAM 内部的刷新及计数器处于正常运行状态。

( 4) 配置工作模式寄存器。

SDRAM 要周期性进行自动刷新操作以保证内部数据不会丢失, 目前公认的行刷新周期为64ms,既可集中刷新也可以分散刷新, SDRAM 内部有刷新地址计数器, 每完成一次自动刷新计数器会自动加1。

SDRAM 的读写通过寄存器配置可以实现突发长度及突发类型的设置。

突发读写长度为1, 2, 4, 8 或整页模式。通过在读写命令有效时设置地址位的第10 位可以实现带预充电的突发读写, 预充电命令可以用来结束当前活动行的操作。对于正常突发读写在同一行操作时只需在第一次进行行激活, 以后的若干次操作中写入列地址即可。若要进行不同行间的切换首先需要预充电关闭当前活动行, 然后在执行行激活命令激活下一操作行。而带有预充电的突发读写在每次操作完成后自动进行一次预充电关闭当前活动行, 因此在每次读写时首先都要进行行激活然后再发出读写命令。

整页读写模式可以实现整页内任意长度的读写, 最大长度为一般为256, 在每次读写完成后需要发出突发终止命令来结束读写, 若要进行下一行操作要发出预充电命令关闭当前行。

1. 2 SDRAM 控制器结构

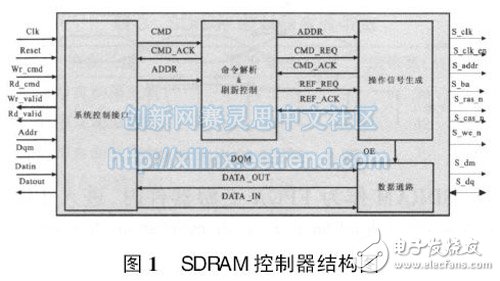

系统采用模块化设计, 可划分为4 个模块, 如图1 所示, 包括系统控制接口模块、命令解析与刷新控制模块、操作信号生成模块和数据通路模块。系统控制接口模块主要由状态机完成初始化工作及生成CMD 命令; 命令解析与刷新控制模块主要将CMD的命令解析发出命令请求同时根据刷新计数器发出刷新请求; 操作信号产生模块由仲裁器仲裁请求生成各种命令信号送给SDRAM 器件; 数据通路模块控制数据流的传输方向并产生有效地数据输入输出。

1. 3 各模块设计

1. 3. 1 系统控制接口模块

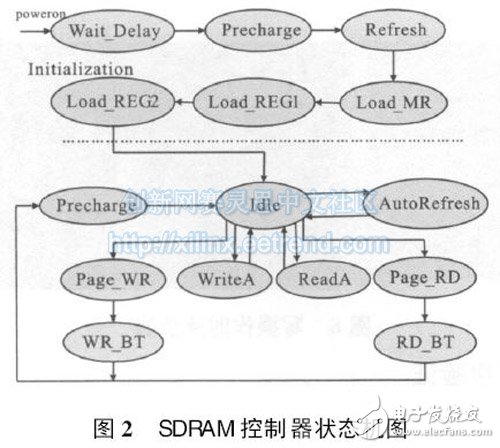

该模块通过状态机实现SDRAM 初始化和控制指令产生功能, 图2 为状态机图。SDRAM 初始化过程主要包括: 在系统上电后通过计数器产生200us 等待时间, 其次执行一次预充电命令, 然后完成8 次自刷新操作, 最后配置寄存器。

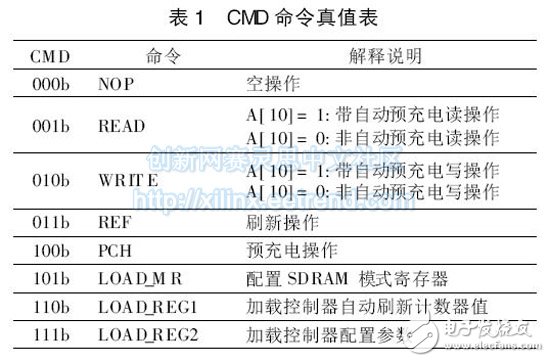

在控制接口模块根据接收外部命令和后端模块响应信号生成CMD 命令送入后端模块进行相应操作, 表1 为CMD 信号真值表。

1. 3. 2 命令解析与刷新控制模块

此模块主要将CMD 命令进行解码送入下一模块中, 同一时刻只允许一种命令请求输出。在寄存器配置过程中将控制器参数配置值和刷新计数器值加载到内部寄存器中。此时刷新控制模块开始计数, 当达到寄存器内预设值时发出刷新请求, 当刷新响应后计数器继续工作, 周而复始。

1. 3. 3 操作信号生成模块

此模块首先接收命令请求和刷新请求, 通过仲裁器根据刷新请求优先级高于命令请求的原则响应请求同时生成SDRAM 对应操作信号送到SDRAM中。同时此模块生成数据使能信号OE 送到数据通路模块控制数据流向。

由于SDRAM 地址信号是分时复用的, 控制器的地址信号ADDR 从高到低依次为SDRAM 的块地址、行地址、列地址。在此模块中将ADDR 中包含的块、行、列地址写入响应的寄存器中, 在行激活命令时将块地址、行地址送入SDRAM, 在读写命令发出时将列地址送入SDRAM。

1. 3. 4 数据通路模块

此模块主要在读写操作期间处理数据路径的操作, OE 信号作为三态门使能端, 写操作时其为高有效数据DATAIN 经过SDRAM 双向数据线DQ 写入SDRAM; 读操作时当OE 为低数据从DQ 读到FPGA 内部DATAOU T 数据总线上。DQM 为数据掩码, 当DQ 为16 位时, DQM 宽度为2, 通过设置DQM 不同位的值可以实现DQ 位高低8 位的读写;同时通过在不同的读写时刻设置DQM 的值可以实现SDRAM 任意地址的读写操作。

2 仿真验证

2. 1 功能仿真

在控制器设计代码完成后首先要进行功能逻辑仿真来检查设计语法是否正确及设计功能是否完全实现。测试向量的编写一定要具有完备性, 对SDRAM 的设计工作模式都要考虑进内。

图3 为控制器的功能仿真。此时突发长度为8, tRCD 延迟为3 个时钟, tCAS 延迟为3 个时钟。写命令发出后, 在写数据使能信号有效时数据被写进SDRAM; 读命令发出后, 在读数据使能信号有效时数据从SDRAM 中读出。

2. 2 时序仿真

时序仿真是在设计完成综合布局布线后将器件延时及布线延时反标到仿真文件中进行的一种仿真过程, 时序仿真更切近器件的实际行为。在时序仿真阶段首先进行时序分析, 若信号不满足的时序要求则添加相应时序约束, 再次仿真验证以保证所有信号能够正确写入读出。

2. 2. 1 时序分析

由于SDRAM 的管脚信号都是在时钟信号的上升沿有效, 通过SDRAM 数据手册得知各个信号建立保持时间。同样从SDRAM 进入FPGA 的数据信号也必须满足FPGA 的建立保持时间。

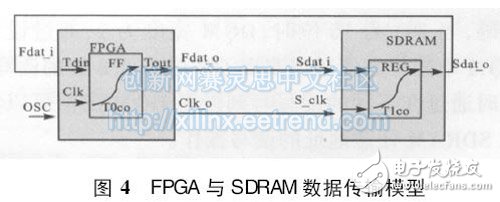

图4 为FPGA 与SDRAM 数据传输模型, 其中:

T din 为数据从FPGA 的IO 口到内部寄存器的传输时间;

T 0co 为数据在FPGA 内部寄存器传输时间;

T out 为数据从FPGA 寄存器输出端到IO 口的传输时间;

T pcb 为数据在PCB 板走线时间;

T 1co 为数据在SDRAM 内部寄存器传输时间。

假定所有信号在PCB 走线延时都是相等的。外部时钟源经过全局时钟网络进入FPGA, 同时从FPGA 输出时钟信号到SDRAM。通过时钟管理单元DCM 的设置可以实现clk 与s_clk 的零相偏移。

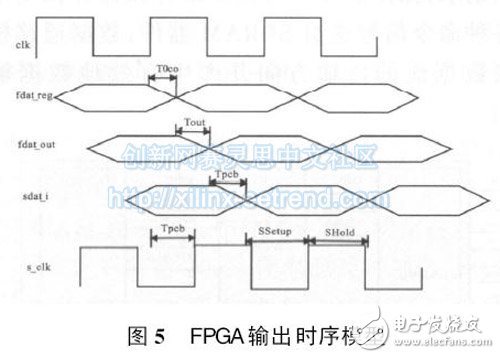

SDRAM 作为FPGA 下游器件时, 进入SDRAM的数据信号在时钟上升沿需满足建立保持时间。如图5 所示, 当SSetup 和SHold 分别满足SDRAM 中数据建立和保持时间时, 数据将正确写入SDRAM中, 若不满足要求时由于T0co 根据特定的器件其值一般是固定的, 可以适当约束Tout 时间来达到时序要求。

SDRAM 作为FPGA 上游器件时, 进入FPGA的数据信号在时钟上升沿也必须满足建立保持时间。若不满足可以通过时序约束数据从FPGA 的IO 到内部寄存器的传输时间Tdin 来达到时间要求。

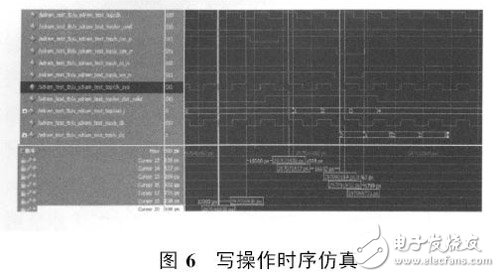

2. 2. 2 时序仿真与验证

图6 为SDRAM 控制器写操作的时序仿真, 从波形中可以看出时钟周期Tclk= 10000ps, SSetup=1763ps, SHold= 6799ps。查阅SDRAM 数据手册得知满足建立保持时间。

3 板级验证

在完成仿真后生成下载文件加载到FPGA 中,添加测试逻辑使SDRAM 中无法观测的数据通过如LED 显示确保读写正确。同时可以借助在线逻辑分析仪ChipScope 快速检测和定位问题所在。

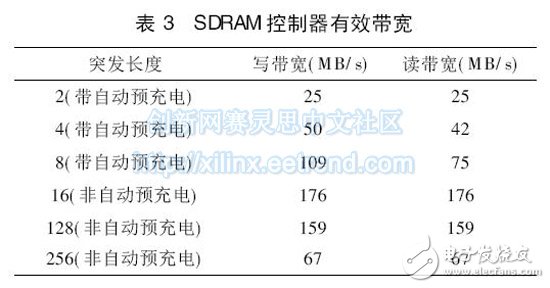

4 结论与分析

本设计开发环境为ISE12. 2, 仿真环境为Modelsim6.5。FPGA 器件为XILINX- SPARTAN3 -XC3S400, 速度等级为- 4。SDRAM 型号为HYNIX-HY57V641620FTP- 6。表2 列出了控制器的资源利用率; 在读写带宽方面系统主频最高能达到100MHz, 表3 为在100MHz 主频下各种模式的读写有效带宽。

由于采用带预充电的读写操作在每一次操作完成后SDRAM 会自动预充电, 相当于关闭当前活动行, 在执行下一次操作时即使是同一行操作也得先执行行激活命令, 再执行读写命令, 这在一定程度上影响了SDRAM 的有效带宽。而整页读写每次操作完一次进行一次预充电, 随着突发长度的增加, 减少了一些命令操作和等待时间, 使带宽大大增加。

本文按照FPGA 的开发流程设计了SDRAM 控制器, 对FPGA 与SDRAM 数据接口进行了时序分析, 并进行了时序仿真。通过板级验证保证了设计的正确性。此控制器按照参数的设定能够在不同的模式下工作, 具有一定通用性。

-

一文解析FPGA的片上资源使用情况(组合逻辑及时序逻辑)2018-04-18 18957

-

FPGA读写SDRAM的实例和SDRAM的相关文章及一些SDRAM控制器设计论文2018-12-25 1742

-

fpga时序逻辑电路的分析和设计2012-06-20 9982

-

零基础学FPGA (二十六)从静态时序分析到SDRAM时序收敛 上2015-03-31 15361

-

FPGA实战演练逻辑篇48:基本的时序分析理论12015-07-09 5629

-

FPGA实战演练逻辑篇49:基本的时序分析理论22015-07-14 3680

-

如何去实现一种基于FPGA的SDRAM控制器设计呢2021-11-04 3280

-

在FPGA中何时用组合逻辑或时序逻辑2023-03-06 896

-

一种基于FPGA技术的虚拟逻辑分析仪的研究与实现2008-11-27 572

-

基于DDR SDRAM控制器时序分析的模型2011-09-26 1141

-

FPGA项目应用之逻辑程序和sdram程序2016-01-21 489

-

一种设计同步时序逻辑电路的新方法2017-02-07 1114

-

一种可延长静态时序分析仪精度的时序签核工具2019-08-13 4172

-

华为FPGA硬件的静态时序分析与逻辑设计2020-12-21 1662

-

基于FPGA的一种SDRAM控制器简易化设计方法2023-10-26 478

全部0条评论

快来发表一下你的评论吧 !