UART的Verilog程序设计

通信设计应用

描述

Verilog是描述复杂的硬件电路,设计人员总是将复杂的功能划分为简单的功能,模块是提供每个简单功能的基本结构。设计人员可以采取“自顶向下”的思路,将复杂的功能模块划分为低层次的模块。这一步通常是由系统级的总设计师完成,而低层次的模块则由下一级的设计人员完成。自顶向下的设计方式有利于系统级别层次划分和管理,并提高了效率、降低了成本。“自底向上”方式是“自顶向下”方式的逆过程。

使用Verilog描述硬件的基本设计单元是模块(module)。构建复杂的电子电路,主要是通过模块的相互连接调用来实现的。模块被包含在关键字module、endmodule之内。实际的电路元件。Verilog中的模块类似C语言中的函数,它能够提供输入、输出端口,可以实例调用其他模块,也可以被其他模块实例调用。模块中可以包括组合逻辑部分、过程时序部分。

那么UART的Verilog程序怎么设计呢?一起来了解一下关于接收模块uart_receiver设计和发送模块uart_transfer的设计。最后奉上UART串口通信协议的详细介绍。

UART的Verilog程序设计:

本次在设计UART的Verilog程序时,我们采用的UART通信协议是:1个起始位,8个数据位,无校验位,1个停止位。

波特率:我们采用9600波特率,但在FPGA分频电路上我们产生了一个9600*16倍的波特率,即FPGA的16个脉冲接收一位PC端的数据。为当采样到RXD数据起始位信号有效时,0-7-15开始计数,其中7为数据的中点,最稳定的时刻。因此在此时采样数据,能够达到最稳定的效果。

接收模块uart_receiver设计

1)异步数据的同步化

由于PC和FPGA端的数据不同步,为了保证数据的同步,需要将外部输入信号同步化。采用简单的D触发器时序电路。

2)数据接收状态机的设计

状态机分配表:

R_IDLE:初始化等待状态

R_START:接收到起始位0(还要判断是否为数据抖动)

R_SAMPLE:接收数据

R_STOP:等待停止位结束,回到初始化状态

3)设计程序步骤:

两段式状态机

第一段:采用组合逻辑取判断状态转换的条件

(1)在初始化状态下检测起始位,来实现状态的转换。R_IDLE

(2)判断起始位是否抖动,在中点检测信号,当计数结束(SMP_TOP)数据依然有效,则表示起始位的开始。 R_START

(3)接收8位数据,采用在数据中点采样。 R_SAMPLE

(4)UART结束位的等待,完成一帧数据的接收。 R_STOP

第二段:采用同步时序电路同步接收

最后输出数据捕获使能信号rxd_flag,作为后续模块的捕获使能信号。

发送模块uart_transfer设计

1)数据接收状态机的设计

状态机分配表:

T_IDLE:初始化等待状态,等待发送使能信号

T_START:数据发送,发送完毕回到初始化状态,等待下一次发送使能。

2)设计程序步骤:

两段式状态机

第一段:采用组合逻辑取判断状态转换的条件

(1)在初始化状态下检测发送使能信号,来实现状态的转换。T_IDLE

(2)发送10位数据,采用在计数中点发送。 等待下一次发送 T_START

第二段:采用同步时序电路同步逐位发送UART数据。10个数据需要按照UART的通信协议发送不得有误。

最后输出数据发送完成信号txd_flag,作为后续模块的使能信号。

UART串口通信协议

UART使用的是 异步,串行通信。

串行通信是指利用一条传输线将资料一位位地顺序传送。特点是通信线路简单,利用简单的线缆就可实现通信,降低成本,适用于远距离通信,但传输速度慢的应用场合。

异步通信以一个字符为传输单位,通信中两个字符间的时间间隔多少是不固定的,然而在同一个字符中的两个相邻位间的时间间隔是固定的。

数据传送速率用波特率来表示,即每秒钟传送的二进制位数。例如数据传送速率为120字符/秒,而每一个字符为10位(1个起始位,7个数据位,1个校验位,1个结束位),则其传送的波特率为10×120=1200字符/秒=1200波特。

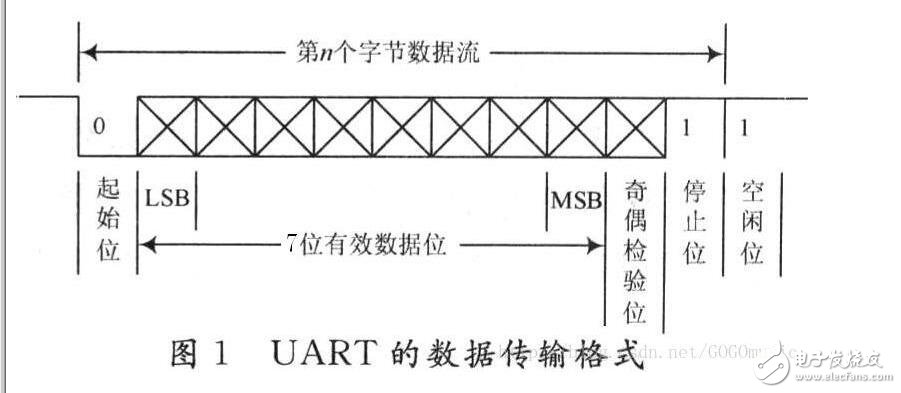

数据通信格式如下图:

其中各位的意义如下:

起始位:先发出一个逻辑”0”信号,表示传输字符的开始。

数据位:可以是5~8位逻辑”0”或”1”。如ASCII码(7位),扩展BCD码(8位)。

校验位:数据位加上这一位后,使得“1”的位数应为偶数(偶校验)或奇数(奇校验)。

停止位:它是一个字符数据的结束标志。可以是1位、1.5位、2位的高电平。

空闲位:处于逻辑“1”状态,表示当前线路上没有资料传送。

异步通信是按字符传输的,接收设备在收到起始信号之后只要在一个字符的传输时间内能和发送设备保持同步就能正确接收。

- 相关推荐

- 热点推荐

- uart

-

Verilog HDL程序设计案例2023-02-13 824

-

Verilog教程之Verilog HDL程序设计语句和描述方式2020-12-09 1366

-

基于verilog的秒脉冲程序设计2017-05-08 2624

-

Verilog HDL应用程序设计实例精讲2016-05-20 2681

-

Verilog HDL程序设计-135例2015-11-06 1067

-

Kinetis E系列上的UART引导加载程序设计2015-11-02 680

-

Verilog HDL程序设计与实践(xilinx)2014-11-21 11294

-

Verilog HDL程序设计与实践2013-03-29 7753

-

《Verilog HDL 程序设计教程》2012-08-10 4578

-

Verilog HDL程序设计教程_王金明2011-09-22 2601

-

Verilog HDL程序设计教程2009-11-25 13183

全部0条评论

快来发表一下你的评论吧 !