Vivado 学习之编写IP核并通过AXI协议与ARM通信

FPGA/ASIC技术

描述

最近发现了一块好玩的板子,PYNQ 这块板子最大的特点就是可以将所写的IP核封装成Python库的形式,然后通过在板载的xlinux系统下用户可以选择通过Jupiter编辑器实时的编写Python脚本,然后Python脚本调用编写好的IP核对FPGA进行重构,使开发变得更加灵活方便。PYNQ doucument 这是PYNQ的官方文档感兴趣的可以看一下。

还有就是学生购买PYNQ的话会有教育专享价,原价2000多的板子只要998就可以拿下。

以下正文。

1. Vivado 部分

1.老套路

1.打开vivado(注意不是vivado hls),建立工程,选择你手里板子的型号,这里我手里的PYNQ芯片型号是CLG400。

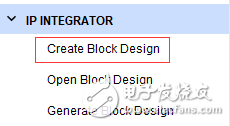

2.建立好工程后还是老套路,IP INTEGRATOR下Create Block Design。

然后添加ZYNQ的IP核

然后点击Run Block Automation

这样zynq的IP核就添加完毕了。

2.添加你自己的IP核,这里就拿点灯来作例子。

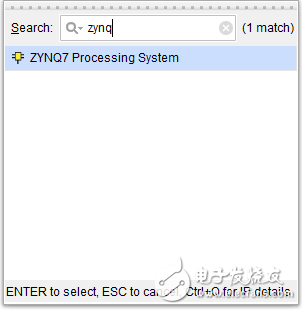

1.点击Tools下的Create and Package New IP

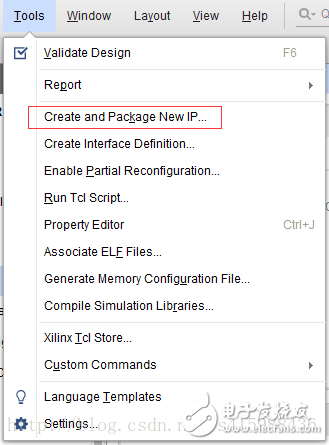

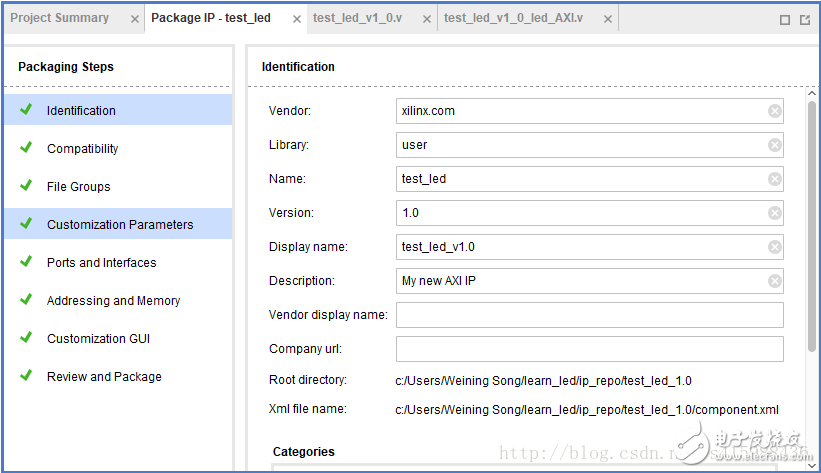

2.选择Create AXI4 Peripheral,然后会出现几个配置页面可以修改自己的ip核的名字和接口类型位宽等信息,一般一直下一步就可以。

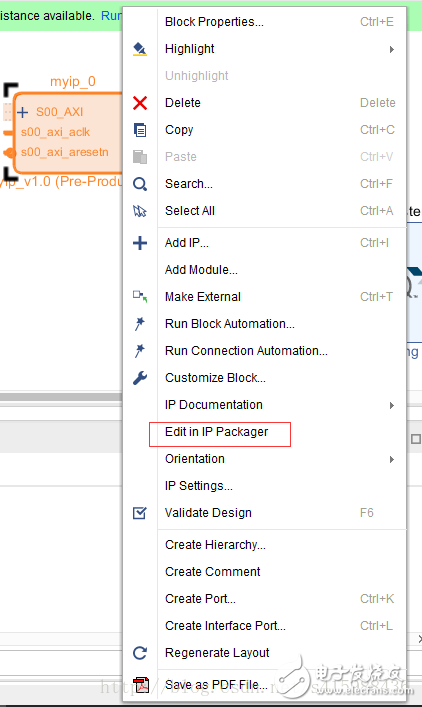

3.完成后IP核库会出现你刚刚创建的IP核,然后右键选择Edit in IP Packager

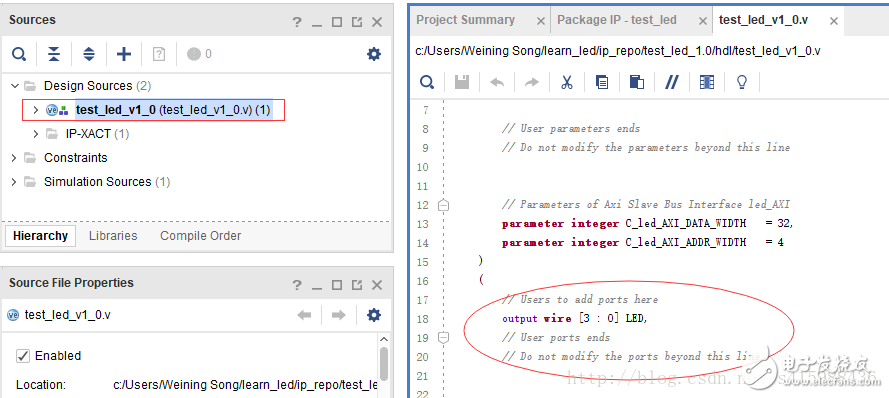

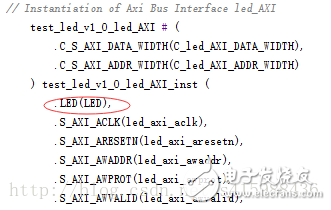

4.进入IP核编辑页面,首先在顶层添加接口和实例调用。

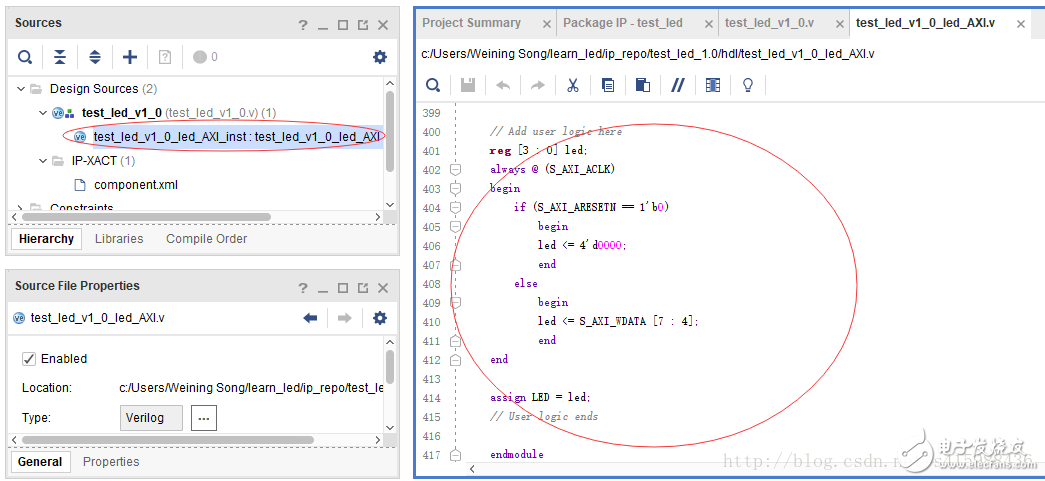

5.然后再下层中同样的需要添加接口,然后在添加自己IP核的实现。

6.全部完成后选择package IP

出现如下界面。

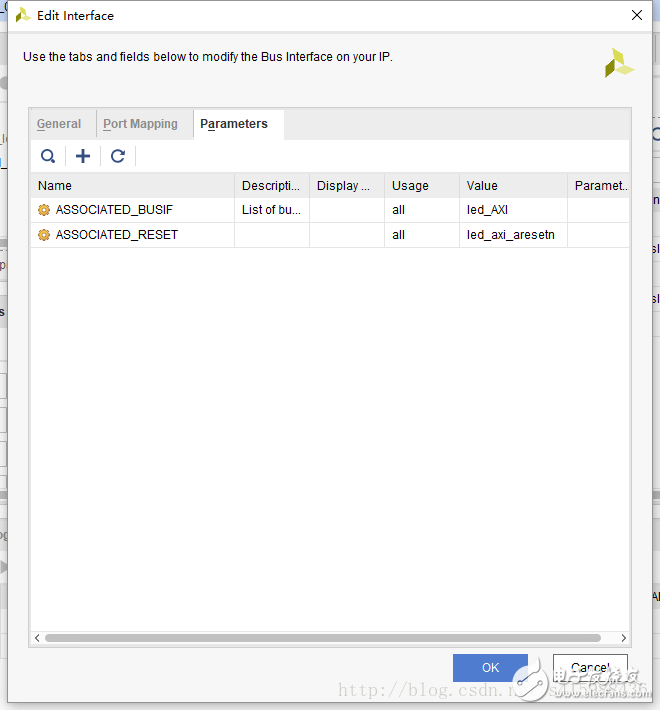

在Port and Interface 下可能会出现如下错误

[IP_Flow 19-3153] Bus Interface ‘_axi_aclk’: ASSOCIATED_BUSIF bus parameter is missing.

解决办法是找到对应的Interface然后右键选择Edit Interface会出现如下界面,然后根据下图所示,将ASSOCIATED_BUSIF 添加进去,然后修改value值就可以了。

7.最后点击Re-package IP, 就封装好了这个IP核

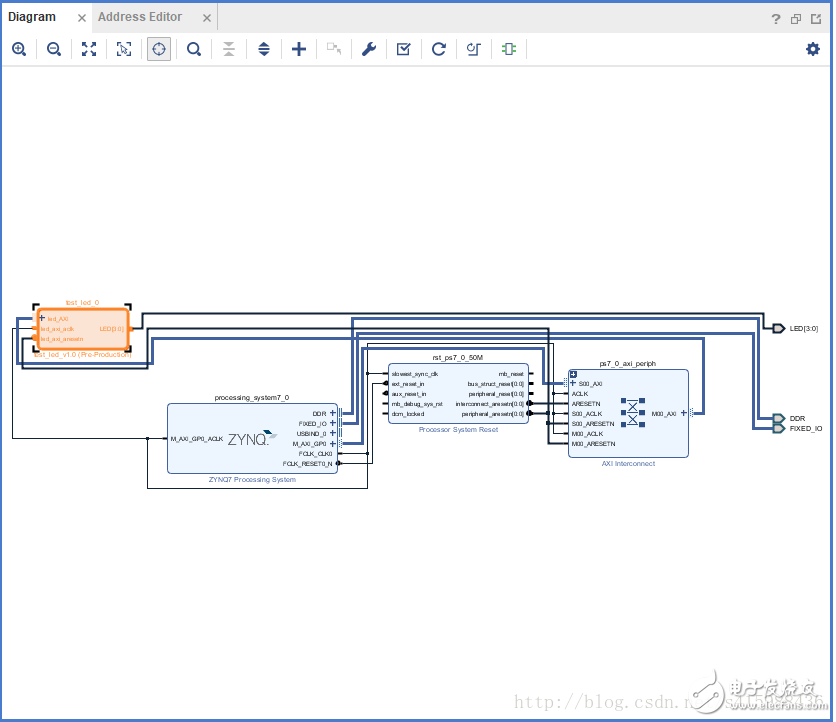

8.最后添加刚刚编辑好的IP核,使用自动连接将线练好,结果如下图所示。

3.老套路

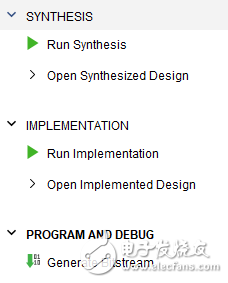

然后就又是老套路了,run 完下面几个步骤之后,export到hardware,然后将生成的bitstream写入到FPGA里,就完成的FPGA的这一部分。

2.SDK部分

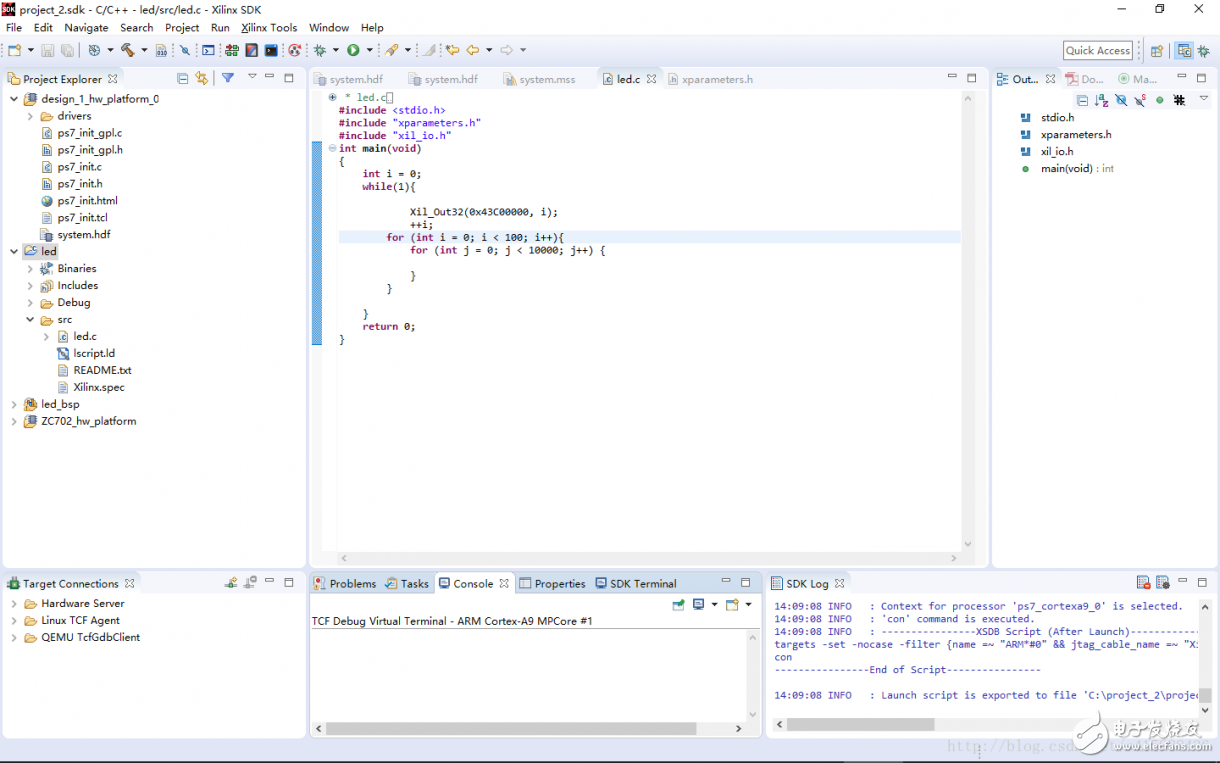

这部分就跟普通的单片机开发一样,唯一的不同就是需要将刚才生成的IP核的驱动文件的头文件添加到C里进行声明。

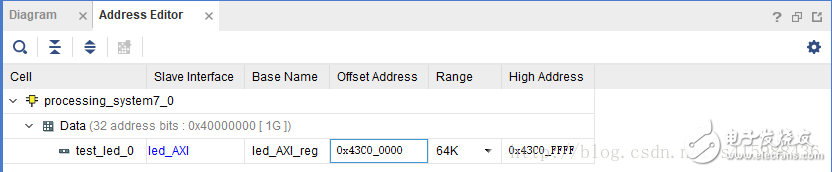

其中生成的头文件中会有基地址的常量声明。但是有时候会出现奇怪的BUG,这个时候就可以回到Vivado中寻找IP核的基地址。如下图所示。

最后烧写到arm中就可以看到效果了。

参考资料:xilinx大学计划

实验平台:PYNQ开发板

-

如何在Vivado中配置FIFO IP核2023-08-07 7722

-

一边学习控制FFT IP核,一边学习AXI4-Stream协议2023-06-19 3927

-

VCS独立仿真Vivado IP核的问题补充2023-06-06 3152

-

FPGA AXI4协议学习笔记(二)2023-05-24 3038

-

AXI总线协议简介2022-10-10 11470

-

AXI4-Stream Video 协议和AXI_VDMA的IP核介绍2022-07-03 10927

-

基于ARM的IEEE802-11bMAC层协议IP核设计2021-09-17 861

-

ARM+FPGA开发:基于AXI总线的GPIO IP创建2020-12-25 6997

-

自定义sobel滤波IP核,IP接口遵守AXI Stream协议2019-08-06 4793

-

AXI接口简介_AXI IP核的创建流程及读写逻辑分析2018-06-29 18000

-

vivado调用IP核详细介绍2018-05-28 38851

-

有人知道为什么MIG IP核中的AXI协议。为什么没有AXI_WID这个信号呢?2018-04-13 4868

-

vivado hls 写的IP核(某函数) 如何在 vivado 里面连接PS并且调用,最后把值放到内存里面?(使用AXI?)2016-01-28 3923

全部0条评论

快来发表一下你的评论吧 !