xilinx vivado zynq pldma设计及应用block design操作说明

FPGA/ASIC技术

描述

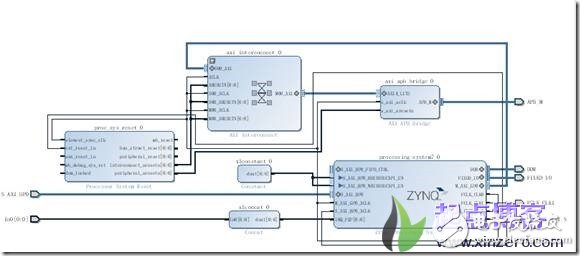

这个设计是根据avnet的PL dma带宽测试程序修改过来的,只使用了其中的HP0一个PLDMA。分为两个部分进行设计,第一部分是关于vivado中的block design部分,就是通过ip进行设计。第二部分是PLDMA的源码部分。

首先定制zynq核,ddr与uart的配置省略,前面已经写过很多。

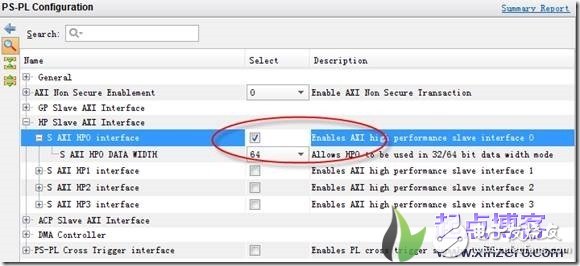

配置PL PS互连配置

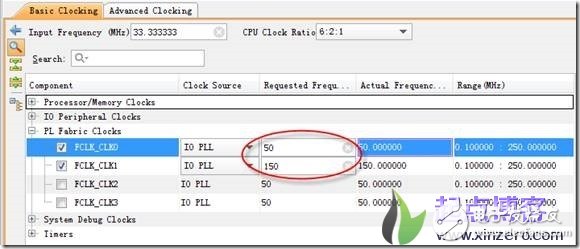

配置PL IO的工作时钟,FCLK_CLK0对应AXI APB总线工作时钟50Mhz;FCLK_CLK1对应HP接口工作时钟150Mhz。

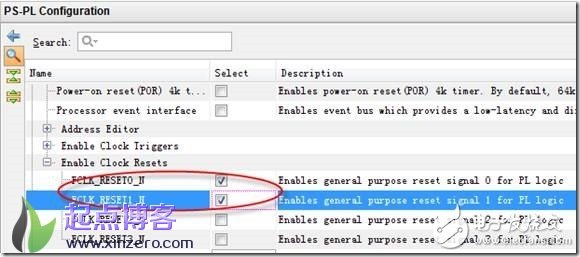

配置两个reset信号

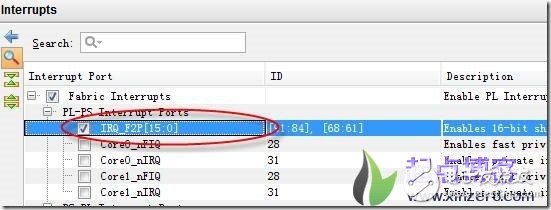

配置PL到PS的中断

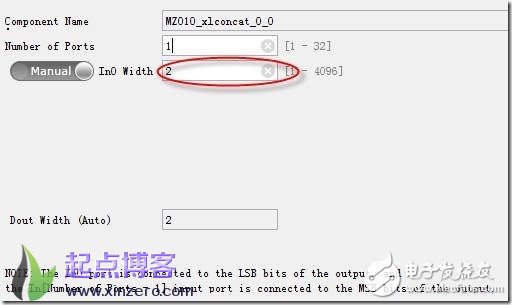

中断转换,将PS部分的中断信号转换后对外输出,需要使用concat ip。

设置concat的端口为1;

对应与DMA读与写中断信号各一个。

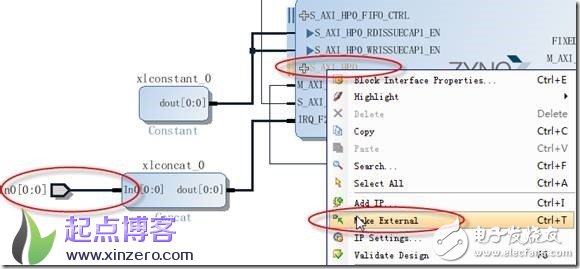

将“In0”、“S_AXI_HP0”端口,“Make External”

上图中的xlconcat_0实际为2个端口,截图时只配了一个端口。

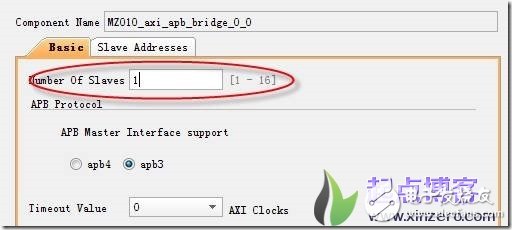

增加AXi apb bridge ip,使用axi到apb接口的转换。

默认为3个Slave接口,设置为1个端口。

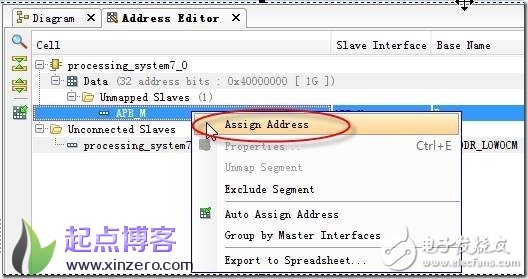

将APB_M接口“Make External”,然后在Address Editor中进行地址分配

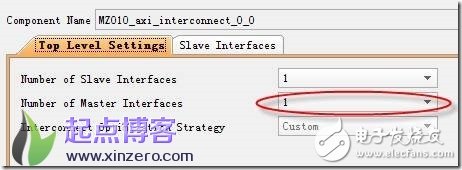

默认为2个Master接口,改为1个。

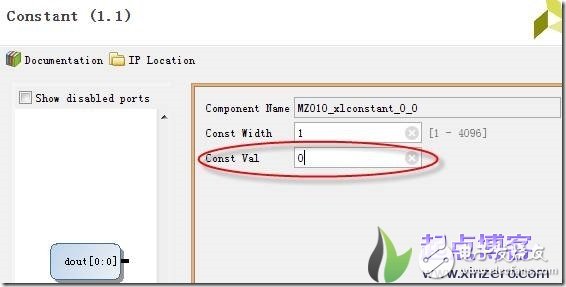

对HP0接口的控制信号配置为固定电平。

设置constant的宽度的值为1,常量的值为0。

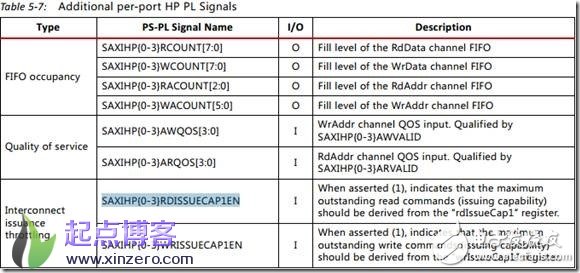

HP PL Signals描述

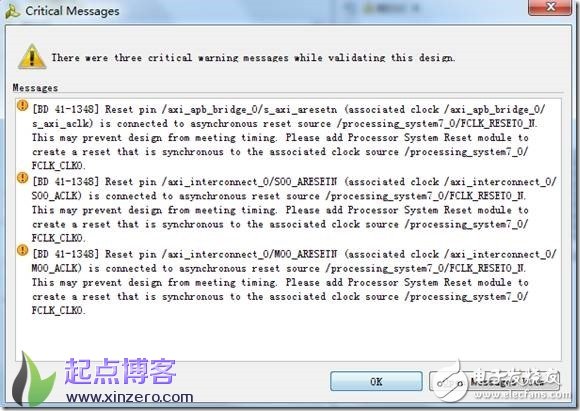

上面的严重警告信息,是因为没有增加“Process System Reset”IP,进行复位信号连接。

增加“Process System Reset”IP

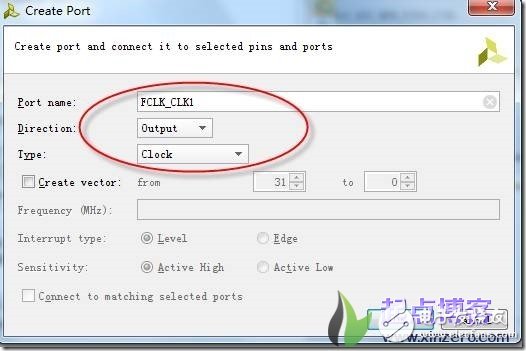

在FCLK_CLK1右键选择“Create Port”,创建为时钟接口,如下图所示

然后将FCLK_CLK1连接到FCLK_CLK1 port上。

增加后的设计布局

- 相关推荐

- 热点推荐

- Block

-

怎么在没有互联网且没有CD的工作站上安装Xilinx Vivado Design Suite2018-12-19 1810

-

在Vivado 2015.2块设计上打开子层次结构弹出一个新的Block Design窗口2018-12-25 3577

-

如何使用Vivado IP Block Design?2020-03-20 4701

-

Zynq7000的混合Verilog和块设计怎么做2020-05-19 2267

-

ZYNQ PS + PL异构多核案例开发手册之axi_timer_pwm_demo案例2021-05-28 2086

-

嵌入式硬件开发学习教程——Xilinx Vivado HLS案例 (流程说明)2021-11-11 3599

-

Vivado的helloword程序(一):硬件工程部分2017-02-07 1029

-

Vivado Design Suite 2014.4.1 现已推出!2017-02-09 516

-

xilinx vivado zynq pldma PL部分ILA调试2017-11-28 8771

-

Xilinx FSBL如何操作启动Zynq器件2018-11-23 5295

-

Xilinx_Vivado_zynq7000入门笔记2021-04-08 1549

-

Vivado BDC (Block Design Container)怎么用2021-11-09 6593

-

使用Vivado Block Design设计解决项目继承性问题2023-02-13 4727

-

Vivado Design Suite用户指南:版本说明、安装和许可2023-09-13 672

全部0条评论

快来发表一下你的评论吧 !