TLC2543特点、引脚功能与使用方法介绍

电子常识

描述

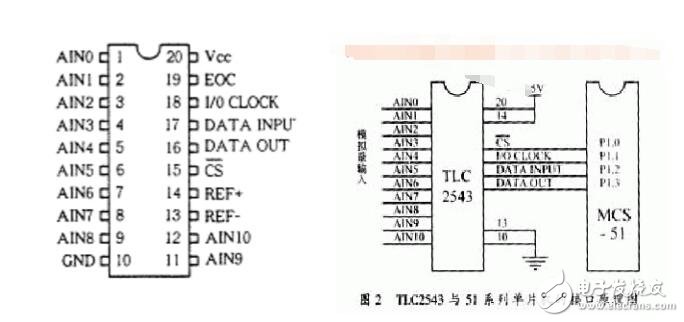

TLC2543是11个输入端的12位模数转换器,具有转换快、稳定性好、与微处理器接口简单、价格低等优点,应用前景好。由于它带有串行外设接口(SPI,Seri-alPeripheralInterface),而51系列单片机没有SPI,因此研究它与51单片机的接口就非常有意义。

TLC2543特点

(1)12位分辨率A/D转换器;

(2)在工作温度范围内10μs转换时间;

(3)11个模拟输入通道;

(4)3路内置自测试方式;

(5)采样率为66kbps;

(6)线性误差+1LSB(max)

(7)有转换结束(EOC)输出;

(8)具有单、双极性输出;

(9)可编程的MSB或LSB前导;

(10)可编程的输出数据长度。

TLC2543引脚功能

1~9、11、12——AIN0~AIN10为模拟输入端;

15——CS 为片选端;

17——DIN 为串行数据输入端;(控制字输入端,用于选择转换及输出数据格式)

16——DOUT为A/D转换结果的三态串行输出端;(A/D转换结果的输出端。)

19——EOC为转换结束端;

18——CLK为I/O时钟;(控制输入输出的时钟,由外部输入。)

14——REF+为正基准电压端;

13——REF-为负基准电压端;

20——VCC为电源;

10——GND为地。

TLC2543的简要工作过程

TLC2543的工作过程分为两个周期:I/O周期和转换周期。

a) I/O周期

I/O周期由外部提供的I/O CLOCK定义,延续8、12或16个时钟周期,决定于选定的输出数据长度。器件进入I/O周期后同时进行两种操作。

在I/O CLOCK的前8个脉冲的上升沿,以MSB前导方式从DATA INPUT端输入8位数据流到输入寄存器。其中前4位为模拟通道地址,控制14通道模拟多路器从11个模拟输入和三个内部测电压中选通一路送到采样保持电路,该电路从第4个I/O CLOCK脉冲的下降沿开始对所选信号进行采样,直到最后一个I/O CLOCK脉冲的下降沿。I/O周期的时钟脉冲个数与输出数据长度(位数)同时由输入数据的D3、D2位选择为8、12或16。当工作于12或16位时,在前8个时钟脉冲之后,DATA INPUT无效。

在DATA OUT端串行输出8、12或16位数据。当CS保持为低时,第一个数据出现在EOC的上升沿。若转换由CS控制,则第一个输出数据发生在CS的下降沿。这个数据串是前一次转换的结果,在第一个输出数据位之后的每个后续位均由后续的I/O时钟下降沿输出。

b) 转换周期

在I/O周期的最后一个I/O CLOCK下降沿之后,EOC变低,采样值保持不变,转换周期开始,片内转换器对采样值进行逐次逼近式A/D转换,其工作由与I/O CLOCK同步的内部时钟控制。转换完成后EOC变高,转换结果锁存在输出数据寄存器中,待下一个I/O周期输出。I/O周期和转换周期交替进行,从而可减小外部的数字噪声对转换精度的影响。

TLC2543的使用方法

3.1 控制字的格式

控制字为从DATAINPUT端串行输入的8位数据,它规定了TLC2543要转换的模拟量通道、转换后的输出数据长度、输出数据的格式。

高4位(D7~D4)决定通道号,对于0通道至10通道,该4位分别为0000~1010H,当为1011~1101时,用于对TLC2543的自检,分别测试(VREF++VREF-)/2、VREF-、VREF+的值,当为1110时,TLC2543进入休眠状态。低4位决定输出数据长度及格式,

D3、D2决定输出数据长度,01表示输出数据长度为8位,11表示输出数据长度为16位,其他为12位。

D1决定输出数据是高位先送出,还是低位先送出,为0表示高位先送出。 D0决定输出数据是单极性(二进制)还是双极性(2的补码),若为单极性,该位为0,反之为1。

3.2 转换过程

1)上电后,片选CS必须从高到低,才能开始一次工作周期,此时EOC为高,输入数据寄存器被置为0,输出数据寄存器的内容是随机的。

2)开始时,CS片选为高,I/O CLOCK、DATA INPUT被禁止,DATA OUT 呈高阻状,EOC为高。

3)使CS变低,I/OCLOCK、DATAINPUT使能,DATAOUT脱离高阻状态。12个时钟信号从I/OCLOCK端依次加入,随着时钟信号的加入,控制字从DATAINPUT一位一位地在时钟信号的上升沿时被送入TLC2543(高位先送入),同时上一周期转换的A/D数据,即输出数据寄存器中的数据从DATAOUT一位一位地移出(下降沿)。(在cs=0时输出第一位,其他的在下降沿输出)

- 相关推荐

- 热点推荐

- TLC2543

-

请问现在有能替代TLC2543的AD芯片吗?2024-12-13 605

-

使用GPIO实现基于MS51系列的TLC2543读写时间序列2023-08-23 460

-

TLC2543串行模数转换器参数资料推荐2021-05-21 1505

-

TLC2543的引脚功能与单片机的接口程序设计2020-07-02 9281

-

英创信息技术EM9280主板SPI访问TLC2543 AD示例2020-01-17 3299

-

tlc2543时序图介绍2017-11-21 5338

-

怎么检查TLC2543的好坏?2016-12-12 6290

-

tlc2543能不能采集交流信号2016-09-19 2682

-

tlc2543芯片使用手册2016-04-26 2001

-

单片机和TLC2543的仿真接口2015-04-05 2913

-

TLC2543测得的电压值跳动很大怎么解决2013-09-07 4633

-

12位A/D转换器TLC2543与51系列单片机接口技术2010-07-15 1374

-

介绍如何用TLC2543的串行接口和微处理器构建12位的数据2009-06-11 583

-

AD芯片TLC2543与Neuron芯片的接口应用2009-04-28 706

全部0条评论

快来发表一下你的评论吧 !