3G中软件无线电技术可行性及实现所面临的技术难题分析

RF/无线

描述

当前,蜂窝移动通信系统发展到第三代,3G系统进入商业运行一方面需要解决不同标准系统间的兼容性;另一方面为了适应技术的发展,3G系统要求具有高度的灵活性和扩展升级能力。软件无线电技术无疑是最好的解决方案。

作为3G移动通信标准中的两个主要标准,W-CDMA和CDMA2000都采用码分多址接入方式,且具有信道带宽宽、数据速率多样且支持高速率,不同业务采用信道编码不同等共性;同时,这两种标准之间在码片速率、信道带宽和信道选择码等方面也存在差异。这些方面以及为了提高系统容量在3G中将采用的智能天线技术(Smart Antenna)、多用户检测技术(MUD)等,使得软件无线电技术在3G系统中有着广泛的应用空间,同时也面临巨大的技术挑战。

以实现CDMA2000(含IS-95)和W-CDMA双模软件无线电系统为例,针对3G移动通信系统的具体情况,我们将分析3G中软件无线电技术的可行性及实现所面临的技术难题。讨论是在传统的流水线结构上进行的,首先讨论传统单用户接收机的软件无线电实现问题,然后讨论卷积码、Turbo码译码的软件实现,最后讨论智能天线技术和多用户检测技术在软件无线电实现中所面临的问题。

多种3G移动通信标准的加入使得本来已经十分庞大的移动通信标准族变得更加繁杂。从近期发展上看,软件无线电技术可以解决不同标准的兼容性,为实现全球漫游提供方便;从长远发展上看,软件无线电发展的目标是实现具有可以根据无线电环境变化而自适应地配置收/发信机的数据速率,调制、解调方式,信道编、译码方式,甚至调整信道频率、带宽以及无线接入方式的智能化无线通信系统,从而更加充分地利用频谱资源,在满足用户QoS要求的基础上使系统容量最大。当然,实现这一美好目标有待于理论与应用研究的进一步深入。

传统单用户接收方式的实现

这里的讨论仅限于下行链路接收过程中的A/D变换器和数字处理子系统。讨论是从实现各种无线电功能的计算复杂度这个角度进行的,而且仅讨论资源需求中的主要问题,包括成形滤波和RAKE接收等。

首先,标准为实现W-CDMA和CDMA2000双模无线电系统提供了基础。为了在移动电台中支持多种通信标准,从降低复杂度和造价等方面考虑,人们希望能用同一个主系统时钟为每种工作模式产生工作时钟,这个主时钟可以是每种模式的时钟频率的最小公倍数。CDMA2000 1X(1.2288M)和W-CDMA(3.84M)码片速率的最小公倍数是30.72MHz,CDMA20003X和W-CDMA码片速率的最小公倍数是92.16MHz。由于这个公倍数较小,可用其二倍频率184.32 MHz作为主系统时钟,CDMA2000(1X和3X)或W-CDMA各自的时钟均可由此主时钟导出。所以说W-CDMA和CDMA2000标准为W-CDMA/CDMA2000多模移动台的实现提供了方便。

其次,VLSI器件也为实现提供了有利条件。实现W-CDMA和CDMA2000双模系统对A/D变换器和可编程DSP处理器提出了要求。

(1)A/D变换器

A/D变换器的采样率选择为61.44MHz。选择的依据有两方面:首先是为了满足采样定理。无线频谱资源是十分有限的,这里假设分配给每个标准的频谱都是25MHz,采样定理要求采样率至少是信号带宽的2倍,实际中常取为信号带宽的2.5倍,61.44MHz的采样率基本满足要求。

其次61.44MHz采样率可由184.32 MHz的系统时钟3倍降采样直接得到。从最先进的A/D器件水平看,ADI公司的AD6644和AD9244在65MHz采样率时能提供14bit的精度。其中AD6644在Nyquist频带上可提供100dB的FSDR(无寄生动态范围指标),可满足要求。

(2)DDC器件

DDC器件可选择Intersil公司的HSP50214B-65。HSP50214B-65最高输入样本速率为65MHz,精度为16bit,并可以进行非整数倍的降采样。这样可以分别确定W-CDMA和CDMA2000的降采样倍数。为了使后续处理部分能更精确地实现码片同步,降低采样后的数据速率取为码片速率的4倍。于是得到W-CDMA的降采样速率为4,CDMA2000 3X降采样率为4.1667,CDMA2000 1X降采样率为12.5。降采样后的数据率分别为15.36MSPS(W-CDMA)、4.9152MSPS(CDMA2000 1X)和14.7456MSPS(CDMA2000 3X)。

(3)可编程DSP处理器

● 脉冲成型滤波处理计算量估计。脉冲成型滤波器也是按4采样速率进行的。3GPP2明确给出了成型滤波器长度(在四采样时,1X时的滤波器长度为48,3X时的滤波器长度为108)。3GPP协议中给出的成型滤波器是滚降因子为0.22的根平方升余弦滤波器,长度为25(单采样率)的根平方升余弦滤波器可以满足3GPP的要求。脉冲成型滤波器收发都要用到,而且是I、Q两路,所以总的计算量仍然很大,对DSP处理能力要求很高,但是用FPGA实现比较方便。

● RAKE接收中的运算量估计。当完成精确的码片同步后,脉冲成型滤波器输出数据速率可以降为码片速率,此后的计算都是在码片速率基础上进行的。RAKE完成解扩、解扰和多径合并等处理。而解扰、解扩后的数据率与扩谱因子有关,对W-CDMA,扩谱因子取值范围是4~512,所对应的数据率为960~7.5 kSPS,因此,最大比合并的计算量为K×0.03~K×3.84MIPS。CDMA2000可以得到相似结果。

发射过程的计算复杂度一般要小于接收过程的计算复杂度,所以,总的复杂度一般不会超出接收处理复杂度的两倍。但是,应该说明的是上面的讨论主要考虑的是数字处理部分中对总计算量起决定作用的功能模块,而没有考虑信源编码及协议实现等所需要的处理量。目前最先进的DSP器件TMS320C6416的处理能力已经达到5.76GIPS。实现上述处理的要求可用两片TMS320C6416芯片或者用FPGA来实现成型滤波器,用一片TMS320C6416来实现其余处理。

信道译码器的实现

CDMA2000和W-CDMA的信道编码方案中都包括卷积码和Turbo码两种方式。卷积码采用Viterbi算法实现译码;Turbo码译码器可以采用MAP算法和SOVA算法通过迭代实现,由于MAP算法十分复杂,实际中采用的是降低复杂度的LOG-MAP算法、MAX-LOG-MAP算法或SOVA算法。

Turbo码译码器的计算复杂度与采用的算法、编码器的约束长度和实现的迭代次数有关。各种算法中MAP算法复杂度最高,LOG-MAP算法次之,而SOVA算法复杂度最低。与这些算法复杂度依次降低相对应的是算法的精度相应地也降低了。在CDMA2000和WCDMA标准中,Turbo码主要用于高速数据业务和高QoS要求的业务。估计中假设DSP芯片中乘、比较和查表等是在单指令下实现的。这种假设对于内部提供Viterbi算法支持的DSP芯片是成立的,如TMS320C54X信片等。当迭代次数N为6时,完全满足CDMA2000标准中各种速率要求的Turbo码译码器需要的运算量为2.7GIPS。

所以,在可编程DSP上用软件实现Turbo码的译码算法对DSP提出了很高的要求。一种可行的方案是用DSP+灵活的硬件译码器方法实现,DSP对硬件译码器进行配置,然后具体的译码算法在硬件中实现,解决了灵活性与处理要求高的矛盾。庆幸的是,在部分高级DSP芯片,如TMS320C6416中,针对3G移动通信标准中的信道编码要求嵌入了高性能的Viterbi译码器和Turbo码译码器。这些协处理器能完全满足CDMA2000和W-CDMA标准中不同信道的译码要求,它们与DSP核心处理器并行工作,通过高性能DMA完成与DSP的数据交换。

智能天线的实现

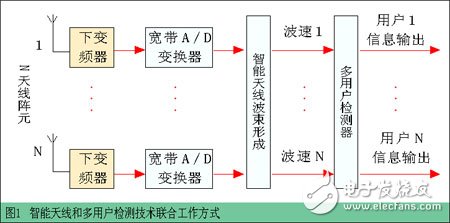

CDMA系统是干扰受限系统,多址干扰(包括同小区内用户和其他小区用户的干扰两部分)和多径干扰大大降低了CDMA系统的容量和覆盖范围。智能天线和多用户检测技术是降低多址干扰的两种关键技术。图1中给出了智能天线和多用户检测技术联合的一种方式。

智能天线利用信号传输的空间特性,

自适应地调整天线方向,在跟踪有用信号的同时减少或抵消干扰,增加信号干扰噪声比,增加系统容量,提高通信频谱利用率,降低信号发射功率,提高通信系统覆盖范围。智能天线波束形成算法可分为基于训练序列的算法和盲算法两大类,这些算法性能通常与通信系统的多址方式有关,如对于3G标准来说,MDIR算法是优选方案。因此,在用软件无线电实现的可以支持不同频段、不同多址方式的通信系统中,智能天线处理的体系结构与算法应当实时地与系统具体采用的标准保持一致。

智能天线处理包括调整天线阵元权系数和利用给定的权系数对输入信号实时处理两方面的计算。不同的智能天线算法复杂度不同,同一算法在系统中天线阵元数不同时复杂度也不同。对于基于训练序列的智能天线算法,很多技术文献中给出了采用LSM、RLS、FTF和LSL等自适应算法调整天线阵元权矢量的计算复杂度。相关文献给出了适用于3G标准的MDIR算法的复杂度。结果表明,当基站的智能天线由4个阵元组成时,每个用户的波束形成需要用一片浮点C67X DSP处理器。可见,对于同时要处理多个用户信息的基站来说,实现MDIR智能天线算法难度较大。

相关文献给出了一种次最优的、低运算复杂度的盲智能天线算法,适用于采用CDMA多址方式的移动通信系统。特点是采用时-空处理结构在解扩之后的基带进行天线波束形成运算,调整天线权系数和实现阵列处理输出都以信息符号的速率进行。而基站中采用此低复杂度智能天线算法的可行性很大。

多用户检测的实现

多用户检测技术通过信号处理手段来降低多址干扰、多径干扰和远近效应的影响,从而增加系统容量和覆盖范围。多用户检测器可分为最优的多用户检测器(MLSD检测器)和次优型多用户检测器,而次优型多用户检测器又可分为线性多用户检测器和非线性多用户检测器。MLSD检测器的复杂度为高。有关文献中给出了部分降低复杂度的次优型多用户检测器的复杂度。复杂度过高是制约所有多用户检测方法使用的决定因素。例如,实现最优多用户检测器需要几十至几百TFLOPS,采用多级硬判决反馈算法的多用户检测方法需要至少7GFLOPS(或30GOPS)的处理量才能满足WCDMA的要求。用当前最先进的定点DSP芯片TMS320C6416来实现3G系统的多用户检测器,需要至少7~8片并行处理才能实现。对于不受体积、功耗等因素制约的基站来说,采用当前最先进的微处理器技术已经可以实现软件无线电多用户检测器。

当前的软件无线电多用户检测器研究尚处于功能实现阶段,通常采用全DSP结构或DSP加FPGA的混合结构来实现。在采用DSP和FPGA混合结构实现的软件无线电多用户检测器中,用FPGA实现算法中计算量大、实时性要求高的部分,而DSP实现算法中结构复杂的部分,如矩阵求逆等。已有相关文献报道,采用改进的匹配滤波器方式实现了匹配滤波MF接收机、近似解相关检测器AD、严格解相关检测器DC、最小均平方误差解相关器MMSE、连续干扰对消检测器SIC、并行干扰对消检测器PIC等多用户检测算法。可根据业务QoS的不同要求,采用不同的多用户检测方法。全DSP结构的软件无线电多用户检测器灵活性更高。而采用4片RISC处理器PowerPC G4实现的基于判决反馈算法多级干扰对消的多用户检测器,可同时支持128个实时的、同时通话的话音用户。

典型软件无线电体系结构

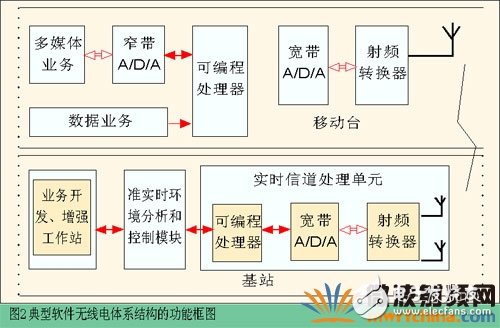

典型的软件无线电系统包括实时信道处理部分、准实时的环境管理部分以及用于开发增强业务的在线和脱机软件等,图2给出了典型软件无线电体系结构的功能框图。软件无线电实现方式多样,既可以利用ADC、FPGA、DSP和通用CPU形成具有SIMO和MIMO混合结构的流水线方式来实现,也可以在通用的PC机和工作站上实现,甚至可以通过高速网络利用网络资源实现。

-

软件无线电的主要原理及技术2023-09-22 1149

-

软件无线电技术中的关键技术——软件无线电的架构2021-04-08 6594

-

软件无线电技术在3G和4G中有什么样的应用2020-10-29 1077

-

软件无线电技术对3G与4G通信系统有什么样的作用2020-09-01 1370

-

卫星无线电频率使用可行性论证办法详细解读2020-01-14 1277

-

智能天线技术在软件无线电中的应用2019-07-29 2450

-

软件无线电技术的发展前景2019-07-26 1827

-

采用射频天线实现软件无线电技术2019-07-11 2459

-

软件无线电助力3G通信发展2019-05-28 2344

-

软件无线电、无线电的技术概述及应用2018-08-21 4399

-

3G和4G使用软件无线电技术优化性能2017-11-21 1222

-

多载波3G收发机的可行性2010-12-07 1237

-

认知无线电技术实现和挑战2010-04-24 3063

全部0条评论

快来发表一下你的评论吧 !