Xilinx DDR2 IP 核控制器设计方案介绍与实现

FPGA/ASIC技术

描述

提出一种便于用户操作并能快速运用到产品的DDR2控制器IP核的FPGA实现,使用户不需要了解DDR2的原理和操作方式的情况下,依然可以通过IP核控制DDR2。简单介绍了DDR2的特点和操作原理,并对DDR2控制器的IP核进行了模块化的划分,分析了每个模块的功能。强调了用户接口功能的完善,并介绍了IP核的操作流程,使每个用户都能轻松的使用该IP核。

1 引言

DDR2作为主流的内存具有存取速度快、存储量大、成本较低等特点,因此被广泛地运用到计算机、汽车导航系统、高清数字电视、数码相机等电子行业的各大领域当中。随着科技的发展,FPGA的技术也在不断进步,FPGA的性能、稳定性、容量等指标已经有了很大的提高。鉴于FPGA的发展和DDR2高性能的表现,越来越多的研发人员会通过FPGA直接对DDR2进行控制,这时他们必须对DDR2的工作原理有深入的了解,但这样就很可能加大了研发周期,直接影响了公司的经济效益。因此设计一款开发人员完全不需要了解DDR2工作原理的DDR2控制器IP核是非常具有实际意义的。

本文提出了一款方便用户使用的DDR2控制器方案。用户不需要了解DDR2的工作原理,只用控制有限的几个用户接口就可以对DDR2进行操作,在产品开发时可以大大缩短开发周期。

2 DDR2的特点

DDR2是基于JEDEC(Joint Electronic Device Engineering Council)标准的外部存储设备,并且DDR2还有着低功耗,高密度和高频率等特点。与DDR相比DDR2具有如下特点:

1)相同的核心的频率的情况下,DDR2的工作频率是DDR的两倍。

2)ODT(on.Die Termination)片内终结器:为了防止信号反射问题,DDR2中集成了ODT。ODT能够吸收线路终端的信号的影响,而且能使得信号质量更高和数据传输更快。

3)OCD(Off-Chip Driver)离线驱动调整:通过调整输出驱动的上拉/下拉电阻值,使得充、放电动作的电压误差减到最小,调整DQS和DQS#的波形交叉点,平衡参考时钟的上升沿和下降沿波形,从而保证内部输出驱动的稳定。

4)前置CAS(Posted Column Address Strobe)前置列地址选通:通过将CAS信号插到RAS(Row Address Strobe)信号的后一个时钟周期,避免命令和CAS信号的冲突,提高命令总线和数据总线的速度。

3 DDR2的操作原理

对DDR2的操作是一个复杂又繁琐的过程,它的主要操作如下:

1)初始化:DDR2的工作方式是由内部和外部寄存器所控制的,因此在上电时先需要对DDR2的寄存器进行配置,即初始化。通过初始化可以对DLL,Burst Length(突发长度),Burst type(突发类型),CAS Latency(CAS延时),CL latency(CL延时),ODT,OCD,等的配置。

2)行激活和列选址:在DDR2内部存储就好是被分成几个表格一样,L-BANK表示有几张表格,而在每一张表格中首先确定它的行,再确定列来选取所存放的地方。根据DDR2的特征,对DDR2的地址选择分为两步:第一步行激活:片选CS#拉低,通过BAO、BA1(BA2)来选择L-BANK,把行选通RAS#拉低,通过地址线输入行地址。第二步列选通:在行激活的下个周期,列选通CAS#拉低,通过地址线输入列地址。如果是在同一行进行操作时,就可以省略行激活。

3)读/写指令的发布:当列选址完成后,经过AL的延时就可以发出读/写命令对DDR2进行操作了,再经过CL个周期(从读操作的命令发出到第一个数据的延时)的延时第一

个读数据输出或者是经过CL-1个周期(写操作命令的延时比读操作命令的延时少一个周期)的延时输入第一个数据。

4)预充电(Precharge):DDR2为动态储存体,它的储存体上的电容电压会因为时间或干扰的情况下使电压值变化,从而使数据产生变化。在对另一行进行操作时必须关闭原来的行,重新发送行/列地址,这时会对DDR2产生干扰,因此在重新换行时要对其电容进行有选择的充电操作即进行预充电。

5)刷新(refresh):DDR2的储存体是体积极小的电容,由于漏电的存在,电容中的电量会不断的减小,而储存体是根据电容电量的多少来判断数据是1或者是0的,为了保证数据的可靠性,就需要定时对存储体上的电容进行有选择的充电,即刷新。

4 DDR2控制器IP核的架构思想

一方面DDR2具有动态存储的特点,它需要在一定的时间和特殊的情况下进行充电,因此在数据传输的时候不能进行不间断传输,而要对传输的数据量进行有效的实时控制。另一方面DDR2又具有高速的特点,在DDR2数据传输方面频率很高,而在FPGA内部的控制方面又不需要达到这么高的频率,因此在FPGA的内部就形成一个跨频域的操作形式。基于上述两方面的原因,在DDR2控制器的IP核上采用控制模块和数据模块分离的方式,再用时钟模块为两个模块输入时钟,最后加了用户接口使用户可以快速和方便的使用IP核。

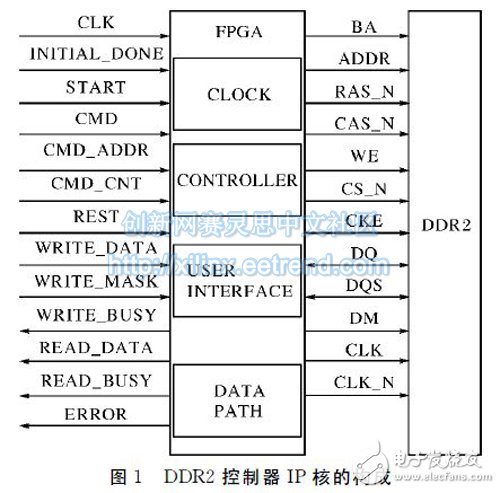

5 DDR2控制器IP核中各模块的功能

DDR2控制器是有四个模块组成:时钟模块,控制模块,数据链路模块,用户接口模块。

5.1 时钟模块

时钟模块是由Xilinx的DCM 核构成,主要用来接收FPGA外部时钟,然后通过分频和倍频产生用户接口时钟、数据链路模块使用的时钟、控制模块使用的时钟和DDR2的时钟。它还有一个作用就是用复位信号对整个IP核进行全局复位。

5.2 控制模块

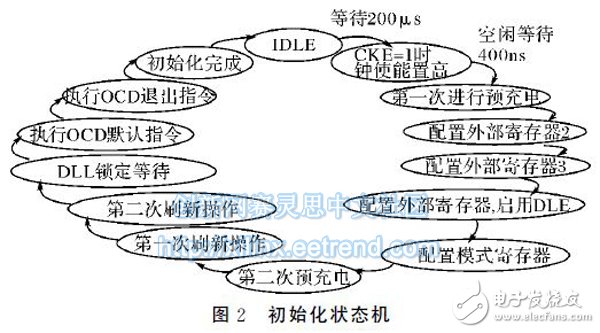

控制模块作为控制器的中枢,它主要负责对DDR2的初始化和命令的操作,因此控制模块基本上是由初始化和命令控制两部分组成。

初始化:在DDR2上电后经过20μs的稳定期,我们把时钟使能信号CKE置高,等待400ns的时间后进行第一次的预充电,然后对外部寄存器和模式寄存器进行配置,紧接着执行第二次预充电和两次刷新,再判断DLL是否正确锁定,配置OCD,最后等待初始化完成。如果初始化结束,我们就把信号initial_done置高表示初始化完成用户可以对DDR2进行操作了。

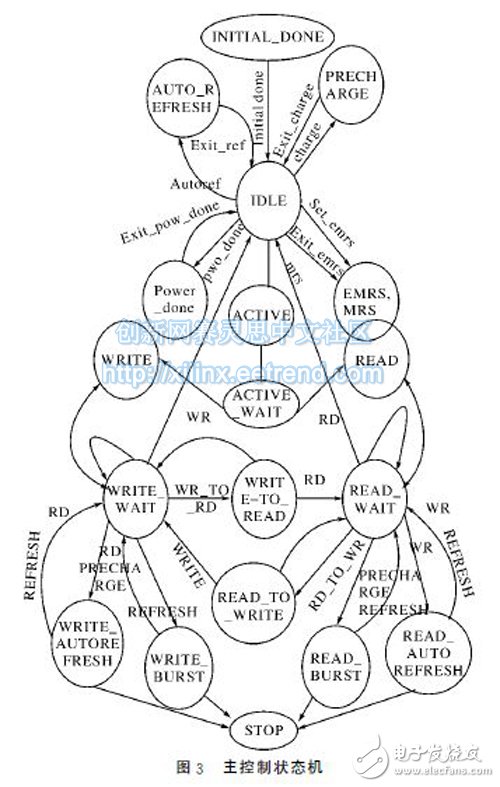

命令控制:命令控制部分主要用作DDR2初始化后,产生控制信号和每个操作中的延时,并分析用户命令对DDR2进行自动刷新、读操作、写操作、预充电等操作。当用户写入读写命令的时候,状态机(图3)可以自动的进行判断初始化是否完成、行激活、列寻址、预充电、自动刷新、读写命令发布等操作。

5.3 读/写数据链路模块

DDR2是一个高速的,并且是时钟上、下沿都采样数据的芯片,因此对于数据链路模块的时序要求非常严格。为了能够严格控制时序问题,采用了Xilinx的SPARTAN6的特殊原语模块IIDDR和ODDR对数据进行处理。在数据链路模块中采用读数据链路和写数据的链路独立的方式,这样使读/写数据完全独立,使用户更容易对数据进行控制。

5.4 用户接口模块

用户接口模块作为和用户直接连接的模块,它功能的强大与否直接影响用户对IP核控制的难易度。为了使用户很容易把控制器的IP核运用到工程项目中,整个模块中包含了READ

FIFO、WRITE FIFO、COMMAND FIFO、命令子模块、用户数据链路子模块,用户控制模块子模块。READ FIFO、WRITE FIFO、 COMMAND FIFO 使用户可以的控制命令和数据连续的输入和输出。命令子模块可以翻译用户输入的命令,用户只需要发送读或写命令、命令要操作的首地址和总共读/写多少个数据,命令子模块就可以根据情况发送命令控制给用户控制子模块。用户控制子模块再以状态机的形式控制COMMAND FIFO、WRITE FIFO、READ FIFO对与用户接口模块相连的主控制模块和数据链路模块进行控制,对DDR2进行读/写等操作。

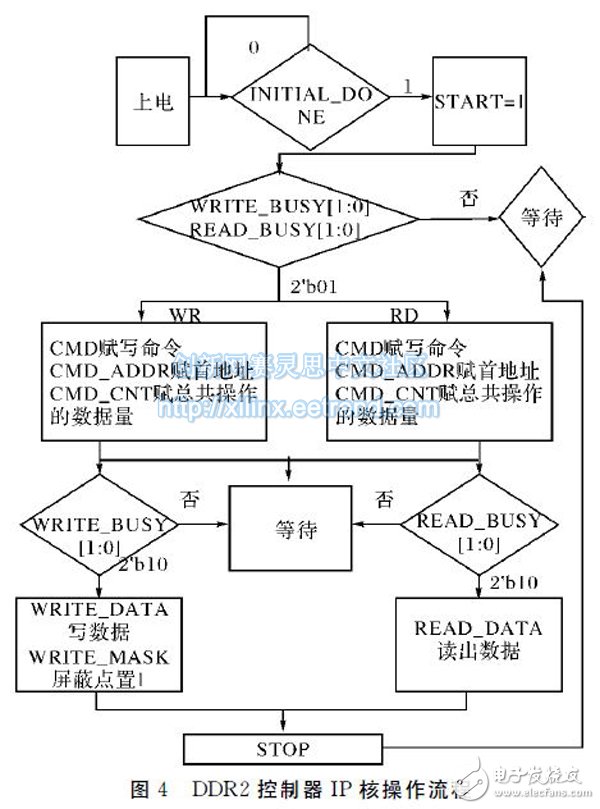

6 如何控制IP核对DDR2进行操作

这个设计的DDR2控制器IP核不需要用户了解DDR2的工作特性就能很好的操作IP核对DDR2进行读写等操作,如图4所示。

1)首先通过INITIAL_DONE初始化完成信号判断DDR2是否初始化完成,初始化完成INITIAL_DONE置1,否则为0。

2)开始操作时把开始信号START置1,通过WRITE_BUSY和READ_BUSY信号来判断是否可进行命令的发送。WRITE_BUSY信号为2位宽,WRITE_BUSY[1]表示命令信号,为1时表示忙,0时表示不忙可以发送命令。WRITE_BUSY[0]表示数据信号,为1时表示忙不能发送数据,0时可以发送数据。READ_BUSY信号与WRITE_BUSY信号有着相同的功能,并且只有在READ_BUSY[1]和WRITE_BUSY[1]信号都为0时才能发送命令,也就是命令不能同时进行。当WRITE_BUSY=01和READ_BUSY=01时,CMD=000为写操作。

3)当WRITE_BUSY[1:0]信号为10时可以在时钟的上升沿时对WRITE_DATA输入数据,并且可以通过对WRITE_MASK相应的位赋1来屏蔽不想要的数据或者是避免当数据不够而写入0的情况。

4)当写入结束时WRITE_BUSY=01时可以把START信号置0,结束写入。

7 结语

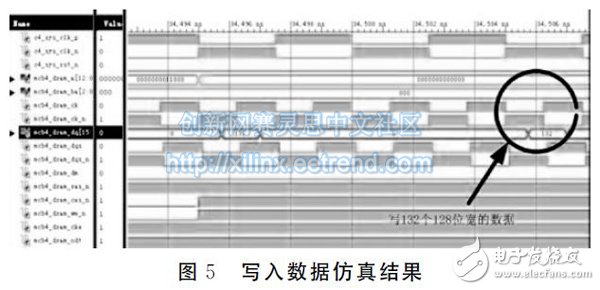

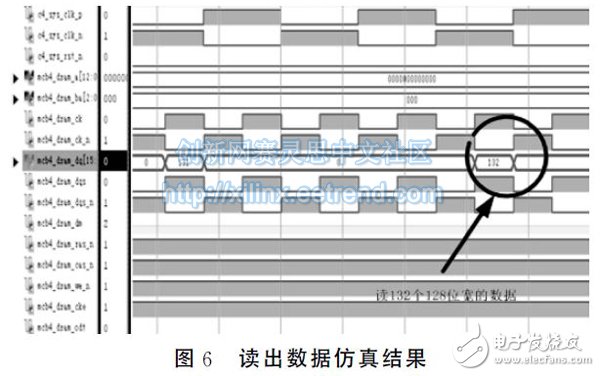

为了验证此DDR2控制器IP核的实用性,我们通过Xilinx公司的xc6slx45t器件以及美光的MT47H12816XX-3DDR2模型做了仿真,并在Xilinx的sp601开发板进行了实验。通过测试代码往DDR2中写入132个128位的数据(如图5),并从DDR2中读取写入的数据(如图6)。通过实验证明了即使用户不很清楚DDR2的工作原理,也可以很方便的通过本文设计的DDR2控制器IP核对DDR2进行读写操作。

-

用FPGA实现DDR控制模块介绍2025-10-21 190

-

如何根据Xilinx官方提供的技术参数来实现对IP核的读写控制2022-02-08 850

-

DDR3 SDRAM控制器IP核的写命令和写数据间关系讲解2020-12-31 6736

-

Xilinx DDR控制器MIG IP核的例化及仿真2020-11-26 10380

-

基于FPGA的数据采集控制器IP核的设计方案和实现方法研究2019-07-09 2904

-

TMS320DM646x数字媒体系统DMSoC的DDR2存储控制器详细介绍2018-04-18 1322

-

IP 核配置——DDR2 控制器 求助2018-01-24 4431

-

DDR2 ip核创建时,器件选型的问题2017-09-19 2948

-

例说FPGA连载41:DDR控制器集成与读写测试之DDR2 IP核接口描述2016-10-27 6742

-

Xilinx DDR2存储器接口调试代码2016-06-07 849

-

带自测功能的DDR2控制器设计2016-01-04 626

-

基于SPARTAN6的DDR2的IP核的研究(转)2015-03-16 4693

-

FPGA引脚分配问题(DDR2控制器)2012-06-19 4846

-

DDR2 SDRAM控制器的设计与实现2010-02-09 826

全部0条评论

快来发表一下你的评论吧 !