基于FPGA的实时视频处理平台方案讨论及设计

FPGA/ASIC技术

描述

为了能够实时地采集、处理、显示视频,设计并实现了一种基于双PowerPC硬核架构的实时视频处理平台;用硬件实现视频的预处理算法,并以用户IP核的形式添加到硬件系统中,上层的视频处理软件程序则直接从存储器中调用预处理后的图像数据;重点介绍了在FPGA上构建双PowerPC硬核架构的硬件系统;采用乒乓控制算法缓存一行图像数据;用DMA的方式将图像数据保存在存储器中;以边缘检测作为视频预处理算法的一个实例,在平台上实现,实验结果表明,用本平台实现仅需40ms;本平台能够实时处理视频,具有较高的实用价值。

0 引言

目前,视频处理平台大多使用DSP芯片进行图像处理。实时视频处理对系统性能提出了极高的要求,几乎最简单的功能也超出了单个通用DSP芯片的处理能力。一旦达到极限,通常只有增加额外的DSP芯片。2010年郭春辉提出一种基于多条带、多DSP的并行视频处理系统[1]。这种采用多处理器并行处理的方法虽然提高了处理速度,但增加了系统开发的复杂度,例如任务的合理分配,多处理器之间的通信、互斥等。当然,也增加了系统的功耗。DSP在性能方面的局限导致开发更为专用的芯片,如多媒体处理器,来克服这些问题。然而,事实证明这些器件除了在范围极窄的一些应用中,都有不灵活的缺点,同时还存在性能瓶颈。基于处理器的方案,其局限在高分辨率视频处理系统,如HDTV和医疗图像系统中特别明显。基本上,这种方案受限于多少个周期可以完成一次加法和乘法运算。

采用FPGA进行视频处理使设计人员可以利用并行处理技术实现视频信号处理算法。设计人员还可以在设计面积和速度之间进行折衷,并且可以用比DSP低得多的时钟频率完成给定的功能。更重要的是它的灵活性,能满足固件升级及以后多媒体标准改进的要求。因此,本文提出一种基于FPGA 可重构的软硬件协同设计的实时视频处理平台。平台使用常规的FPGA开发工具,提供一个适应强、模块化的架构,同时满足高性能、低功耗的要求。

1 总体设计

视频是一种连续变化的图像信息。一般地,视频处理大致可以分为底层处理(即预处理)和上层处理:底层处理的数据量大,算法实现比较简单,且存在较大的并行性;上层处理的算法复杂,而数据量小。对于视频处理的实现手段,在视频的预处理阶段,采用软件实现是一个很耗时的过程,但采用硬件实现就可以对大量的视频数据进行并行处理,能够极大地提高视频处理的速度;而在视频上层处理阶段,采用软件实现则具有较高的性价比。

例如,Visicom公司发现对于中值滤波,DSP需要67个周期完成该算法。采用FPGA只需要运行在25MHz的时钟频率,因为FPGA可并行实现该功能。而DSP要达到同样的性能则需要运行在超过1.5GHz的时钟频率。在这一特定的应用中,FPGA的方案比一个100MHz时钟频率的DSP的要强大约17倍[2]。

范围广泛的实时图像和视频预处理功能都适合采用FPGA硬件实现,它们包括实时:边缘检测、缩放、色彩和色差校正、阴影增强、图像放置、直方图功能、锐化、中值过滤、模糊分析等。

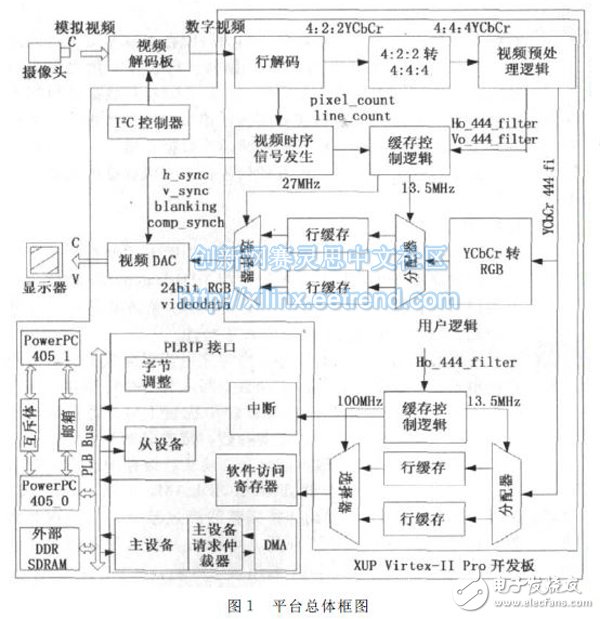

本设计的实时视频处理平台采用Xilinx公司大学计划XUP Virtex-II Pro 开发板。它包括一个Virtex-II Pro XC2VP30FPGA,其内部有30816个逻辑单元,136个18位乘法器,2448kB块RAM,两个PowerPC 405处理器。还包括一根DDR SDRAM DIMM 插槽,可以支持高达2Gbytes的RAM,若干扩展接口和一个XSGA视频接口。外接一块视频解码板(支持ITU-R BT.656视频标准),该开发板就能完成视频的采集、处理和显示。实时视频处理平台总体框图如图1所示。

视频采集部分包括行解码、4:2:2转4:4:4、行缓存和缓存控制逻辑模块、分配器、选择器模块等。测试部分包括YCbCr转RGB、视频时序信号发生模块等。这两部分是Xilinx公司提供的验证设计,故本文只对其做简单介绍。预处理部分包括视频预处理逻辑模块,下文将重点介绍该模块。这三部分构成用户逻辑。用户逻辑和PLB IP接口构成一个完整的基于PLB总线的用户IP核,可以方便地将其添加到视频处理平台的硬件系统中。

对于视频信号源,可以是有线电视、DVD、VCR、CCD等。在对模拟视频信号进行数字化处理时,先通过视频解码板把它转换成符合ITU-R BT.656标准的数字视频流。在FPGA芯片内,对该数字视频流进行采集及预处理。经处理后的视频流,一方面通过YCbCr转RGB模块、行缓存、及视频DAC转换成RGB信号,供显示器显示,作为测试用;另一方面,该视频流还以DMA 的方式通过PLB总线保存到片外的DDR SDRAM 中。这样,在PowerPC处理器上运行的应用程序就可以直接从DDR SDRAM 中调用已经过视频预处理模块处理的视频数据,完成上层的视频处理算法。

1.1 双PowerPC硬核结构

IBM PowerPC 405处理器核是32位的RISC CPU 硬核,它嵌入到FPGA内用于实现高性能嵌入式应用。它包括标量5级流水线、独立指令和数据缓存、1 个JTAG 端口、迹线FIFO (trace FIFO)、多个定时器和1个内存管理单元。它最高可以工作在300MHz频率下,具有600+DMIPS的运行速度。

使用Xilinx公司提供的嵌入式开发套件EDK,在FPGA上构建视频处理平台的硬件系统,包括双PowePC处理器、PLB总线、DDR SDRAM 存储器、互斥体、邮箱、用户IP核(包括视频预处理逻辑模块)和其它外设。

实现PowerPC双核架构的难点是数据的并行处理和共享存储器的访问竞争。因此,在硬件系统中添加互斥体,它包括数量可配置的互斥信号量,每个互斥信号量包括一个32bit用户配置寄存器(存储专用数据),用来解决多核环境下访问共享存储器。在多核环境下,一个处理器可以用邮箱与另一个处理器通信,这样就能实现视频处理算法的并行执行。

1.2 行解码模块

经视频解码板转换后的数字视频流,符合ITU-RBT.656标准,通过9根信号线(1根27MHz时钟线LLC_CLOCK和8根YCbCr视频数据线)接入FPGA。行解码模块完成从数字视频流中提取所需的视频信息,包括场标识位F (处于奇场或偶场)、场状态标识位V(处于场正程阶段或场消隐阶段)、行状态标识位H (有效视频起始信号或有效视频结束信号),以及YCbCr视频数据。视频数据是以27M 字/秒的速率传输的,其顺序是:Cb0,Y0,Cr0,Y1,Cb2,Y2,Cr2,…… 其中,Cb0,Y0,Cr0这3个字指的是同一像素的亮度和色差信号采样,后面的Y1对应于下一个像素的亮度采样。

1.3 4:2:2转4:4:4模块

为了数据传输和存储的需要,ITU-R BT.656标准采用YCbCr4:2:2采样格式,就是每采样4个亮度信号,只采样2对色差信号,因此在对视频数据进行处理之前,必须重建YCbCr4:2:2采样中丢失的Cb、Cr色差信号。在该模块中,采用复制前一像素的Cb、Cr色差信号的方法,把YCbCr4:2:2采样格式的视频流转换成YCbCr4:4:4采样格式的视频流。因此,模块输出的数字视频流的频率为输入Y信号的频率,即像素时钟频率,等于13.5MHz。

1.4 视频预处理逻辑模块

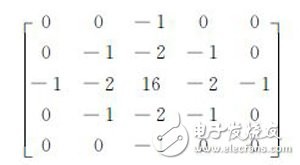

边缘检测是图像处理中的重要内容。边缘在边界检测、图像分割、模式识别、机器视觉等中有很重要的作用。因此,本设计以边缘检测作为视频预处理算法的一个实例。在边缘检测算法中,采用LOG算子,它通过求二阶导数中的零交叉点来检测边缘,检测出的边缘宽度较细,有利于边缘的精确定位。LOG算子使用的5×5模板为:

当然,工程师可以根据不同的需要,在该模块中用硬件逻辑实现不同的视频预处理算法,例如:缩放、色彩和色差校正、中值过滤等。

1.5 YCbCr转RGB模块

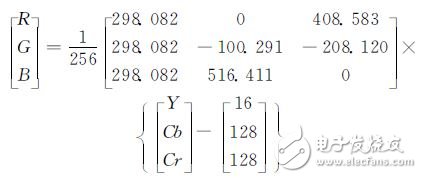

YCbCr和RGB是视频图像中常用的两种色彩空间,用YCbCr色彩空间表示颜色易于实现压缩和方便传输,但现有显示设备大多采用RGB信号驱动,因此,对于视频的显示,需要将YCbCr信号转换为RGB信号。YCbCr转RGB的公式:

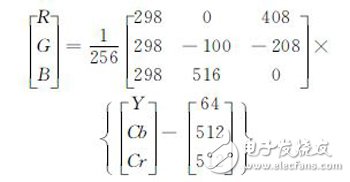

式中,Y、Cb、Cr 信号值的范围是16~235,均为8比特。考虑到兼容性,在设计中,Y、Cb、Cr 信号均采用10比特位。结合FPGA器件的特点,及在用硬件逻辑实现浮点运算时,满足精度和浮点的要求,将以上公式改为:

在RGB信号输出时,取其高8位即可。对于公式中的运算“1/256”,在代码设计时采用截数的方法实现。

1.6 行缓存

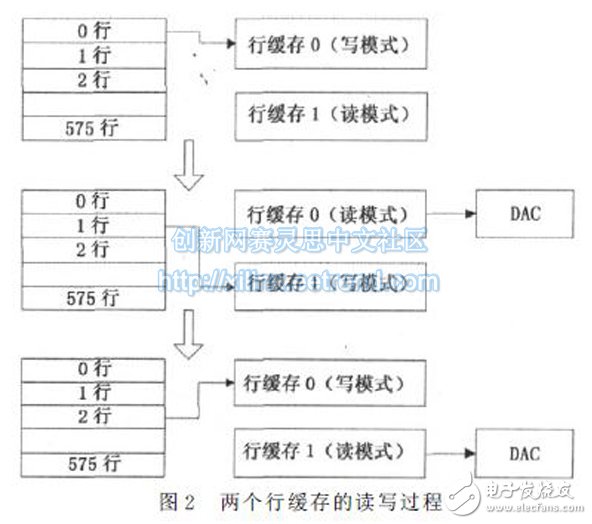

本设计采集的视频分辨率为720×576,采用24位色(R、G、B各为8位),因此保存一帧图像需要720×576×24=9.4921875Mbit的存储空间。可见,一帧图像数据所需的存储空间是比较大的,不适合直接保存在FPGA 片内的块RAM中。有几种方案可以选择,一是采用双口RAM 作为帧缓存,但这种容量的双口RAM 芯片较贵,势必增加成本;二是采用两片DDR SDRAM,通过乒乓控制算法构成双端口的帧缓存,这种方法需另外制板,增加了设计的复杂度;三是在FPGA片内构建两个行缓存,并采用乒乓控制算法,每次只存储一行视频数据,然后通过DMA的方式把576行视频数据逐一存储到DDR SDRAM 中。这样,仅需两行视频数据的存储空间,即720×2×24=33.75kbit,大幅减少系统对存储资源的需求,一方面节约了成本,另一方面也充分利用FPGA 片内的块RAM。图2显示了采用乒乓控制算法控制两个行缓存读写视频数据的过程。

对于分辨率为720×576的视频图像,第0行视频数据首先写入行缓存0,此时,行缓存0处于写状态,行缓存1处于读状态。当向行缓存0写完第0行最后一个像素时,产生Ho_444信号。行缓存0随之变为读状态,行缓存1变为写状态。接着,第1行视频数据开始写入行缓存1,同时,DAC从行缓存0读出第0行视频数据。当向行缓存1写完第1行最后一个像素时,再次产生Ho_444信号。行缓存0随之变为写状态,行缓存1变为读状态。然后,第2行视频数据开始写入行缓存0,DAC同时从行缓存1读出第1行视频数据。如此循环反复。因此,从整个控制模块两端看数据,输入数据流和输出数据流是连续不断的,没有任何停顿,完成数据的无缝缓冲与处理[3]。

1.7 PLB IP接口

PLB IP接口用于在PLB总线及用户IP核之间提供一个快速实现且高度适应的接口。通过使用VHDL generics语句,根据用户需求提供多样的服务及可选的特性。在本设计中,选择了中断、软件访问寄存器和DMA等特性。

视频数据自动写入行缓存,当写完一行视频数据后,由用户逻辑产生中断信号,同时视频数据写入另一个行缓存,接着CPU响应中断,并在中断服务程序中配置DMA 寄存器,如源地址、目的地址、传输长度等参数,接着启动DMA。然后,DMA申请得到PLB总线控制权,自动从行缓存中读出视频数据,并通过PLB总线存储到DDR SDRAM,这样循环反复,就在DDR SDRAM 中得到一帧完整的经过预处理后的视频数据。这样,在PowerPC处理器上运行的上层视频处理程序就可以直接从DDR SDRAM 中调用这些数据。

2 实验结果

通过示波器测量输出的像素时钟信号(PIXEL_CLOCK信号,该信号连接到视频DAC),得到频率瞬态值为27.03MHz,根据ITU-R BT.656 标准,1 行视频流包括1728个字,一帧图像包含两场,共625行,则输出一帧图像所需时间为

,即FPGA对一帧图像进行边缘检测的时间。注意到本设计所用的模拟摄像头为PAL制式,也是40ms/帧图像,所以,证明本设计实现了实时处理视频。另外,视频信号的测量必须注意终端匹配的问题[4]。

3 结论

本文提出一种高性能的实时视频处理平台,并在Virtex-II Pro XC2VP30FPGA上实现。相对于别的以硬件逻辑的形式实现图像处理算法[5-6],该平台采用双PowerPC硬核架构,以用户IP核的形式,为工程师在片上系统中实现各种视频处理算法提供了最大的灵活性。实验结果证明该平台能够实时处理视频,具有较高的实用价值,将广泛应用于消费类电子、视频监控、远程医疗和视频会议等领域。

- 相关推荐

- 热点推荐

- F

-

基于FPGA的实时视频图像采集处理系统2018-02-10 20454

-

运营级远程网络实时视频监控平台2010-02-03 4144

-

LabSQL的讨论及如何使用与技巧2013-10-05 4220

-

基于fpga的实时视频处理系统2014-04-08 1745

-

基于FPGA与DSP的视频处理系统设计2019-06-19 2112

-

基于FPGA+DSP架构的视频处理系统设计2019-06-28 2205

-

一种基于FPGA+DSP的视频处理系统设计2019-07-01 2282

-

FPGA实时视频图像处理系统的原理是什么?2019-08-22 3336

-

基于FPGA的实时视频信号处理平台该怎么设计?2019-09-29 2110

-

基于FPGA的实时视频信号处理平台的设计2012-08-13 1357

-

如何使用DSP和FPGA进行实时视频信号处理系统设计2018-12-18 1643

-

Aupera与赛灵思携手研发FPGA视频云处理平台2019-11-19 1134

-

采用FPGA和通用DSP相结合实现视频图像采集系统的设计2020-07-28 1746

-

基于ARM与FPGA的嵌入式实时图像处理平台2021-07-30 1009

-

ALINX FPGA+GPU异架构视频图像处理开发平台介绍2024-08-29 2804

全部0条评论

快来发表一下你的评论吧 !