基于FPGA图形和字符加速的液晶显示设计

FPGA/ASIC技术

描述

在传统的工业控制应用中,由于工业控制计算机中集成了高性能的显卡,故通常采用工业控制计算机+液晶显示器的体系结构,可方便地实现以图形和字符为主的人机界面。而在对实时性能和可靠性要求比较高的航空航天领域,通常要求液晶显示器内部集成图形显示功能,以减轻主控处理器的负担,并提高系统的实时性。重点介绍了如何利用FPGA实现基于Bresenham算法的2D图形绘制(包括画点、画线、画圆、画椭圆),以及点阵字符和位图在液晶屏上的显示,并提出了显示性能优化的一系列策略。经过仿真验证和产品实际应用,该设计方法实现的液晶显示模块图形和字符显示功能稳定,性能良好,适合于航空航天领域高可靠性液晶显示模块的应用需求。

1 引 言

在传统的工业控制应用中,多采用X86架构的工业控制计算机,计算机外置或集成显卡输出VGA/DVI视频信号,由液晶显示器完成显示功能。在这种架构下采用软件编程实现人机界面比较方便。而在嵌入式系统领域,尤其是航空航天仪表显示设备的信息显示领域,对显示任务的可靠性和实时性要求很高。一方面需要减少设备内部的模块及互联总线,以提高设备的可靠性并降低功耗;另一方面,设备所选用的高可靠性处理器性能通常较低,需要专门的硬件加速器辅助完成显示功能。硬件加速器主要完成字符显示、图表绘制及液晶屏驱动等功能,以减轻处理器的负担,提高外部通信总线处理的实时性。基于FPGA的液晶显示驱动及图形加速器就是为了满足显示仪表设备而设计的。由于液晶显示模块内部集成了图形和显示功能,对设备主机处理器的性能要求大大降低,这样就可以采用低性能、可靠性高的处理器来承担显示控制任务。

2 系统结构

2.1 总体结构

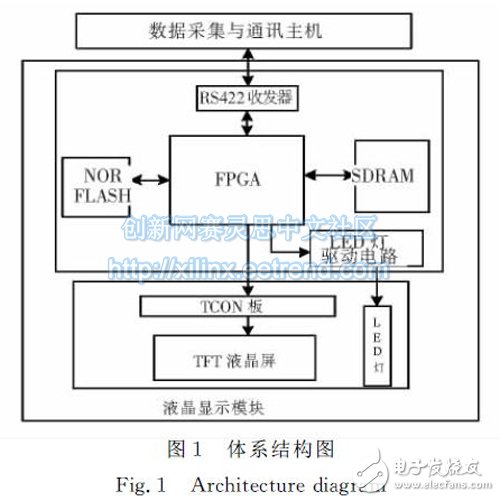

仪表设备系统结构图如图1所示,由数据采集与通讯主机和液晶显示模块组成。

2.2 数据采集与通讯主机

数据采集与通讯主机采用51系列单片机,外接A/D采集、CAN等接口,主要完成数据采集、通信及向液晶显示模块发送页面显示命令等功能。

2.3 接口

液晶显示模块与设备主机间为RS422串行接口,通讯波特率为200kbit/s,数据传输协议是自定义的,由帧头、数据包长度、命令、参数、校验和构成,单个数据包最大长度为256字节。

帧头:为0xEB、0x90两字节,为整个数据帧的通讯过程提供同步功能;

字节长度:1字节,数据帧格式中指令的总字节数,最大不超过255字节。

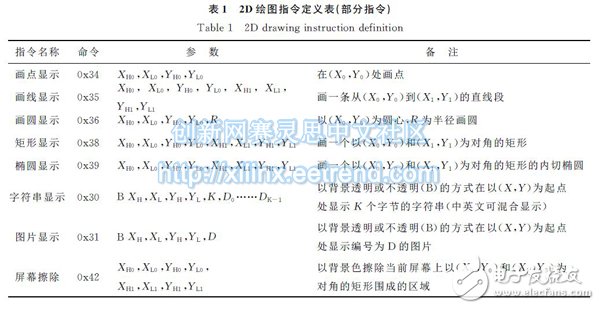

指令:液晶显示模块操作指令内容,包括命令和参数,表1给出了部分操作指令格式及含义;

校验:1字节,“字节长度”和“指令”字段的累加和,以校验数据帧的正确性。

2.4 液晶显示模块

液晶显示模块,相当于小型液晶显示终端,由液晶屏及其TCON 板、背光、图形加速及显示控制板组成。

液晶显示模块需完成的绘图命令有:屏幕擦除(背景填充)、画点、画线、画矩形、画椭圆、画圆、字符串显示、自定义字显示、图片显示、块拷贝、块粘贴等功能,以及字库及图片下载功能。除此之外,还有液晶屏亮度调节及状态管理等命令。

2D绘图指令定义见表1。

本设计选用的液晶屏为NEC公司的16.5cm(6.5in)TFT彩色液晶显示屏,分辨率为640×480,液晶屏自带TCON板,其接口为18bit数字RGB信号。

3 FPGA设计实现

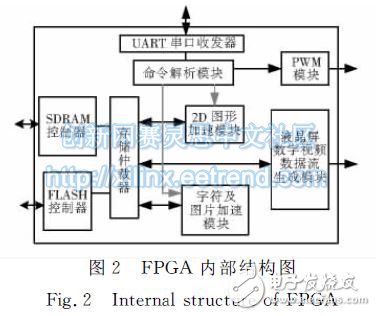

FPGA在本设计中完成的工作主要是:一方面,进行数据接收并解析,根据命令进行图形绘制操作,生成显示帧存储写操作数据流,最后将要改写的数据写入SDRAM 存储器中;另一方面,根据液晶屏同步信号时序要求,将帧存中显示区的数据定时地读出,生成液晶屏驱动数据流;其次,FPGA内部还具有PWM 信号生成模块,可调节液晶显示屏的亮度。

3.1 FPGA器件选型

FPGA选用Xilinx 2V3000系列[1],该器件具有28 672个LUT单元和个28 672个触发器以及96个BlockRAMs,便于实现大规模控制逻辑及FIFO、Buffer等;另外,FPGA 内部具有DCM,可将外部65MHz时钟转为25MHz时钟,用于液晶屏驱动时钟,并可内部经分频产生1kHz PWM信号,用于液晶屏背光亮度调节。

3.2 FPGA结构

FPGA内部结构如图2所示。

3.2.1 命令接收解析模块

数据命令(设备主机下发)以200kbit/s UART接口送入FPGA 中,FPGA 接收数据后,完成数据帧的识别、校验。对于校验无误的数据帧,解析命令字的含义,并将对应的参数传入相应的模块中,启动命令处理操作。

3.2.2 2D图形加速模块

所有的2D图形绘制操作都可以分解为画线段或画椭圆等基本图元操作,由于液晶屏为栅格显示结构,基本图元操作命令最终是转化为打点操作。

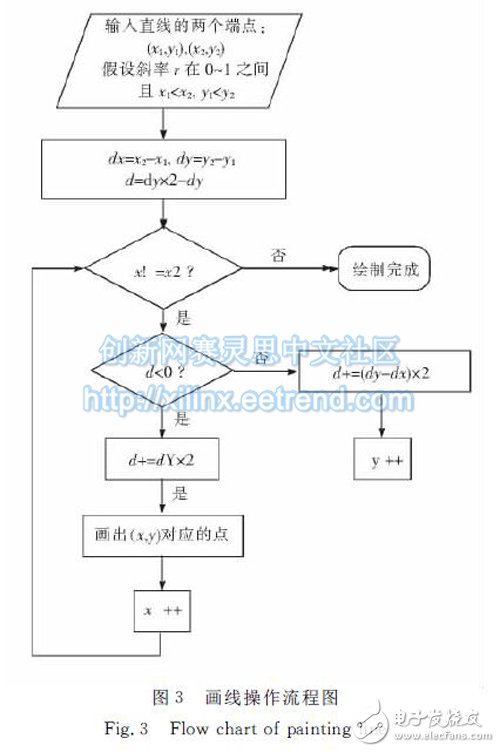

画线段和画椭圆弧采用的是bresenham 算法[2]。该算法的基本原理是在进行线段绘制操作时,首先根据线段的斜率确定绘制的起点和方向,以确定每次在X 方向还是Y 方向上步进,然后每步进一步,确定在另一个方向上的增量,保持不动或者增1、减1,最后输出该点坐标,流程图如图3所示。

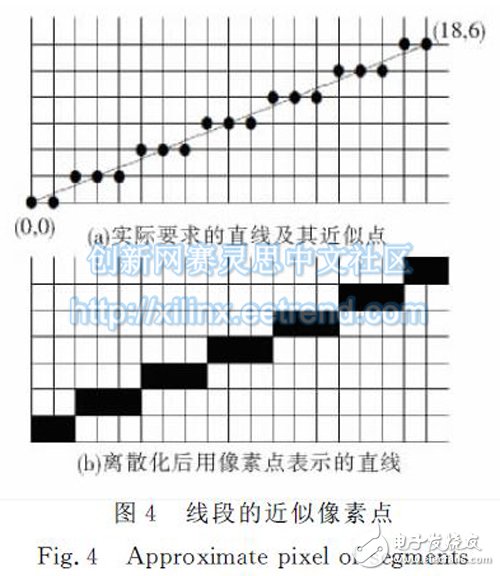

如图4所示,绘制一条从(0,0)至(18,6)的线段,第一个点为(0,0),由于dx>dy,则在x 方向上递进,每个时钟周期x 坐标加1。根据bresenham

算法,初始判决式为d1=dy×2-dx=6×2-18=-6<0,则第2个点(1,0),同时d2=d1+dy×2=6>0,则y++,输出第3个点为(2,1),依次输出下一个点,直到输出最后一个点(18,6)。

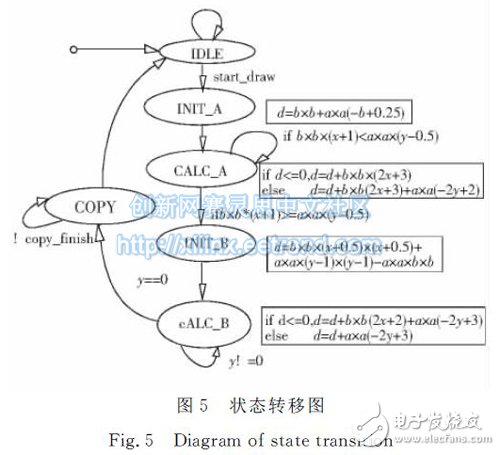

同样在进行椭圆或者圆绘制操作时,也采用了bresenham算法。在FPGA 中实现时,采用状态机的编码方式,以绘制圆心为(x0,y0)、长半轴为a、短半轴为b的椭圆为例,其状态转移流程图图如图5所示。图中CALC_A和CALC_B状态分别为计算1/4椭圆弧中的a轴方向和b 轴方向的像素点。

画线时的数据运算只有乘以2和加法,乘以2通过将数据左移1位,末位补0来实现。

在进行椭圆绘制时,乘法操作采用的是FPGA内部的MULT18X18S乘法单元,先将算式中的浮点数通过移位运算放大2n倍数转换为定点数,计算得到的结果再通过截掉最低的n 位,相当于除以2n。通过这种方法避免了在FPGA 中做硬件除法,同时提高了绘图效率。

3.2.3 字符及图片显示加速模块

在该设计中,液晶屏上显示的字符为点阵字符。该字符库是通过串行通讯接口(RS422)预置在FLASH 中的,字库为预先转换好的GB2312点阵字库。本设计中采用了两种规格大小的标准字库,西文为黑体8×16和16×32,汉字为16×16及32×32。除此之外,用户还可下载自定义的字库,点阵大小最大可以为256×256,字库可在屏幕上任意位置为起始点显示。

预置图片为256色BMP图片,最大不超过屏幕分辨率(640×480),可以在屏幕上任意位置为起始点显示。

字符和图片在数据结构上具有相似性,均为点阵数据。

在显示时,根据显示命令,首先从存储单元中获取欲显示的字符或图片的点阵数据。对于字符,其点阵数据中的“0”表示不显示,“1”表示显示,然后向显示坐标位置对应的地址空间中依次写入颜色值。对于不需要写入的像素点,在写操作时,使用SDRAM 的写屏蔽功能,每完成一行,地址切换到下一行,直至写操作结束。

3.2.4 液晶屏数据流生成模块

本设计中选用的液晶屏型号为NEC公司的NL6448-BC20-20[3],接口为LVTTL 数字RGB接口,包括R、G、B(每色为6bit)、HS、VS、DE、CLK等信号。

该液晶屏有两种时序模式,固定时序模式和DE信号模式。固定时序模式下,液晶屏有效数据起始点是以HS、VS边沿为参考的固定数值,而DE信号模式下,有效数据范围是以DE信号为参考的。本设计中选择了DE模式,每行中DE为高电平的第一个周期对应第一个有效数据。

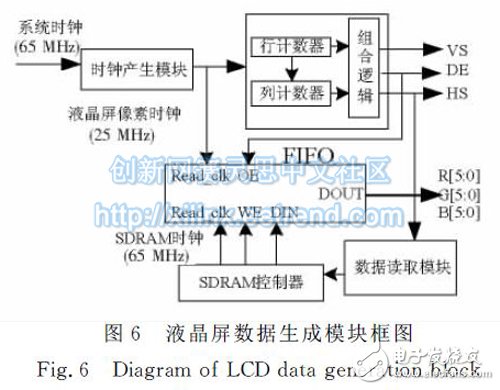

液晶屏数据生成设计框图如图6所示。该模块采用DCM 生成25MHz像素时钟,并采用两个计数器(行计数器和列计数器)生成DE信号[4-5],根据液晶屏时序要求,每行总共800个时钟,有效像素点为640个时钟;每列总共525行,有效数据区域为480行。在FPGA设计中,行计数器在像素时钟下计数,从0计数到799后,输出HS脉

冲,同时计数值回到0重新进行下一轮的计数;列计数器以HS信号脉冲为计数条件,从0计数到524行后,输出VS脉冲,同时计数值回到0。

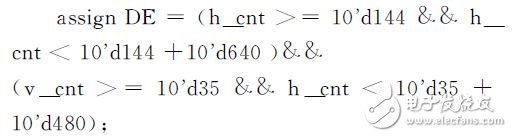

将行计数值定义为h_cnt,列计数值定义为v_cnt,数据有效信号DE设计为:

数据读取模块根据HS信号从SDRAM 存储器中读取一行有效数据到FIFO中,并采用DE信号作为FIFO的读使能信号,将FIFO中的数据取出,生成18bit RGB数字信号送给液晶屏TCON板,驱动液晶屏输出显示画面。

3.2.5 SDRAM 控制器

采用的SDRAM 容量为32M×32bit,设计的工作频率为65 MHz,SDRAM 中划分为多个区域:显示页面区、绘制操作页面区、字库区、图片区等。

SDRAM 器件在进行读写操作时,需要先激活一行,然后在该行内,针对某个列地址进读/写操作,操作完毕后,需要进行预充电以关闭该行,同时,SDRAM 需要定期地进行刷新以保持其内部数据稳定不丢失。用FPGA 实现的SDRAM控制器就是为了实现提供一个便于上层读写访问的简单接口。

3.2.6 FLASH控制器

采用的FLASH容量为16M×16bit的NOR FLASH。FLASH 主要用于存储字库和图片,内部数据可通过液晶显示模块数据通信口进行下载。

FLASH 接口为异步接口,在进行读操作时,其时序相对简单,类似于ROM。而在进行写操作时则相对复杂,在写FLASH 之前,先确认扇区为空,如果不为空,则需要先擦除。

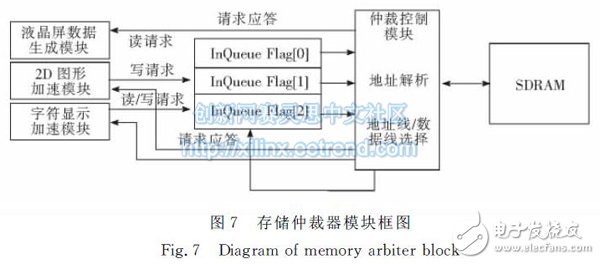

3.2.7 存储仲裁器

存储仲裁器模块结构如图7所示,在同一时间,SDRAM 只能为其中一个模块提供数据读或写操作。该模块的设计是为了解决多模块同时访问SDRAM 或FLASH 时的优先级控制,以及提供排队访问的机制。该模块中采用了标志位In-QueueFlag[2∶0]来分别记录各模块的状态请求,并分别给出应答信号,以控制其对于SDRAM的读写访问。

在FPGA设计中,由于液晶屏数据生成模块对数据的及时性要求最高,给予其最高的优先级,在SDRAM接口空闲的情况下,优先处理InQueue-Flag[0]=1的请求,处理完毕后,InQueueFlag[0]清0。如果InQueueFlag[0]=0,则检查InQueue-lag[1]是否为1,依次直至所有标志位为0。

4 优化系统性能的几点设计

4.1 采用双图层、多页面的设计

显示屏在显示时,具有前景和背景两个图层。在绘图过程中,可进行切换[6]。

该显示模块在设计时,存储区中开辟了10个操作页面和显示页面。正常使用情况下,在后台页面进行绘图操作,绘制完成后,将显示页面切换至该页面。这样可避免因绘图操作对内存数据更新而引起的显示不流畅感。

4.2 256色调色板设计

液晶屏有144种颜色,但对于图形显示屏而言,实际应用中并不需要这么多种色彩,256色已经可以满足应用要求。在FPGA 内部,使用BlockRAM 建立了一个256色的调色板,每种色号对应一个RGB颜色值。

如果每个像素都存储RGB值,则每像素需要18位。而采用256色,每个像素点的颜色只需要用8位来表示,由此可见,采用256色调色板的设计可以减小一半以上的内存带宽需求。

4.3 缓存设计

在进行绘图和字符、图片等显示操作时,每次写入SDRAM 内存的数据,不是立即写入的。而是先将要操作的SDRAM 地址及其数据暂存在buffer中,由专门的模块负责将其写入SDRAM中。这样的设计有两个好处,一是减少了对存储器的频繁读写,存储器读写效率提高;另一方面,绘图模块无需等待数据写入,便可继续进行绘图操作,大大提高了绘图效率,从而提升了整个显示模块的性能。

4.4 高效率的SDRAM 控制器

用FPGA 实现的SDRAM 控制器[7-8],其核心是控制好SDRAM 读写命令给出的时机,并定时刷新SDRAM,同时提供方便的用户接口给其他模块使用。

另外,由于SDRAM 的特性,进行单字节操作时,其效率很低。经过分析,在65MHz时钟下,写入1个字节,至少需要8个时钟周期,包括激活命令、写命令、预充电命令以及等待时间,效率只有12.5%。

本设计中使用Burst操作,在Fullpage操作时,其读写效率会大大提高,接近97%。

4.5 FLASH数据校验机制

为了保证存储在FLASH区域中数据的完整性,系统在每次启动时,会发送相关的自检命令检查FLASH 数据的完整性,并将自检信息显示在液晶屏上,以保证字库、图片数据的正确性。

5 仿真及测试结果

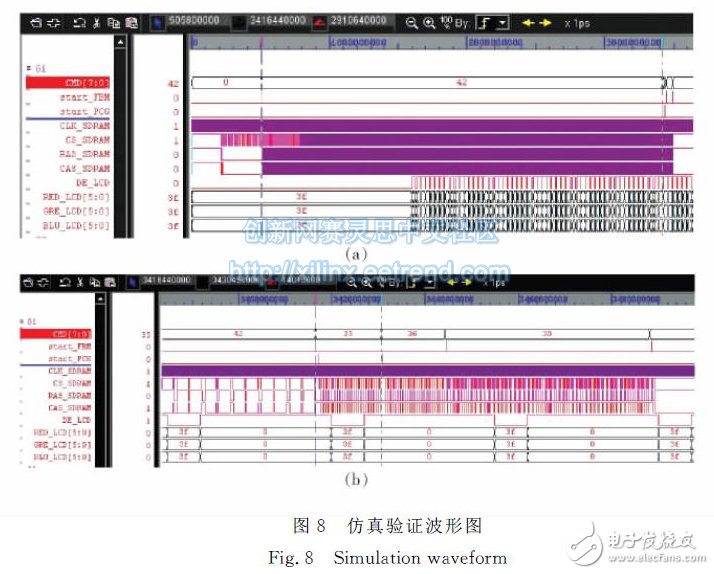

采用ModelSim6.2g对本设计进行了功能和时序仿真,仿真了屏幕擦除、画线、画圆和字符显示等指令的性能情况。如图8中(a)、(b)图所示,图中,cmd信号为指令(详见表1),start_FBM、start_PCG是指令操作时的起始信号,图中还给出了SDRAM 信号线。从图中可以看到,cmd信号从0x00变到0x42表明开始进行擦除操作,由0x42切换到0x35表明擦除操作结束,开始执行画线命令。可以看到在屏幕擦除操作过程中SDRAM 信号线CS、RAS、CAS上信号不断变化,此时SDRAM 执行写操作。

仿真结果表明,在65MHz时钟频率下,典型操作时间为:擦除整屏(640×480)耗时为2 910.6μs;画一条长度为100的斜线段,耗时为14.0μs;绘制一个直径为10的圆,耗时为13.6μs;显示一个16×16大小的点阵汉字,耗时为44.1μs。

本设计实现的液晶显示模块在典型应用情况下,每秒约有250条绘图命令,包含了屏幕擦除及大量画线及字符串显示操作。经仿真测试,在该使用情况下,SDRAM 读写占用率约为21%。

在RS422数据总线满负荷情况下,每秒最大接收10k字节数据,最多为5k个汉字显示,估算SDRAM 读写占用率约为30%,资源利用仍有足够的余量。

由此可见,采用本设计的液晶显示模块在典型工况和数据总线满负荷情况下,均有足够的余量能够高效地完成上位机发送的作图命令,不会造成显示迟滞。

该液晶显示模块已应用于飞行器仪表显示系统中,并成功完成了飞行任务。

6 结 论

采用基于FPGA 图形和字符加速的液晶显示模块,可以较好地满足航空航天领域中高可靠性仪表显示设备中低性能微处理器作为主机,而液晶显示模块作为显示终端的应用需求,减轻了处理器及显示控制软件的复杂度。当然,本设计的部分性能指标还有待提高,为了适应高分辨率、大尺寸TFT液晶屏的要求,需要提高FPGA 运行频率,同时采用DDR/DDR2SDRAM 等高速存储器件。

- 相关推荐

- 热点推荐

- F

-

利用处理器FPGA与液晶显示模块的图形显示的编程技术2021-07-30 930

-

201图形点阵式液晶显示模块及其应用2019-02-10 978

-

201液晶显示模块及其应用2019-01-16 1005

-

如何在液晶显示器上显示汉字、ASCII字符和彩色图形2018-04-10 20576

-

字符型点阵式 LCD液晶显示屏及液晶显示技术的详述2017-11-22 3681

-

LCD液晶显示汉字字符集表2016-12-23 1057

-

基于8051的Proteus仿真-字符液晶显示的频率计2016-09-01 863

-

【FPGA设计实例】基于FPGA的图形液晶显示面板应用2012-04-09 34394

-

基于FPGA的液晶显示接口设计2009-09-26 1507

-

DM12864M 汉字图形点阵液晶显示模块2009-09-09 656

-

图形点阵液晶显示的单片机开发系统的设计2009-05-27 524

-

HD61202图形液晶显示模块2009-01-04 1262

-

点阵字符型液晶显示模块使用手册2008-11-01 1090

-

图形液晶显示实验2008-09-26 3556

全部0条评论

快来发表一下你的评论吧 !