基于FPGA 的LDPC 码编译码器联合设计

FPGA/ASIC技术

描述

该文通过对低密度校验(LDPC)码的编译码过程进行分析,提出了一种基于FPGA 的LDPC 码编译码器联合设计方法,该方法使编码器和译码器共用同一校验计算电路和复用相同的RAM 存储块,有效减少了硬件资源的消耗量。该方法适合于采用校验矩阵进行编码和译码的情况,不仅适用于全并行的编译码器结构,同时也适用于目前广泛采用的部分并行结构,且能够使用和积、最小和等多种译码算法。采用该方法对两组不同的LDPC 码进行部分并行结构的编译码器联合设计,在Xilinx XC4VLX80 FPGA 上的实现结果表明,设计得到的编码器和译码器可并行工作,且仅占用略多于单个译码器的硬件资源,提出的设计方法能够在不降低吞吐量的同时有效减少系统对硬件资源的需求。

1 引言

在数字通信系统中,采用前向纠错编码(FEC)技术可大幅提高数据传输的可靠性。其中,LDPC码凭借其优异的纠错性能、较低的译码复杂度和可并行实现的译码结构,已被数字卫星广播(DVBS2)、无线局域网(WLAN)和全球微波互联接入(WIMAX)等多个通信标准采纳。

如何在大规模集成电路上实现高速的LDPC 编译码器一直是LDPC 码应用研究的一个焦点。理论上,可根据二部图中的所有节点及边线实现全并行结构的LDPC 码译码器,但随着码长的增长,过高的布线复杂度及庞大的资源需求量将导致全并行结构的译码器难以实现。采用串行结构虽然可以减少硬件资源的消耗量,但译码器所需的存储空间会随着码长的增长而迅速增加,并且其较低的译码吞吐量通常不能满足实际应用的需求。2001 年Kou 等人[1]提出了准循环结构的LDPC 码,由于其校验矩阵的准循环特性,译码器可以采用部分并行结构进

行实现,从而使得基于长码的高吞吐量LDPC 码译码器得以实用化。现阶段部分并行结构QC-LDPC译码器实现的研究工作已全面展开,文献[2-8]给出了几种有效的基于FPGA的译码器实现方法。在编码器的实现上,如果直接采用生成矩阵编码,那么算法复杂度将随着码长的增加以平方速度递增,2001 年Richardson 等人[9]提出了一种简化的编码算法,但其所需的存储和运算量依然过于庞大。此后,学者们提出了一些结构化的编码方法,其中一种是设计生成矩阵也具备准循环性质的LDPC 码,利用生成矩阵进行编码,文献[10]给出了该方法的编码电路;另一种方法是采用特殊结构的准循环校验矩阵进行编码,例如IEEE 802.16e (WiMAX),IEEE 802.11n(WLAN)等标准采用了一种双对角结构的准循环校验矩阵进行编码,针对该结构,文献[11]提出了一种快速递归编码算法及该算法的并行硬件实现架构。但现有的LDPC 码编译码器设计方法都只针对编码器或译码器单独设计,并各自优化其吞吐量和FPGA资源,而实际的应用系统多数属于全双工通信系统,系统需要编码器和译码器两者同时工作,采用分离式设计将使得编码器和译码器的硬件资源无法得到有效复用,导致FPGA资源的利用率不高。

本文针对IEEE 802.16e, IEEE 802.11n 等标准建议的LDPC 码,提出了一种编码器与译码器联合设计方法,该方法使得编码器能够利用译码器在垂直运算时闲置的校验计算电路进行编码。提出的实现结构中,待编码数据、待译码数据和译码码字共用相同的存储块,编译码器的各处理单元共享同一组地址信息,有效减少了编译码系统对硬件资源的需求。

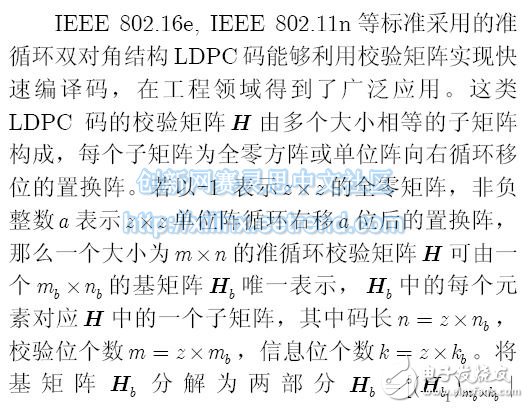

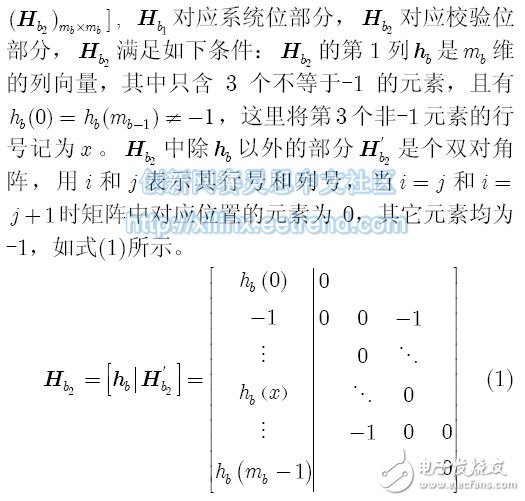

2 基于H 矩阵的LDPC 编码

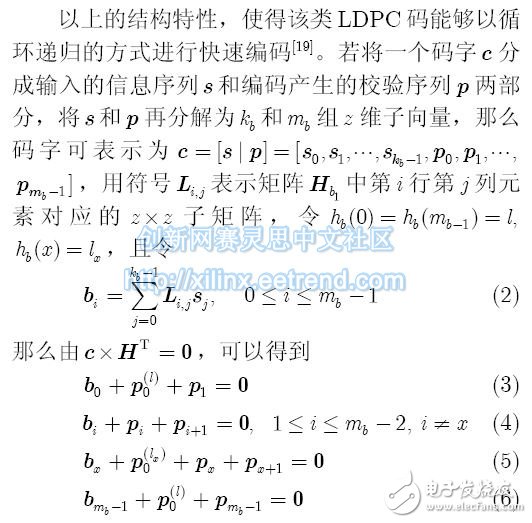

个矩阵与向量相乘的结果相加,且共有mb 个bi 向量需要求解,即便由于矩阵的结构特性使得矩阵乘法可以使用向量的循环移位代替,其计算量仍然较大。而其它式子均为2~3 个向量的加和,其计算量实际较少,因此整个编码器的计算复杂度主要集中于式(2)。通过对式(2)分析可知,bi 实际由H 矩阵每行对应位为1 的各信息位相加得到,显然,如果将码字序列的校验位部分全部置零后利用H 矩阵求解其伴随式,那么得到的伴随式与bi 等效。因此可以利用系统中现存且闲置的校验计算电路,通过把校验位置零后计算伴随式的方法将其复用到对信息位的编码上。本文的编译码器资源复用方案即利用了这种校验计算电路编码的思想进行设计。

3 LDPC 码的译码过程分析

下面以归一化最小和算法为例,分析LDPC 码的译码过程及常见的译码器实现方式,结果表明:常规LDPC 码译码器实现中包含一校验计算电路,且由于译码算法本身的交替迭代性质导致该校验计算电路在译码过程中有一半的时间处于空闲状态。

现有的LDPC 码译码器实现通常被划分为3 个主要工作模块[5−12] ,其中变量节点处理单元(VNU)完成垂直运算,校验节点处理单元(CNU)完成水平运算,校验方程计算单元(PCU)完成译码判决。从上面的译码过程可知,垂直运算和水平运算不能同时进行,每次迭代中垂直运算需要以水平运算产生的作为输入,水平运算反过来又需要垂直运算的结果,因此在同一时间里VNU与CNU必有一方空闲。另外,PCU 的校验处理必需安排在VNU 对信息更新完毕之后,但其与CNU 没有数据处理交集,因此PCU 与CNU 通常被设计为并行工作。对于部分并行结构的译码器,各模块的并行度一般按照校验矩阵的分块来划分。对于子矩阵大小为z×z的校验阵,每轮迭代的前半部分各个VNU 对其对应分块的z 列变量节点顺序进行更新,若VNU 数据更新处理的流水线长度为Lv ,那么VNU 模块在一次迭代中的工作总时长为z+Lv个系统时钟周期。而PCU 则在CNU 处理的同时顺序将z 行的校验和进行加和,另外还需要Lp 个时钟周期检查伴随式的各分量是否全部为0,因此CNU 模块在一次迭代中的工作总时长为z+Lp 个系统时钟周期。对于大部分校验阵,z 比Lv ,Lc 和Lp 要大得多,而且Lv ,Lc 和Lp 通常大小相近,或可以被设计为完全相等。比如为了运算方便VNU 和CNU 通常需要用不同的数据形式(补码和原码)表示,而在实际设计中,可以选择将原码和补码间的转换安排在VNU或CNU 部分来达到两者流水线长度的平衡。译码器各模块的工作时序如图1 所示。

由图1 的工作时序可以看到,负责译码判决的PCU 只有在每次迭代的后半部分处于工作状态,而PCU 模块主要由校验计算电路组成,根据第1节的讨论,我们可以利用该校验计算电路在垂直运算的空闲时间对信息位进行编码,从而提高整个编译码系统的资源利用率,达到减少硬件资源消耗量的目的。以上讨论基于归一化最小和算法,但对其它LDPC 译码算法其迭代过程类似,只有水平运算和垂直运算的计算处理有所变化,因此该资源共享的设计思路对一般译码算法具有通用性。

4 编译码器的联合设计

4.1 编译码器复合结构

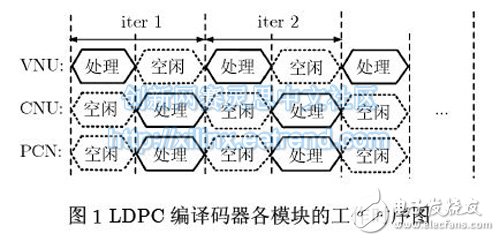

本文利用编码器和译码器在码字校验计算上的可协作特性,针对二者的数据流向复用存储资源,提出了如图2 所示的编译码器复合结构。该结构包含3 个处理单元,其中变量节点处理单元(VNU)和校验节点处理单元(CNU)只作译码处理,校验方程计算单元/编码校验位计算单元(PCU/ENC)被设计为一个时分复用模块,在一半的处理时间里,它作为校验方程计算单元(PCU)检查译码结果的合法性,另一半处理时间里,它作为编码校验位计算单元(ENC)计算编码产生的各校验位。存储单元分为4 部分,分别是位宽为Q bit 的信道初始信息存储块RAM_F,位宽为Q+T+1 bit 的混合信息存储块RAM_M,位宽为kb bit 的译码码字存储块RAM_C 和位宽为mb bit 的编码校验位存储块RAM_P,其中Q 是译码器处理数据的量化比特数,T 是译码器最大迭代次数。

本文提出的复合编译码系统工作过程如下:

(1)初始化:将Q bit 的信道接收信息存储到RAM_F 中,将T bit 的待编码数据补零后扩展为Q+T+1 bit 存入RAM_M,初始化迭代次数为0次。RAM_M存储块中的数据由3 部分组成,其中包括Q bit 的译码迭代外信息(即 的更新结果),T bit 的待编码数据和1 bit 的译码判决结果。初始化完成后RAM_M 中的迭代外信息和译码判决位均为全零。

的更新结果),T bit 的待编码数据和1 bit 的译码判决结果。初始化完成后RAM_M 中的迭代外信息和译码判决位均为全零。

(2) 变量节点更新及编码处理: 分别从RAM_F 和RAM_M中取出Q bit 的信道信息和迭代外信息送入VNU 处理,然后将更新得到的Q bit迭代外信息和1 bit 的译码码字回写到RAM_M中。其中译码码字被重复存储到RAM_M 和RAM_C 中,采用这样的存储结构需要额外的一块

RAM 资源作为RAM_C 的码字输出缓存,但它可以使得PCU 能够从RAM_M 中迅速读取判决所需的译码比特,且有效降低了电路的布线复杂度,从而提高运行时钟频率,增大系统的编译码吞吐量。在变量节点更新的同时, PCU/ENC 单元从RAM_M 读出的数据中取出1 bit 待编码信息进行编码,计算得到的校验比特存入RAM_P。需要说明的是系统编码帧数是译码帧数的T 倍,T 是译码器的总迭代次数,RAM_M中总共存储T组信息序列,每次迭代中PCU/ENC 取出的待编码比特对应T 组不同的信息序列。如果需要等吞吐量的编译码系统,可以通过屏蔽部分编码处理得到。

(3)校验节点更新及译码判决:从RAM_M 中取出Q bit 迭代外信息送入CNU 处理,处理结果回写入RAM_M。同时从RAM_M 中取出变量节点更新得到的译码码字,送入PCU/ENC 进行码字的合法性校验。如果校验满足或达到最大迭代次数,将RAM_C中的判决码字作为译码结果输出,否则转到(2)继续下一轮迭代处理。

这种结构中待编码数据,待译码数据和译码码字共用同一存储块,可以有效减少编译码器对存储资源数量的要求,而且读取一个存储块可以同时获得编码和译码所需的数据,使得VNU, CNU 和PCU/ENC 3 个模块可以共享相同的地址信息,避免了ENC 独立产生读写地址所需的大量逻辑资源,这样的设计同时也有效降低了运算单元和存储单元之间的布线复杂度。最后,T 路信息序列在不同迭代中分时复用ENC 进行校验位的计算,能有效提高硬件资源的利用率和编码器的吞吐量。

通过改变VNU, CNU 和PCU/ENC 运算单元的数量,该复合结构可以实现不同并行度的编译码器。当VNU, CNU 和PCU/ENC 只设置一个运算单元时,整个编译码系统为串行架构,此时系统占用的硬件资源少,但编译码吞吐量也较低,适合硬件资源十分紧缺且对数据速率要求不高的实现平台。当VNU 运算单元个数与码长相等、CNU 和PCU/ENC 运算单元数量为校验位个数时,编译码系统为全并行架构,此时架构中的存储单元应采用逻辑资源表示,系统的编译码吞吐量大,但要求大量的硬件资源,适合于短码的实现。当VNU 运算单元个数与检验矩阵的列分块数一致,CNU 和PCU/ENC 运算单元个数与行分块数一致时,编译码器为部分并行架构,此时系统可以达到硬件资源需求量和吞吐量的折中,适合于吞吐量较大的长LDPC 码编译码器实现。

4.2 编译码器的码长码率兼容设计

在编译码器采用完全相同的校验矩阵进行编译码的情况下,本文提出的复合结构能够将整个PCU 的校验电路资源复用到编码器的码字计算上,从而节省编码器所需的大部分硬件资源。典型的应用有中继通信和对等的点对点通信等,尤其在卫星中继通信中,由于低轨道中继卫星需要通过译码再生对高轨道卫星的数据进行转发,同时还需要将自身观测得到的数据回传到地面站,其要求的编码吞吐量比译码吞吐量高,是该编译码器联合设计方法应用的一个理想场景。但在更多的实际应用中,由于信道条件不对称、设备的尺寸及功耗的约束不对等以及上下行业务需求不同等原因,通信系统的收发两端很难采用完全一致的编译码体制。下面讨论提出的复合结构在编译码矩阵的码长和码率上的兼容设计。

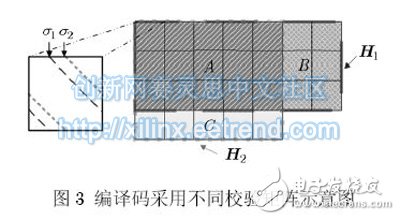

当编译码采用不同的校验矩阵时,需要根据两矩阵的差异性对复合结构进行修正,需要考虑的矩阵差异主要包括4 个方面:(1)矩阵对应分块的偏移量不相同;(2)对应各分块的行重列重不同及分布不一致;(3)矩阵的分块数不相等;(4)子矩阵的大小不同。假设不同的两校验矩阵H1 和H2 ,其中两矩阵的公共部分标记为A,矩阵H1 中独立于H2 的部分标记为B, H2 中独立于H1 的部分标记为C,如图3所示。

首先,由于矩阵的偏移量不同并且各分块间的偏移量差值不可能完全一致,这将导致对应分块的编码和译码信息无法共用相同的RAM 和地址发生器。针对这一问题,可以对初始化编码信息的存储地址作一定的偏移来达到数据访问的一致性。对于两矩阵相同的情况,在数据初始化阶段,RAM_M中对应各矩阵分块的各块RAM 均从0 地址开始顺序存入各编码信息,而在译码迭代阶段,编译码器则以公共偏移量作为初始地址顺序读写子矩阵中的信息进行计算。而对于两矩阵不相同的情况,若编译码校验阵在同一位置的两个子矩阵的向右循环移位次数分别为σ1 和σ2 ,那么在数据初始化阶段,该分块的RAM 可以将编码矩阵和译码矩阵的地址差值作为初始地址对编码信息进行存储,具体操作时考虑到地址的循环移位性质,还需要对分块大小进行取模运算, 即信息存储首地址应为(σ1−σ2)⋅modz ,这样在译码迭代时就可以将译码矩阵的地址偏移量σ2 作为公共地址来读取编译码信息。由于RAM 共用,改变编码信息的写入顺序显然需要同时更改初始译码外信息的存储顺序, 但是由于RAM_M 存储块中的各外信息部分的初始值均为0,因此信息位存储的初始顺序的改变实际并不扰乱译码初始信息的读写顺序;其次,两校验阵在行重和列重上的差异也会产生一些问题,在垂直运算阶段,由于VNU 和ENC 同时工作,相同列分块的列重不同和分布不一致将使得编译码数据的访问不一致,造成RAM 资源共用困难。而在水平运算阶段,由于CNU 和PCU 使用的同为译码矩阵,因此不存在矩阵差异对数据读写带来的影响。另外,在垂直和水平运算间需要复用校验计算电路,而行重不相同则会引起校验计算电路不通用。在具体的电路实现中,由于存储的编译码数据是经过拆分和组合后读出或写入的,因此并非必须相同位置的矩阵分块才能共享RAM 存储,实际上只要在垂直运算阶段两矩阵在同一列分块的列重相等即可组合共用相同的RAM,而两矩阵对应列分块的列重不同则可以通过列分块的交换来缓解,这是由于校验阵的列交换不改变码本空间,对于最后无法通过列分块解决的列重不相等则需要放弃RAM 共用。对于行重不同引起的校验计算电路不通用,可以在校验计算电路中实现较大的行重,在处理行重较小的校验矩阵时作屏蔽处理来解决问题;还有,矩阵的分块数不相等会对资源复用带来较大的影响,显然只有两个矩阵的交集部分(区域A)能够采用资源复用设计,其余各矩阵的独立部分(区域B 和区域C)则需要分开设计,需要注意的是,考虑编码矩阵的区域范围时只需考虑系统位部分,因为编码时校验位部分本身就需要通过置零的方式进行屏蔽,而对于编码矩阵中与译码矩阵不重合的部分在校验计算电路上可以直接舍去校验位的加和;最后,对于子矩阵大小不同的情况,虽然也可以通过资源复用来达到节约资源的目的,但从图1 的时序分析可以知道,子矩阵的大小不同将引起各模块计算时间的不相等,造成时隙等待,从而增加控制上的复杂度,并且会造成吞吐量的降低。而从码构造上看,矩阵的分块大小并不会对码性能构成大的约束,因此子矩阵大小差异的问题通过构造分块大小相等的编译码矩阵来解决显然更加合适。

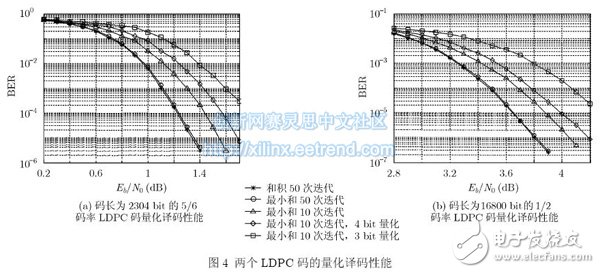

5 硬件实现结果

采用提出的编译码器联合设计方法对两组不同的LDPC 码编译码器进行部分并行结构的实现,第1 组编译码均采用码长为2304 bit,码率为5/6 的LDPC 码;第2 组编译码采用不同的校验矩阵,两矩阵的分块大小相同,其中译码采用16800 bit 的1/2 码率LDPC 码,编码采用8400 bit 的3/4 码率LDPC 码。芯片使用Xilinx 公司的XC4VLX80FPGA,在ISE 10.1 平台上进行逻辑综合和布局布线,在ModelSim 6.2 上进行功能仿真和时序仿真。两个译码器均采用4 bit 均匀量化,译码算法采用归一化最小和算法,归一化修正因子α 选择为0.75,最大迭代次数均为10 次。图4 是在AWGN信道,BPSK调制条件下,没有量化的50 次和积迭代译码和量化后的归一化最小和译码的性能对比。

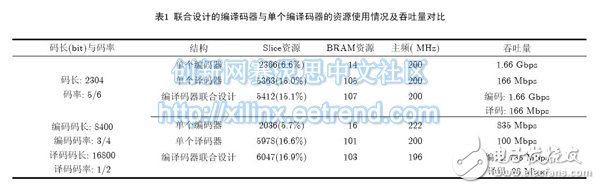

对于两组编译码器实现,表1 分别列出了单个编码器、单个译码器和联合设计的编译码器三者的资源使用情况及系统的信息吞吐量。除了采用提出的编译码复合结构以外,联合设计的编译码器和单个编译码器实现使用的设计优化技术均相同。对于码率为5/6 的第1 组实现,独立设计和联合设计两种情况下编译码器均满足5 ns 的布局布线约束,工作时钟频率为200 MHz。从表1 的数据可见,联合设计的编译码器消耗的系统资源仅略多于单个译码器实现,其中逻辑资源多0.1%, BRAM 资源多2块,而在编译码器分开设计的情况下,单独设计一个编码器需要消耗6.6%的芯片逻辑资源及14 块BRAM资源,采用复合结构设计可以节省约30%的

逻辑资源和10%的BRAM 资源。对于编译码矩阵不同的第2 组实现,独立设计时编译码器的工作时钟频率分别可达222 MHz 和200 MHz,联合设计时系统工作主频稍有降低,为196 MHz。联合设计的编译码器消耗的系统逻辑资源比单个译码器多0.3%, BRAM 资源多2 块,与分开设计的情况相比可节省约25%的逻辑资源和12%的BRAM 资源。在本文提出的编译码器复合结构中,编码器的绝大部分资源由译码器共享得到,因而减少了编码器对硬件资源的额外需求,从而显著提高了FPGA资源的利用率。

该复合结构主要从工作时序上对编码器和译码器的各组成部分作资源复用,除了要求RAM 的位宽较一般的译码器位宽宽以外,其它主要的译码模块的设计与现有的设计技术不冲突,多数的其它设计优化方法都可以应用到本结构中,该设计仅利用了译码工作时的空闲时序进行额外计算。从设计原理上看,对各模块增加资源复用设置只需要在原有电路上增加一些选通开关,对译码电路的布线复杂度影响较少,因此对整个编译码系统的工作频率及吞吐量影响也较少,具体的实现结果也表明了这一点。该资源复用方案适用于一般的编译码系统,能够达到节省系统资源而基本不降低编译码吞吐量的目的,其资源复用程度只与编码和译码采用的校验矩阵的相似度有关,而与系统具体使用的LDPC 码的码长和码率等参数没有关系。从两组编译码器的实现结果可以看到,对于第1 组高码率短帧长LDPC 码和第2 组码率较低的LDPC 长码,提出的联合设计方法都能够在节省资源的同时实现与独立设计的编译码器相当的吞吐量,而第1 组实现由于使用完全相同的校验矩阵进行编译码,其资源节约百分比明显要高于编译码矩阵不同的第2 组实现。需要说明的是,编译码器所能够实现的吞吐量大小只与采用的LDPC 码结构和具体模块的设计有关,而该资源复用结构仅提供一种不降低吞吐量的资源复用设计,正如给出的两个实现例子中,第1 组实现的吞吐量明显要高于第2 组,但并不表明该方法更适合于高码率短码的编译码器设计,也不表明该方法能够使高码率译码器的吞吐量做得更高,这是由于编译码系统本身选用的参数不同而导致吞吐量大小的差异,第1 组实现的编码并行度本身要高于第2 组,且计算信息吞吐量时,高码率LDPC 码的信息位比例要较低码率情况时高,因此在相同的帧处理速度下,高码率码可实现的信息吞吐量也高。综上所述,与分离式设计相比,本文提出的联合设计方法能够在不降低系统吞吐量的前提下减少硬件资源的需求量,特别适用于资源受限的硬件平台。

6 结论

本文分析了准循环双对角结构LDPC 码的编译码过程,利用译码器在垂直运算时闲置的校验计算电路,通过把校验位置零后计算伴随式的方法将其复用到编码器的码字计算中,提出了一种利用校验矩阵编译码的编译码器联合设计方法。该方法使得编译码器共享相同的RAM 存储块及地址产生器,有效减少了实现所需的存储资源和逻辑资源。在Xilinx XC4VLX80 FPGA 上的实现结果表明,联合设计的编译码器能够进行高速编译码,且仅占用略多于单个译码器的硬件资源,提出的设计方法能够在不降低系统吞吐量的同时减少对硬件资源的需求量。

-

怎样设计基于CMMB系统的LDPC译码器?2019-08-23 1953

-

大围数QC_LDPC码的译码器该怎么设计?2019-09-30 1737

-

突发通信中的Turbo码编译码算法的FPGA实现2021-05-07 1487

-

LDPC码与RS码的联合迭代译码2009-05-12 1119

-

基于FPGA 的(3,6)LDPC 码并行译码器设计与实现2009-06-06 652

-

IEEE 802.16e中LDPC译码器的实现2009-08-05 697

-

高码率LDPC码译码器的优化设计与实现2009-11-25 889

-

LTE标准下Turbo码编译码器的集成设计2010-11-11 974

-

LDPC编译码2009-03-01 2322

-

WIMAX LDPC码译码器的FPGA实现2011-06-08 2522

-

基于FPGA的RS码译码器的设计2013-01-25 1117

-

采用FPGA芯片实现多码率QC-LDPC译码器的设计与测试2019-01-08 3872

-

使用FPGA实现800Mbps准循环LDPC码译码器的详细资料说明2021-01-22 1210

-

如何使用FPGA实现结构化LDPC码的高速编译码器2021-03-26 1085

-

基于FPGA的800Mbps准循环LDPC码译码器2021-06-08 853

全部0条评论

快来发表一下你的评论吧 !