基于FPGA的智能电子衡器称重测控仪设计与实现

FPGA/ASIC技术

描述

在FPGA芯片上内嵌CPU是用软件编程实现硬件CPU功能,是嵌入式技术发展趋势;在此针对测重系统设计了采样电路、信号调理电路、超重报警电路以及显示电路,同时针对软件嵌入式技术,并以spartan6XC6SL开发板为核心,编写了软件CPU并成功嵌入Xilinx公司的spartan6XC6SL开发板上的X45-CSG324芯片内,实现了智能小车称重测控仪的设计。

数字式智能称重传感器及数字称重系统是近些年来电子衡器领域研究开发的热点。随着科学技术的进步,工业化过程自动化水平的提高,特别是数字技术与信息技术的发展,对电子称重系统提出了数字化、智能化的要求。而传统的称重系统存在着输出模拟信号小,一般为20~40mV;传输距离短;抗干扰能力差;称重控制仪表复杂;安装、调试不方便等先天缺陷,根本不能适应电子衡器的智能化要求。为求解决这些难题,一般采用单片机系统设计,上述难题基本解决,但设计电路负杂,本文采用功能强大的FPGA芯片XC6SLX16-3CSG324,可使外围电路更简单,体积更小,优越性更明显。

1 系统总体设计

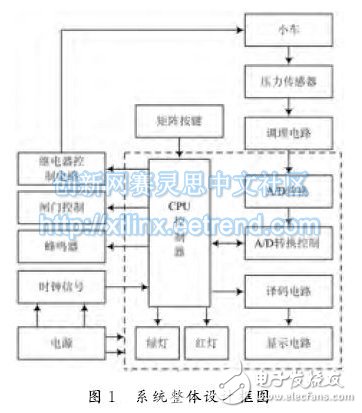

本系统主要由硬件电路和FPGA程序设计2大部分组成,如图1所示,硬件电路设计以FPGA芯片X45-CSG324为核心的内部控制部分,外围电路有压力传感器、调理电路、继电器控制电路、蜂鸣器驱动电路、显示电路以及时钟信号和按键等。FPGA程序模块有A/D转换与转换控制、CPU、译码电路等。该系统主要是通过控制继电器开关来控制载重小车电机正转和反转,正转和反转代表小车前进和后退,以便使小车能在压力传感器上停在合适的位置;重量通过压力传感器转变电信号后,通过调理电路输入FPGA芯片,在内部通过编程实现12 为A/D转换,并把A/D转换的数值送入CPU,经过数据处理,通过译码器送到12显示数码管显示重量;测量范围可以通过矩阵按键预先设定,若在测量范围内,绿灯亮,闸门打开,小车可以通过;若重量小于预设下限值,则红灯指示亮,闸门不开;若大于预设上限值,红灯亮而且蜂鸣器报警,闸门不开。

2 硬件电路设计

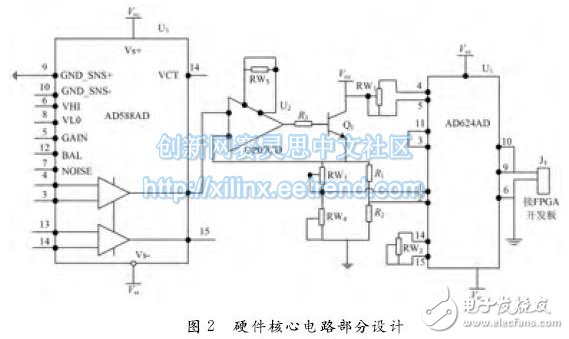

2.1 传感电路设计

2.2 调理电路设计

2.3 其他应硬件电路

继电器控制电路是控制小车电机前后运动,闸门控制电路实际上也是继电器驱动电路,控制门的开关,而蜂鸣器电路只需一点三极管驱动即可,这三个电路均选用经典常用的电路,不在赘述。

3 软件部分设计与实现

3.1 软件设计流程图

软件设计根据功能模块划分,采用实时并行控制方式,FPGA的程序在ISE13.3集成环境下进行的,可以使用原理图输入方式、文本输入方式、模块输入方式和EDA设计输入工具等表达电路构造思想。本系统采用常用的Verilog HDL语言文本输入来描述系统的功能。软件采用自顶向下的设计方法,有利于从整体上规划系统的功能和性能,方便调试和以后的维护。随着设计层次向下深入,系统的参数进一步细化和确认,并且随时可以根据设计的改动加以调整,便于分配各个功能模块的任务,从而保证设计的正确性,缩短设计周期。

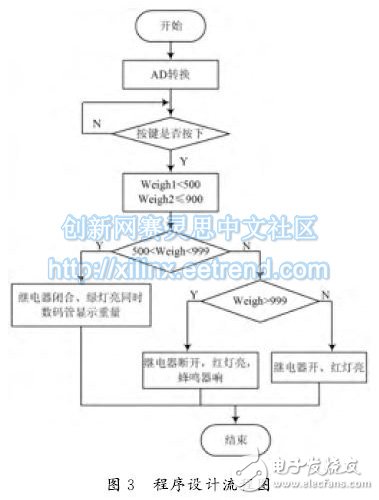

系统软件程序流程图如图3所示。

首先把从调理电路接受的信号,进行A/D转换,此时,若按键没有按下,则处于等待状态,若按下则进行重量范围边界值输入并判定重量范围,若在范围内则进行继电器闭合以开启闸门、绿灯亮表示小车能够通过,并同时显示小车重量;若在范围之外,则进行第二次范围判定,判定是否超载还是重量不足,若超载则继电器保持断开,红灯亮和蜂鸣器响双报警,若重量不足只进行红灯亮报警,蜂鸣器不响,且闸门不开。

3.2 程序仿真运行

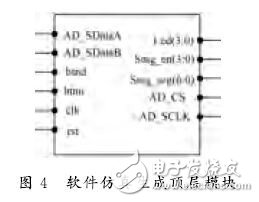

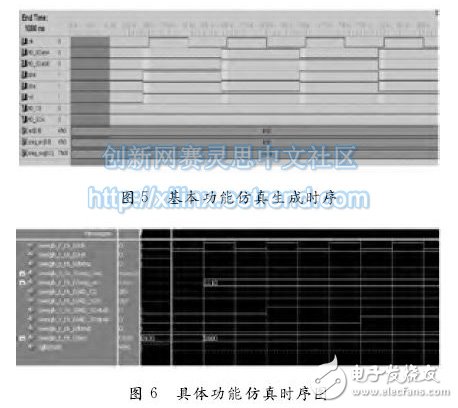

把电脑接上XC6SLX16-3CSG324板卡,该板卡接上小车,系统上电或复位之后,初始化时主要对板卡内部的相关存储器、寄存器、控制指令数据和端口进行初始化,初始化完成后,进行时钟分频设置,这里主要对芯片时钟和A/D时钟设置,图4是仿真生成的顶层模块图,clk和AD_sclk为芯片时钟和A/D 时钟;btnd和btnu为上下限设置参数,该参数可以人为设置和修改,其他管脚如图,不再说明;由图4说明改程序设计正确,编译通过,接下来主要看功能能否实现。接下来仿真生成内部模块,每个模块对应一个程序源代码;接着对每个子模块对应程序做时序仿真,图5是程序初始化的时序图,该图是没有输入重量多少时的时序图,从图上可以看出,A/D的时序表示0,这里主要验证数码管是否显示为0,芯片时钟能否正常工作,程序能否下载到板卡并成功控制小车等基础控制部分。在基础部分完成后对系统各部分进行仿真验证,这里仅介绍输入一个重要的A/D仿真时序,如图6所示,在输入重量为0100时,整个电路时序和A/D的时序输出正常,在重量大于500g和低于1g两条警戒线为红色,没有输出。与实际设想吻合。

4 结 语

笔者尝试利用FPGA 方法设计一种智能电子衡器,在软硬两个方面进行设计,并进行了仿真和实践。该衡器针对目前我国普遍利用单片机开发设计智能电子衡器的现状而设计的,为智能电子衡器的开发提供一种参考。

- 相关推荐

- 热点推荐

- FPGA

-

电子衡器的工作原理是什么?2020-03-09 1252

-

电子衡器使用和维护2009-12-25 862

-

电子衡器如何选用传感器2012-03-08 808

-

电子衡器基础知识及接口静电保护2018-06-22 831

-

基于RS-232应用接口下的电子衡器2018-07-13 1012

-

称重传感器的应用及选择2019-10-07 4124

-

电子衡器接口静电保护元件推荐2020-03-15 2128

-

数字式智能称重传感器的应用2020-06-10 3857

-

如何选择微型称重传感器2020-07-16 1460

-

称重传感器的选择和使用解析2020-07-17 2061

-

电子衡器的PCB原理图免费下载2020-10-10 740

-

如何挑选合适的称重传感器2021-08-24 4565

-

称重传感器怎么选型2022-02-04 2374

-

智能称重物联网实现电子衡器云端监控与管理2023-04-21 1375

-

激光焊接技术在汽车电子衡器中的应用2025-03-28 1174

全部0条评论

快来发表一下你的评论吧 !