基于CPLD的FPGA快速动态重构设计

FPGA/ASIC技术

描述

摘 要: 随着FPGA的广泛应用, 其实现的功能也越来越多, FPGA 的动态重构设计就显得愈发重要。在分析Xilinx Vertex II Pro系列FPGA配置流程、时序要求的基础上, 设计了基于CPLD 的FPGA 快速动态重构方案, 实现了同一硬件平台下多个FPGA 设计版本的在线动态配置和功能重构, 该技术已在工程中成功应用。

1 引 言

软件无线电( SDR )的设计思想已成为现今通信的热点, 它以通用、标准、模块化的硬件处理平台为依托, 通过软件编程来实现无线电台的各种功能。硬件处理平台设计为通信系统的关键之一,通用性是其首要考虑的问题, 因为只有具有通用性,才能用软件实现多种功能。由于FPGA ( Field Programmable Gate Array)的现场可编程特性, 故目前硬件处理平台的设计基本上都采用了FPGA + CPU 的架构, FPGA主要用来完成并行和高速处理的功能。

随着微电子技术的发展, FPGA 可提供的资源日益强大, 达到上千万门级, 其承担的功能越来越多, 同时, 电子设备对成本、功耗和体积的要求也越来越高, 矛盾就不可避免地产生。通过实时地动态重新配置FPGA 来加载不同的功能软件, 实现功能切换, 是解决此问题的较好方法, 可实现几者之间的均衡。目前, 实现FPGA 动态重新配置比较通用的方法有两种: 一是通过DSP或其它CPU 读取存储器中的比特( bit)文件对FPGA 进行串行加载或并行加载, 其缺点是加载速率一般很低, 不能实现状态高速切换; 二是使用Xilinx 公司的专用配置芯片XCFxxP系列, 但由于其存储容量有限, 对于功能复杂的系统, FPGA 的软件版本多, 需要多片专用配置芯片, 不适用于印制板尺寸很小、布局紧张的场合。

针对上述问题, 本文提出了基于CPLD的FPGA快速动态加载方案, 实现了FPGA 的功能重构, 克服了上述两种方式的缺点。

2 Vertex II Pro的配置流程

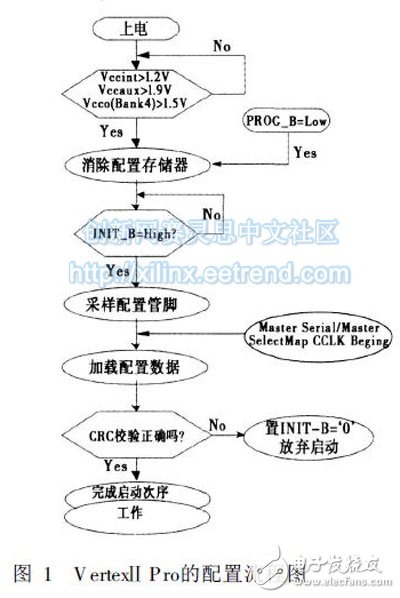

Xilinx 公司的FPGA 配置存储器是易失性的 , 每次上电时都要将存储在外部存储器中的位流文件加载到FPGA中才能正常工作。其配置过程主要有4个阶段: 清除配置存储器、初始化、加载配置数据、器件启动 , 其流程如图1所示。

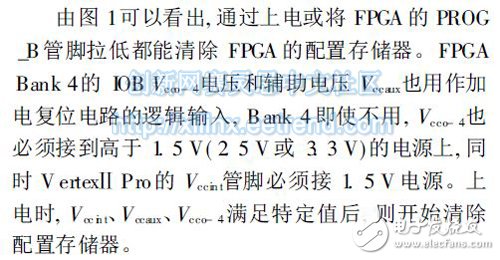

配置存储器清除阶段, IN IT _B 和DONE 管脚变低。当配置存储器清除完毕后, IN IT _B 管脚变高。如果通过拉低PROG _B 管脚来清除配置存储器, 则PROG _B 的低脉冲时间至少大于300 ns, 无最大值。上电时序如图2所示。

2. 2 初始化

在初始化阶段, FPGA 首先释放对IN IT_B 的控制权。此时, 如果外部将IN IT _B 拉低, FPGA 将延迟配置进程, IN IT _B上升沿采样配置方式管脚M0、M1、M2, 根据不同的配置方式, 开始配置进程。在此期间, 不需要暂停时间或等待周期, 但IN IT _B 变高后, 也不会立即开始配置, 需要FPGA 从位流文件中收到同步字后, 其配置逻辑才开始处理数据。

2. 3 加载配置数据

内部配置存储器被分成叫做“帧”的块, 真正写进配置存储器的位流部分叫做"数据帧", "帧"的大小和数量随器件而变。一旦配置进程开始, FPGA接收数据帧, 最后一个数据帧接收完后进行CRC 校验。当CRC校验出错, FPGA 将IN IT _B 管脚置低,指示CRC 出错, 同时FPGA 放弃配置进程, 不启动工作, 直至PROG _B变低来重新复位配置逻辑; CRC校验正确, 最后一个数据帧下载后, 将给全局复位信号( GSR)一个脉冲, 它将在进入启动之前复位器件内的全部寄存器。

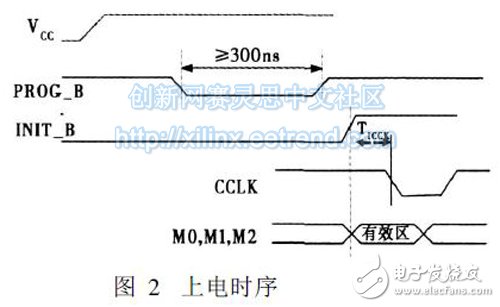

2. 4 器件启动

启动是配置的最后一个阶段, 是从配置状态到工作状态的一个转换过程, 如图3所示。启动次序是0~ 7的一个8段序列状态机, 可以用软件改变次序, 该阶段完成以下任务: 释放DONE 管脚; 撤消GTS, 激活所有的I/O; 使能GWE, 允许所有的RAM和触发器改变状态; 使能EOS, 启动结束标志总是设在第7段, 其为内部标志, 用户无法介入。

3 CPLD动态配置FPGA的方法

Vertex II Pro 系列有4 种配置模式: 主串行模式、主并行模式、从串行模式和从并行模式。其中主从指的是配置时钟的方向, 主模式配置时钟由FPGA内部振荡器产生, 从模式则由外部提供配置时钟; 串行是指配置数据逐位传输, 并行是指配置数据以字节传输。为了便于有效地控制配置流程和快速加载, 这里选择从并行模式。

FPGA 最后生成的执行文件有二进制和ASC II文本形式两种。为了便于烧写进FLASH, 方案选择生成ASC II文本形式的位流文件, 它是用ASCII码0或1表示生成的设计文件中的0或1信息。

整个步骤如下:

( 1)将多个设计文件版本按照分配好的地址烧写入FLASH;

( 2) CPLD 内部的控制逻辑首先将FPGA 的PROG_B管脚拉低必要的时间, 清除FPGA 中配置存储器的内容, 同时在PROG _B 变高后继续拉低FPGA 的IN IT _B 一段必要的时间然后置高, 采样配置方式管脚M0、M1、M2;

( 3)接着CPLD 中的地址产生器输出当前版本的起始地址, 对FLASH 进行读操作, 从FLASH 中读取的数据在配置时钟的作用下输给FPGA 的数据配置管脚, 然后FLASH 的文件地址加1, 这样依次将数据输给FPGA, 直至配置过程结束;

( 4)配置数据输完后, 如果CRC 校验正确, FPGA则进入启动阶段, FPGA 的DONE 信号变高, 结束CPLD 内部的配置程序, FPGA 进入工作状态;

( 5)如果CRC 校验不正确, FPGA 拉低IN IT_B,放弃配置, 这时CPLD会检测到IN IT_B 信号的下降沿, 复位配置程序, 并将FPGA的PROG_B 管脚再次拉低, 重新开始配置。

配置过程中, 最大频率主要由FLASH的读取时间和数据输入的建立时间决定。FLASH 的读取时间一般远远大于数据输入的建立时间, 因此它是造成配置速率不能提高的瓶颈, 从而也决定了最大配置频率。目前FLASH 的随机读取时间通常为70~90 ns, 因此FPGA 的最大配置频率在10MHz左右。

4 应 用

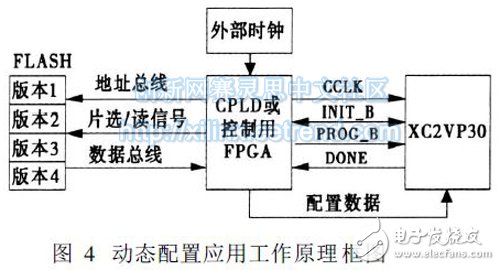

在工程中, 利用大容量FLASH 芯片和CPLD成功实现了对300万门FPGA XC2VP30 的动态加载,其实现方法是将FPGA 的加载模式设为从并模式,加载版本设为4个, 利用DSP事先将4个软件版本烧写进FLASH。

设计采用一片CPLD来控制XC2VP30的配置逻辑和版本管理。当DSP收到外部送来的模式切换命令后确定加载版本, 然后送给CPLD版本切换信号和所需的版本信息。这时CPLD 启动配置逻辑程序对FPGA进行加载。加载过程中, 如果CRC 校验出错, IN IT_B变低, CPLD检测到INIT_B下降沿后重新加载FPGA。如果连续检测到5个INIT_B 下降沿, CPLD放弃加载, 上报错误信息。其工作原理如图4所示。

在本应用中, FPGA 的加载时钟选择的是10MHz, 而XC2VP30 的配置位流文件大小为11589984 bit, 完成一次加载的时间大约需要145ms。测试表明, 本加载方法稳定可靠, 性能良好。

5 小 结

本文设计的基于CPLD的FPGA 快速动态重构方法, 加载速度明显快于DSP或其它CPU 上秒的加载速度。由于FLASH 具有容量大封装小的特点, 使这种配置方法在小型化硬件平台设计中占有优势,而且以后随着FLASH 读取时间的缩短和FPGA 配置数据位数的扩展, 加载时间会大大地缩短, 更能满足设计要求。同时, 这种方法不依赖国外专用配置芯片, 提高了硬件设计灵活性。

-

FPGA动态可重构技术是什么,局部动态可重构的时序问题解决方案2021-07-05 4625

-

怎么实现基于FPGA的动态可重构系统设计?2021-05-10 3037

-

如何去实现FPGA动态部分的重构?2021-04-29 4026

-

采用模块化设计实现基于FPGA的动态可重构功能2020-07-29 2946

-

如何在FPGA动态部分重构功能设计中进行模块化设计?2019-09-20 2592

-

如何采用FPGA部分动态可重构方法设计信号解调系统?2019-09-05 1803

-

有什么FPGA可重构方法可以对EPCS在线编程?2019-07-31 2470

-

如何在FPGA动态局部可重构中进行TBUF总线宏设计2018-12-14 1480

-

采用ARM和CPLD结构的检测系统可重构设计方法2018-10-20 2678

-

可重构技术分析及动态可重构系统设计2017-11-25 14686

-

基于动态重构技术和GSM通信的FPGA动态配置2015-02-05 2609

-

FPGA可重构设计的结构基础2011-05-27 4004

-

划分和时延驱动的动态可重构FPGA在线布局算法2010-01-18 515

-

基于SRAM编程技术的PLD核心可重构电路结构设计2009-11-30 623

全部0条评论

快来发表一下你的评论吧 !