Zynq器件三种主要类型的存储控制接口解析

FPGA/ASIC技术

描述

基于Zynq器件的嵌入式开发时,我们不可避免地需要规划设计使用什么样类型和多大地内存与FLASH,本文就ZYNQ器件的存储控制器作一个抛砖引玉的描述,以期大家对它有个基本了解,如有不当或需要补充之处欢迎大家发言指出。

Zynq器件主要包括三种类型的存储控制接口:

① DDR控制器,主要特性如下:

·支持DDR3、DDR2、LPDDR2;

·支持位宽为16比特或32比特,位宽为16比特时支持ECC。

·使用多达73个PS专用引脚。

·模块支持:32比特位宽:4 x 8b, 2 x 16b, 1 x 32b

16比特位宽:2 x 8b, 1x 16b

·1.5v的DDR3最大速率支持到533 MHz(DDR1333)

·1.8v的DDR2最大速率支持到400 MHz(DDR800)

·1.2v的LPDDR2最大速率支持到400 MHz(DDR800)

·具有4个DDR控制端口,1个给PS专用,2个PL专用,1个外设/DMA/PL/PS共享。

·不支持DIMM

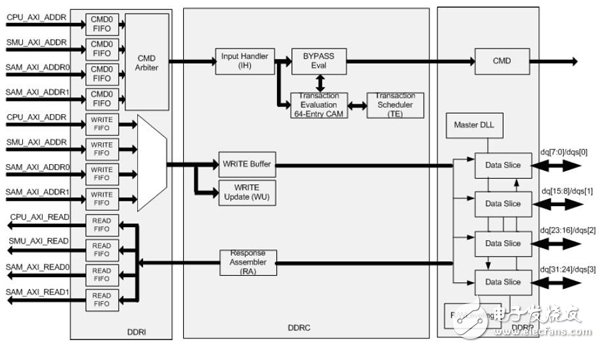

DDR控制器的框图如下:

主要包括三部分:

·DDRController Interface (DDRI),负责各个端口的读写请求和仲裁。

·DDR Controller Core (DDRC),负责对读写交易进行调度和排队。

·DDRController PHY (DDRP),物理层,直接和DDR3,DDR2,LPDDR2器件通信。

② Quad‐SPI控制器,主要特性如下:

·100 MHz32-bit APB 3.0接口支持各种操作,如读,写,搽除等操作。

·100 MHz32-bit AXI读接口时地址线性映射。

·读操作时支持x1, x2 和x4速度。

·写操作时支持x1和x4速度。

·主模式下最大SPI时钟达到100MHz。

·带有252字节的FIFO以最大化Quad‐SPI读效率。

·支持最大容量为128Mb的Quad‐SPI器件。

·支持两个Quad‐SPI器件并行使用。

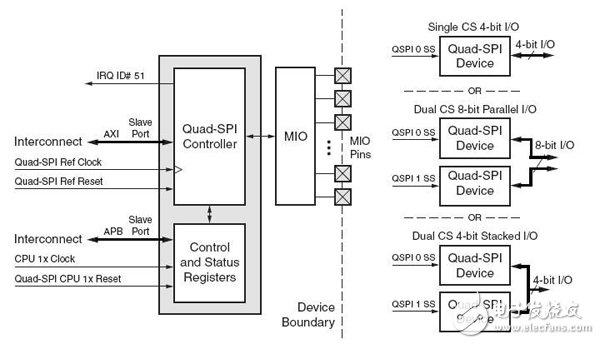

Quad‐SPI控制器是系统外设互连(IOP)的一部分,如下图示可以支持一到两个QSPI FLASH:

注意当使用一个Quad‐SPI器件时,只能使用QSPI0,使用两个Quad‐SPI器件时,要保证器件是同样的(生产商和通信协议)。

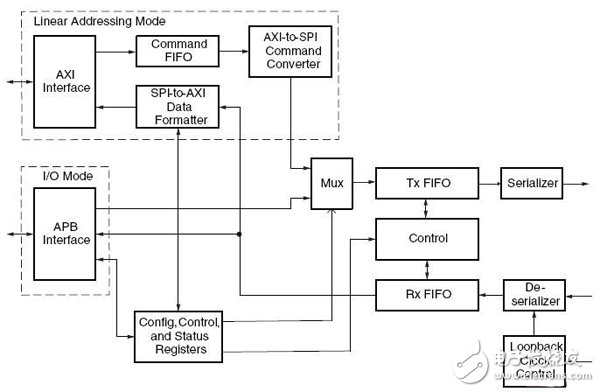

Quad‐SPI控制器有两种基本的使用模式:I/O模式和线性地址模式。

I/O模式:控制器只负责收发数据,需要软件开发者熟悉FLASH器件的通信协议,软件用四个TXD寄存器来写数据和命令,从FLASH读回来的数据存储在一个接收寄存器。这种模式支持FLASH器件的所有操作,如读操作,写操作和搽除操作。

线性地址模式:这种模式消除了I/O模式需要软件开发者自行发出读写命令的开销,线性地址模式下由硬件发出对FLASH的读命令并控制数据流向AXI总线接口,控制器响应AXI总线接口的请求,这仿佛把FLASH当作ROM存储器来操作,开发者不用关心低层细节,这种模式常用于直接在FLASH上执行代码的情形。

Quad‐SPI控制器的框图如下:

③ 静态存储控制器(Static Memory Controller (SMC)),能支持NAND Flash, NORFlash和SRAM。

NANDFlash控制器主要特性如下:

·支持8比特或16比特的数据宽度。

·符合ONFI specification 1.0标准

·16-word的读和写FIFO

·8-word的命令FIFO

·可编程的I/O周期时序

·ECC功能

·异步存储器操作模式

Parallel SRAM/NOR控制器主要特性如下:

·8比特数据宽度,支持最大25个地址线。

·2个片选信号(24位地址模式)

·16-word的读和写FIFO

·8-word的命令FIFO

·可编程的I/O周期时序,两个片选信号可分别设置

·异步存储器操作模式

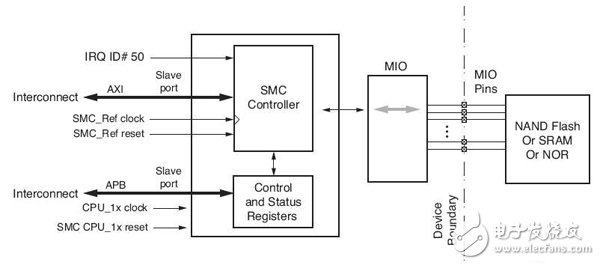

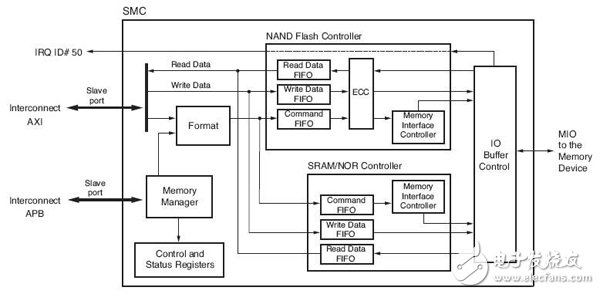

系统总线可以访问到静态存储控制器SMC,但SMC的控制寄存器只能提过APB接口访问,如下图示:

注意使用SMC时可能占用比较多的MIO引脚,需要规划好防止引脚冲突。

静态存储控制器(SMC)的框图如下:

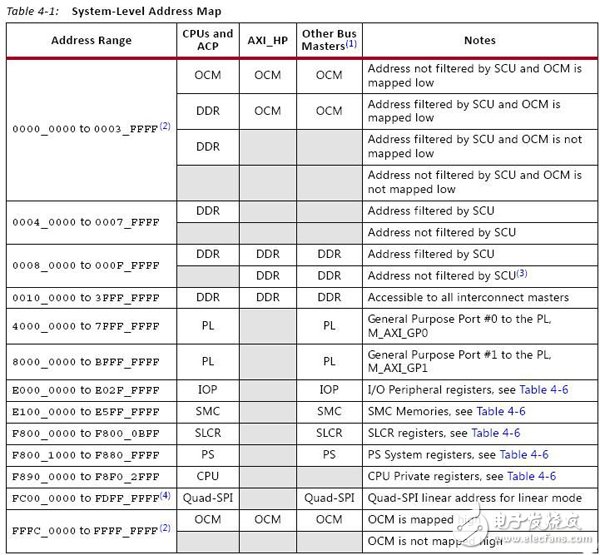

最后给出Zynq器件的存储地址分配表:

-

差分晶振的输出波形解析:三种类型要知道2024-01-24 2642

-

运动控制的三种控制方式2024-01-23 3320

-

异步电机主要的三种调速方法解析2024-01-07 4561

-

常见的socket三种类型2023-12-08 3906

-

伺服电机控制器的是三种类型介绍2023-11-19 1954

-

实现可编程逻辑电路的三种主要器件2022-09-08 5916

-

FPGAs,Zynq和Zynq MPSoC器件的特点2022-08-15 4116

-

编译的三种类型是什么?2021-12-24 1386

-

STM32的三种复位类型2021-08-02 3620

-

进程类型及三种状态2021-04-02 1790

-

verilog中端口类型有哪三种_verilog语言入门教程2020-08-27 12018

-

浅谈Zynq Qspi控制器的三种模式2018-07-02 21792

-

三种加密器件的熟悉2016-08-24 3641

-

三种SMA接口pcb封装2016-01-25 95493

全部0条评论

快来发表一下你的评论吧 !