基于MSP430的三线串行接口通信系统

FPGA/ASIC技术

描述

摘要:通过研究三线串行接口的构成原理, 设计了一种基于MSP430 单片机和FPGA 的三线串行接口测试仪。该测试仪利用MSP430 单片机来控制三线传输功能,由FPGA 产生三线传输时序,由相应的上位机软件来测试数据通信。经测试,该测试仪具有使用方便、功能齐全、性能稳定等特点, 能够较好应用于航天领域的三线串行接口通信测试中。

三线串行接口是一种广泛应用在航天工程领域的简单串行通信接口, 是航天单机产品遥测遥控通信链路的重要环节。三线串行接口具有电路简单、时序便于实现、波特率可调等诸多优点。

传统三线串行接口的设计一般是采用数字电路搭接而成, 虽然能满足工程设计要求, 但是体积较大, 耗费资源过多, 而且灵活性欠佳。为了对三线串行接口电路进行优化, 同时对三线串行通信进行测试, 本设计采用FPGA 技术设计了三线串行接口的时序电路, 将三线时序功能集成到单片FPGA中, 大大减小了电路单元体积。同时, 采用单片机MSP430 来控制FPGA 中产生的三线串行时序, 单片机通过RS232C 通信方式与PC 进行通信, 进而在上位机软件中直接配置三线串行接口的时序参数和通信数据, 使得测试三线串行接口通信的方便性和灵活性大大增强。

1 三线串行通信原理

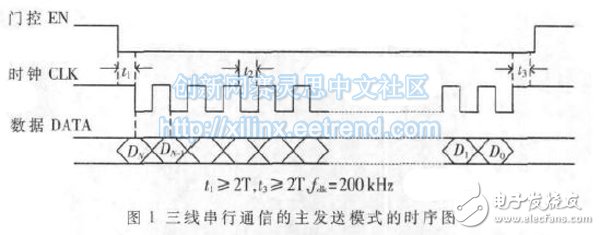

三线串行接口通信是一种主从同步串行通信, 其数据发送端和接收端有共同的时钟源, 数据接收端采用光耦隔离, 一般时钟频率在100 kHz~1 MHz 之间。三线串行接口有门控信号EN、时钟信号CLK、串行数据信号DATA 三根信号线。三线串行接口包括发送和接收两种工作模式, 图1 给出了三线串行通信发送模式的一种时序图。

门控信号EN 的下降沿表明一次数据传输的开始,之后保持低电平有效, 数据在时钟信号的下降沿采样,每个时钟周期接收或者发送一位串行数据, 直到数据发送完成。在数据发送或接收的整个过程中, 门控信号一直处于低电平不变。

2 三线串行接口测试仪的总体方案设计

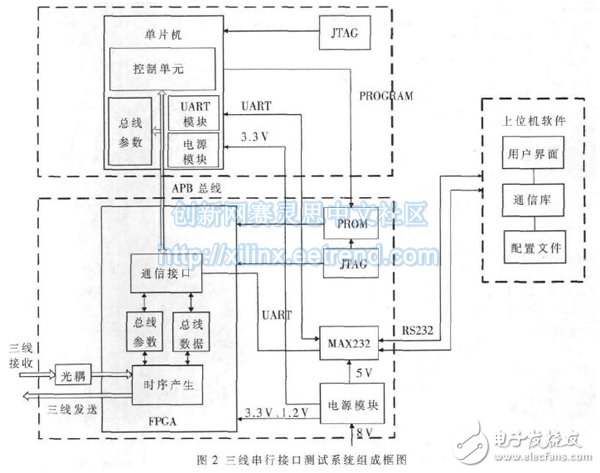

本设计将三线串行接口测试仪划分为三大功能单元:FPGA 时序产生单元、MSP430 控制单元、上位机软件单元。图2 是三线串行接口测试仪的总体方案设计框图。

FPGA 时序单元主要用于产生三线串行时序, 选用Xilinx 公司的Spartan-3A 系列FPGA, 其上电配置由一片PROM 来实现。FPGA 时序单元通过Verilog 语言编写的有限状态机来实现各种时序, 有限状态机属于一种时序逻辑电路, 是协调相关信号动作、完成特定操作的控制中心[ 3]。有限状态机一般由三部分组成: 当前状态、下一状态和输出逻辑。本设计采用摩尔型有限状态机来实现各种模式的三线接口时序, 所谓摩尔型状态机指输出值与当前的状态有关, 与当前的输入无关。

MSP430 控制单元主要用于对FPGA 的各种功能模块进行控制, 通过APB 总线的方式访问FPGA 内部的寄存器来实现。单片机通过C 语言编程的方式灵活地修改各个时序参数, 并和上位机软件进行通信。

上位机软件采用微软公司的VC++ 集成开发环境开发, 本设计将软件划分成几个小功能模块, 并将部分模块做成动态链接库的形式供主程序调用。上位机软件主要包括主接收程序、数据发送程序、三线串行接口配置程序、RS232 通信动态链接库。

此外, 电路中用到了多组电源,FPGA 供电电压为1.2 V, 单片机供电电压为3.3 V, 三线串行接口的数据接收端一般需要光耦隔离, 本设计选用的是5 V 供电的光耦,RS232 通信芯片也是5 V 供电, 所有这些电压都由相应的电源芯片直接产生。

3 三线串行接口测试仪设计方案的实现

3.1 三线串行接口时序产生单元的FPGA 实现

设计的三线串行接口电路要求能够实现三线串行时序, 同时要求具备时序参数( 比如时钟频率、采样方式等) 可调、数据收发等功能, 根据上述目标, 本设计将FPGA 时序产生单元划分成以下几个模块:three -wireregister interface ( 三线寄存器接口模块)、three-wire send( 三线发送模块)、three -wire receive ( 三线接收模块) 和three-wire clock( 三线时钟产生模块)。

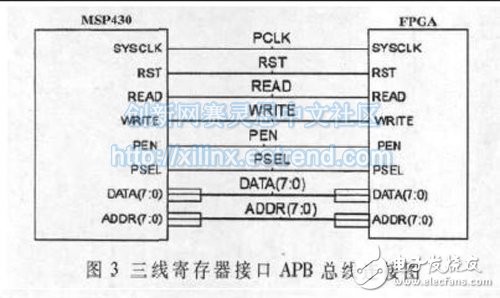

Three-wire register interface : 该模块主要用于FPGA与单片机MSP430 的通信。本设计将FPGA 当作一个外部设备挂接在MSP430 的I/O 端口,MSP430 控制I/O 端口通过特定的总线时序来访问FPGA 内部的配置寄存器。总线时序采用APB 总线时序。APB 总线是ARM 体系结构里片内芯片互联的一种高性能总线, 其控制信号线包括: 复位信号RST、系统时钟SYSCLK、读信号READ、写信号WRITE、片选信号PSEL、使能信号PEN,另外还包括一个8 位的地址总线ADDR[7:0] 和8 位数据总线DATA[7:0]。图3 给出了三线寄存器接口APB总线连接图。

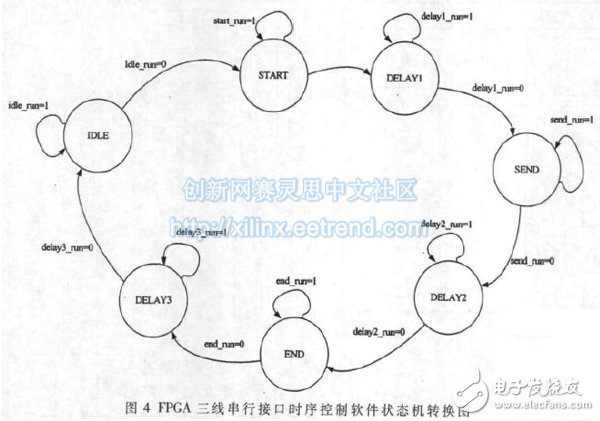

Three-wire send : 该模块主要用于三线串行接口发送数据时的时序产生, 三线发送模块时序采用摩尔型状态机实现, 该状态机共有7 个状态:IDLE 状态、START状态、DELAY1 状态、SEND 状态、DELAY2 状态、END 状态和DELAY3 状态, 各个具体状态转换如图4 所示。

每个状态都有一个状态指示控制信号, 以SEND 状态为例, 其指示控制信号为send_run 。当状态机进入SEND 状态后,send_run 变为1 , 然后SEND 状态的电路开始工作。当该电路执行完毕后会将send_run 变为0时, 表明退出SEND 状态, 状态机进入下一状态。其余状态类似。各状态定义如下:

IDLE 状态, 为空闲等待状态, 即系统上电后的状态机的初始状态, 当系统完成初始化或者完成一次完整的时序功能后状态机都会返回IDLE 状态。

START 状态, 表示三线串行通信开始, 在检测到三线串行接口的使能数据线EN 有效后状态机进入到START 状态。

DELAY1 状态, 表示三线串行通信数据使能后, 时钟信号相对使能信号的延迟时间, 该状态实际上起到一个延时的作用。

SEND 状态, 表示三线串行通信数据开始发送, 该状态下三线串行数据将开始移位发送。

DELAY2 状态, 表示三线串行通信数据发送完一个字节后的间隔时间,该状态实际上起到一个延时的作用。

END 状态, 这是表示三线串行通信数据发送结束。

DELAY3 状态, 这是表示三线串行通信数据发送结束后, 使能信号变成无效后相对最后一个时钟触发沿的延迟时间。

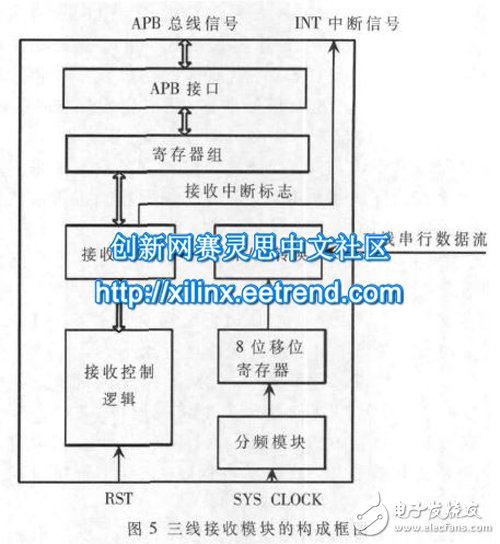

Three-wire receive : 当三线串行接口的使能信号线有效后( 高电平有效或低电平有效) , 在同步时钟的触发下( 上升沿或下降沿) 对数据信号线进行采样, 采样得到的数据位经过一个8 位移位寄存器实现串/并转换, 转换后的8 位并行数据存放到接收FIFO 中。接收FIFO 的大小为128 B, 接收FIFO 的使用使得三线串行接口具备了数据缓存功能, 不必担心单片机和FPGA 接口速度匹配问题导致的数据丢失。当三线串行接口的使能信号由有效变成无效时,接收模块向系统发送“ 三线数据接收结束” 中断, 该中断信号直接与单片机的外部中断连接, 从而单片机可以快速响应该中断通过APB 总线读取接收FIFO 中的数据。图5 是三线接收模块的构成框图。

Three-wire clock 三线时钟模块:

该模块实际上是一个时钟分频模块。由于FPGA 系统采用的系统时钟频率为50 MHz , 本设计需要的三线串行模块的时钟频率是由系统时钟频率经分频得到[ 5]。为了实现可调的三线时钟频率, 要求分频系数可调。分频系数存储于一个32 bit 的分频寄存器中, 通过三线串行接口模块中的寄存器配置能修改该分频系数。

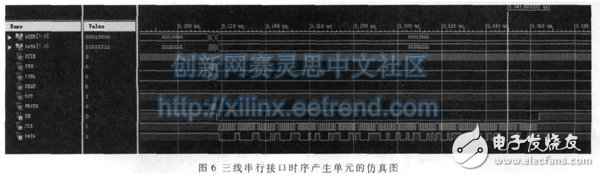

通过ISE 自带的ISim 仿真器对三线串行接口时序产生单元做了功能仿真, 仿真图如图6 所示。

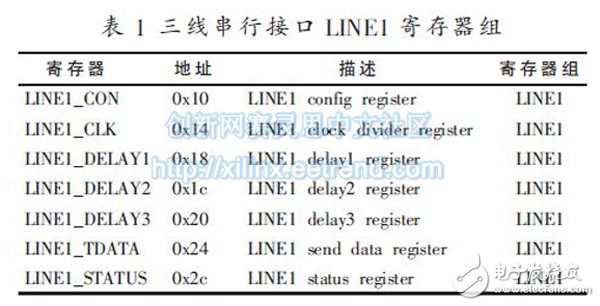

3.2 单片机控制三线串行接口寄存器

MSP430 单片机在测试仪中起到控制和配置三线串行通信参数的作用, 这是通过单片机读写APB 总线上挂接的三线串行接口配置寄存器组来实现的。本设计自行定义了配置寄存器的地址和功能。以三线串行接口LINE1 寄存器组为例来介绍配置寄存器:LINE1 寄存器组包括了发送相关的7 个寄存器, 分别用于控制三线串行接口的发送参数。如表1 所示,LINE1_CLK 寄存器是一个32 位的寄存器, 其访问地址为0x14 , 属于LINE1 寄存器组, 通过配置LINE1_CLK 寄存器可以很容易调整三线串行接口的时钟频率, 其调整范围可以从0~1 MHz, 这可以通过调整分频系数寄存器来计算。

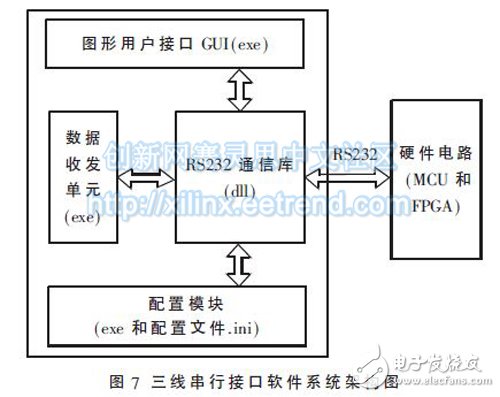

3.3 上位机软件设计

上位机软件主要划分成几个模块: 数据收发单元、配置文件、RS232 通信动态链接库、图形用户接口。其中图形用户接口是软件的主程序, 在该程序中可以调用其他程序[ 6]。比如可以调用数据发送程序来发送三线串行数据, 也可以调用配置程序来配置三线串行接口的通信参数等。图7 是上位机软件的系统架构图。

三线串行接口配置软件功能包括调整三线串行总线频率f、调整三线时序中的t1、t2、t3以及总线信息设置等。三线发送软件功能包括数据发送的模式和方式, 如手动发送、自动发送等模式, 以ASCII 或HEX 方式发送等。

本文通过介绍三线串行接口通信原理, 给出了三线串行通信接口测试仪的硬件电路和软件设计。针对传统三线串行接口电路资源占用过多且不够灵活的缺点,构建了基于MSP430 单片机和FPGA 的三线串行通信测试仪, 详述了其组成模块及工作方式。本方案设计合理可行, 优点突出, 满足了实际应用要求。目前, 此测试仪已研制出样机并成功应用于某航天型号项目的通信测试平台中。

-

MSP430与PC机的远程通信及液晶显示2018-11-27 2182

-

MSP430系列教程之PWM波串行接口2021-09-01 1520

-

MSP430串行通信的相关资料推荐2022-02-15 1022

-

利用捕获比较功能实现MSP430与微机串行通信的研究2009-11-27 1505

-

三线串行通信接口电路性能2017-08-30 996

-

基于MSP430和STM32无线通信系统的设计2017-09-25 1187

-

MSP430再三表中的应用2017-10-12 693

-

PC机与MSP430单片机串行通信的实现方法2017-10-13 1096

-

MSP430单片机的同步串行SPI多通道温度测试系统设计详析2018-04-24 1181

-

MSP430和FPGA的三线串行接口测试仪的设计详析2018-05-02 1173

-

如何使用MSP430单片机进行多机串口通信的设计2019-03-07 2637

-

MSP430单片机的通用串行通信接口详细资料说明2020-09-15 911

-

msp430中如何连续对位进行取反_MSP430系列通用串行通信模块的异步模式2021-12-14 658

-

基于MSP430的高速串行通信设计2023-10-30 375

-

MSP430 MCU上常见的eUSCI和USCI串行通信问题的解决方案2024-10-09 462

全部0条评论

快来发表一下你的评论吧 !