基于FPGA的NoC多核处理器的设计

FPGA/ASIC技术

描述

摘要:为了能够灵活地验证和实现自主设计的基于NoC的多核处理器,缩短NoC多核处理器的设计周期,提出了设计集成4片Virtex-6—550T FPGA的NoC多核处理器原型芯片设计/验证平台。分析和评估了NoC多核处理器的规模以及对FPGA硬件资源的需求,在此基础上给出了集成4片FPGA的开发板详细设计方案,并对各主要模块如互联架构、电源、板级时钟分布、接口技术、存储资源等关键设计要点进行阐述。描述了开发板各个主要模块的测试过程和结果,表明了该设计的可行性。

0 引 言

由于基于传统SoC (system-on-chip)的单芯片处理器在内核频率、片上通信、功耗以及面积等方面面临着很大问题,基于NoC (network-on-chip)的多核处理器应运而生,从体系架构上解决了前者所面临的诸多问题。NoC互连结构具有IP间的并行通信、扩展性好以及吞吐量大等优势,并且解决了多核处理器的体系结构问题以及困扰总线结构的全局时钟问题。因此,NoC互连结构是多核处理器系统最有前途的解决方案。

目前,FPGA芯片作为承载和验证基于NoC的多核处理器硬件设计的途径,已经成为了研究热点,但是随着硬件设计的规模不断增加,单片FGPA的硬件资源并不能满足基于NoC的多核处理器需求。因此,本文设计的验证平台采用了4片Xilinx公司的40nm Virtex-6系列中的XC6VLX550T (FF1759);该芯片具有将近50万的逻辑单元、840个最大可用I/0、内部信号可达600MHz、36组2.5Gbps高速吉比特收发器端口以及丰富的分布式RAM、Block ft 。由此观之,集成4片该型号FPGA芯片的开发板能够为FPGA硬件设计人员提供足够多硬件资源,以便验证和实现基于NoC的多核处理器的原型芯片设计,也为以后在片上网络(NoO 上研究多核并行计算提供了条件。

1 多FPGA开发板设计的总体方案

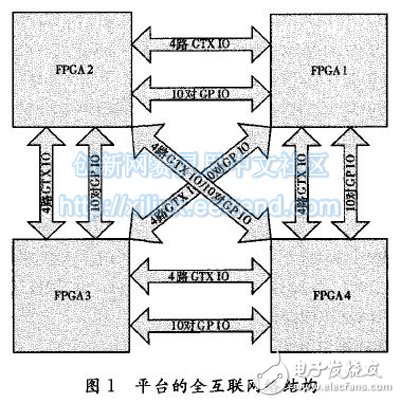

1.1 多FPGA的互联结构

该开发板总体架构如图1所示,平台上有4片Xilinx XC6VLX550T FPGA芯片,因此可以将需要处理的任务划分多个子任务分配到不同FPGA芯片上的处理单元分别处理,从而实现任务处理的并行化;其任务间数据通信速度和同步时间等不仅取决于处理单元本身的通信速度,还取决于链接处理单元的通信互联网络。所以本平台的4片芯片利用FPGA提供的全双工差分高速GTX接口(low-voltage diferential signaling,LVDS)_6]和单端模式的高速普通GPIOE ,实现片间的全互联网络结构;其中差分高速GTX接口的数据通信遵循Aurora协议,实现FPGA间的大量数据的高速传输,而单端模式的高速GPIO为FPGA开发人员提供自定义接口空间。

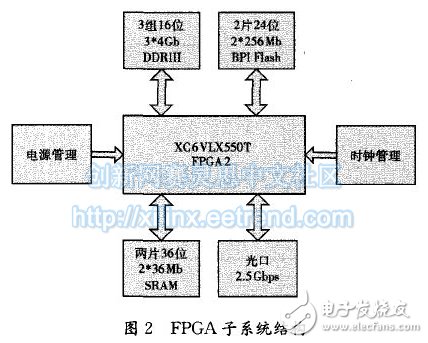

1.2 开发板的具体实现及其特点

该开发板的具体实现如下:3大组GTX 10 (每组GTX IO由4路独立的GTX IO通道构成)分别与另外3块FPGA芯片的对应GTX IO相连,提供64位宽,125MHz的数据传输通道,实现4块FPGA芯片的全互联,片间吞吐率达lOGbps;以及1O对单端模式的高速GPIO。每片FPGA子系统包如图2所示,含如下模块:电源管理模块、独立的存储系统、板级时钟管理模块、FPGA的配置方式以及对外对内的接口模块。该开发板具有以下特点:

(1)丰富的逻辑资源,4片FPGA 总逻辑资源:549888*4= 2199552。

(2)丰富的存储资源,24片DDR3共计48Gb,片外SRAM达到256Mb,片内RAM共计115.8Mb。

(3)存储端口吞吐率大:DDRIII 400MHz*16*12=76.8Gbps,片外SRAM 167 MHz*64*4= 42.752Gbps。

(4)FPGA设计灵活性、通用性强:可以采用不同的处理器,也可以采用相同的处理器,如ARM等。

(5)仿真综合软件支持好:第三方的Modelsim能很好地完成功能仿真,而Xilinx公司的ISE则能很好地完成综合。

2 开发板各模块具体设计方案

2.1 系统电源设计

为了能够承载更多的硬件设计,开发板在设计中使用了4片FPGA为处理核心。因此,系统的功耗要远远超出普通系统的设计要求。所以,能否设计出满足系统功耗需求的稳压电源成为系统能否正常运行的关键。通常,电源设计有两种实现方式:低压差线性稳压电源LIX)与开关电源(DC_DC)开关电源(DC-DC)。u)O的特点是电源精度高、噪声小,比较适合于精密电路供电,其缺点是输出功率往往不够大,并且功率的转换效率偏低[8]。I)C-DC的特点是功率转换效率高,能够提供较大的电源功率,但相比较LIND而言其电源噪声会有所提高,因此I)C-DC一般作为系统整体稳压电源使用或直接为大功率器件供电。

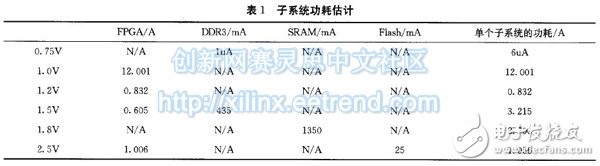

2.1.1 系统功耗估计

根据图1和图2可以得出系统的核心部分主要4片XC6VLX550T FPGA、24片DDR3 s亡IRAM、8片SRAM及8片NOR Flash,它们占据了系统功耗的主要部分。因此,主要对这部分的功耗进行大致上的估算,同时考虑到板上的其它器件,对估算的结果适当放宽,最终给出电源部分的具体设计参数。

本文对系统核心部份其中一个子系统所需的电压品种的对应的功耗进行了一个估算,参见表1。

表1的数据计算均参考每片芯片最大工作电流,为了提高电源的稳定性,本设计中电源的设计输出电流能力大于估算系统总功耗值的5O 系统总功耗即可,并对FPGA进行功耗估算时使用Xilinx公司的功耗计算工具XPE(XPower

estimator) 对FPGA的功耗进行估算,当FPGA内部时钟工作在100MHz时,使用了90 以上的内部资源,实际使用时一般不能用到所有的内部资源。

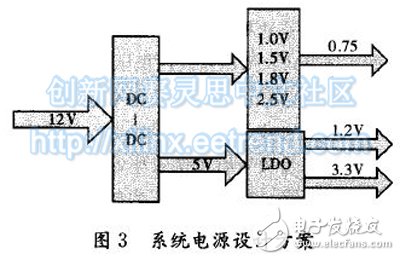

2.1.2 系统电源设计方案

为了使该系统更具稳定性和扩展性,本文设计的电源管理系统的带载能力至少是现有估计功耗的两倍。由于系统需要0.75V、1.0V、1.2V、1.5V、1.8V、2.5V 和3.3V稳压电源,考虑到整个系统的功耗,整个系统主要采用DC-DC这种效率高、输出功率大的开关电源,而局部功耗较小、精度要求高的部分电路则采用LDO线性稳压电源,充分结合开关电源与线性稳压电源各自的优势进行系统电源的设计。DC-DC开关电源的芯片采用了凌力尔特公司的LTM4601;整个系统的外部供电12V。本文设计的电源方案如图3所示。

因为1.OV、1.5V、1.8V及2.5V的电源所需电流较大,所以我们采用一个相位震荡器来并联两片LTM4601得到24A的电流输出,而其中的0.75V是DDR3所需的一个参考电压则通过1.5V分压得到;1.2V 和3.3V 通过LTM4601降到5V后通过一个LD0得到。

虽然采用的LTM4601的效率高,但是考虑到PCB板的空间以及有超过IOA的输出电流,整个系统的散热成为了考虑的关键。在进行PCB的版图设计时,尽可能的加大铺铜的面积,并每片FPGA上贴有散热片和风扇,以便系统散热。

2.2 板级时钟分布

基于SoC结构的处理器要求单一系统时钟全局同步工作,给设计带来了极大的困难。然而,基于NoC结构的多核处理器采用全局异步一局部同步的通讯机制,很好地解决了单一时钟同步问题,也为验证平台的时钟分布设计提供了便利。本文为每个FPGA子系统设计相应的时钟驱动,实现全局异步一局部同步的板级时钟分布。

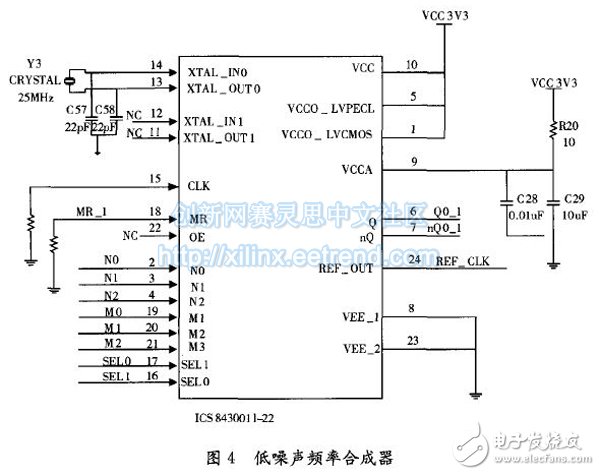

本文设计的多核处理器原型芯片设计的验证平台实现了两种RTC方案。一种是外接有源晶振,选用EPSON公司的EG-2101CA125M为整个系统的差分高速GTX接口提供125MHz的差分时钟驱动;另外一种是利用25MHz的无源晶振和ICS公司的低噪声频率合成器ICS8430011-22,通过配置和调节芯片可以精准的产生200MHz差分时钟,并通过时钟芯片ICS8543BGT分出4路提供给每片FPGA所挂载的DDR3的参考差分时钟,具体电路参见图4。第二种方式因为其时钟输出频率的可调节,使得其更具灵活性,也就为整个平台的通用性和可扩展性做好了铺垫。

虽然只提供两个外部时钟,可以利用FPGA芯片内部的PLL产生400MHz的DDR3工作时钟;100MHz系统时钟和SRAM 工作时钟。

2.3 系统接口设计

2.3.1 SDRAM DDR3接口设计

NoC多核处理器的各处理单元在进行并行处理任务时,需要快速存储和读取数据,避免各个处理单元处理数据时产生冲突,就需要提供数量足够多、数据传输带宽和存储空间足够大的存储器。因此,本文设计的平台采用数据存取频率能达到1333MHz DDR3芯片。

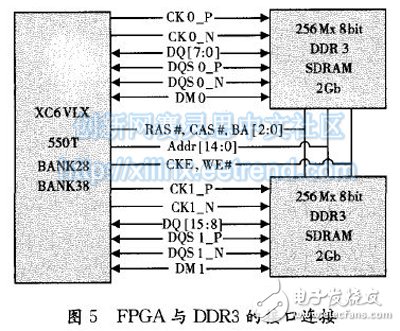

开发板的每片FGPA芯片外接有3组美光公司的容量为2Gb,单片位宽为8bit的MT41J256M8HX-15E (DDR3 1033)的存储器,由两片组成16bit宽度的数据总线。XC6VLX550T FPGA能够支持SSTL15电平标准,能够和DDR3 SDRAM进行无缝连接,FGPA与DDR3 SDRAM 的接口如图5所示。

图5中只是给出了其中一组DDR3与FPGA的连接,其所连接的FPGA BANK是通过Xilinx公司的官方软件ISE开发环境锁定得到。FPGA的不同BANK的电平标准,用户可以自己定义,本文在设计时是参考ISE生成的UCF文件来给各个BANK输入电源,比如BANK28和BANK38的VCCO使用1.5V的电源进行供电。两片DDR3芯片的数据、时钟、读写闪烁信号和数据掩码信号使用FPGA分别控制,地址和控制命令信号共享。

2.3.2 N0R Flash接口设计与FPGA的配置方式

FPGA是基于SRAM 架构来实现逻辑设计,所以在掉电后,编程信息立即丢失。芯片在每次加电时,都必须重新下载由设计文件生成的配置数据烧写文件。本系统每片FPGA芯片外接有两片相同的BPI NOR Flash,容量为256Mbit,位宽为16bit。其中的一片Flash接口在系统初始化过程中使用,当系统上电后或FPGA原型芯片复位键有效时,系统从片外的Flash加载硬件设计程序的bit文件到各个FPGA的本地程序存储器,实现对FPGA BPI方式的配置和编程;另外,在这一片Flash还用来加载软件程序设计的bit文件。

使用同一片BPI FLASH保存软件bit文件。BPI方式通过NOR型FLASH加载FPGA配置,无需Bootloader搬移FLASH中的应用软件bit文件,就可以直接运行。

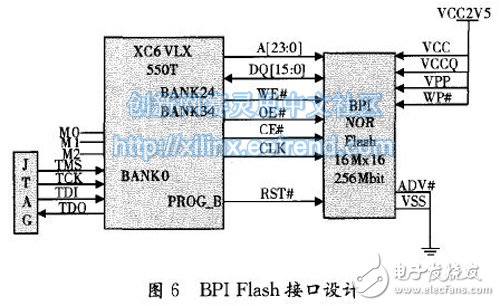

同样,XC6VLX550T FPGA能够支持LVCOMS2.5V电平标准,能够和NOR Flash进行无缝连接,FPGA 与NOR Flash的接口如图6所示。

图6中BPI Flash与FPGA相连两个是特定的BANK,分别是BANK24和BANK34;Flash的数据线和控制信号与FPGA BANK24相连,地址信号与BANK34相连,其中的复位信号与BANK0的PROG—B相连,硬件设计人员可以自行设定对应BANK的电平标准。

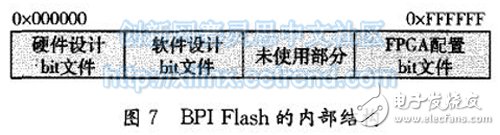

BPI方式中,M0,M1和M2配置管脚的设置,010和110都是BPI方式,当M0为0时,FPGA加载时由BPI Flash的OxO00000地址递增读取配置文件;MO为1时,FPGA加载时有BPI Flash的0xFFFFFF地址递减读取配置文件 ,如图7所示。

每片FPGA都是一个子系统,有可作为独立的模块独立工作,4片FPGA芯片相互独立,因此4片FPGA使用了相互独立的Flash。此外,在本系统中,4片FPGA芯片还连成传统的菊花链,以便可以通过JTAG链式并结合Xilinx的iMPACT软件配置FPGAl”],从而提高了系统的通用性。

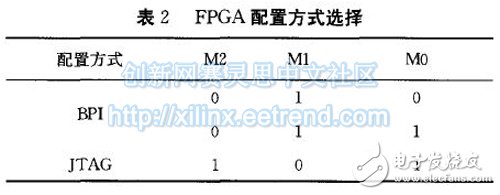

配置方式的选择:通过FPGA BANK0的M0,M1,M2进行配置方式的选择,本系统使用了两种配置方式:BPI和JTAG,管脚的设置如表2所示。

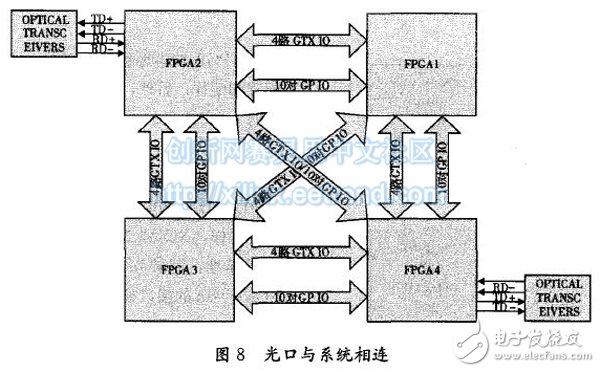

2.3.3 数据传输端口的设计

为了加大整个系统的数据吞吐率和更加合理的利用FPGA芯片的高速吉比特收发器,所以在FPGA2和FPGA4的BANK118各外接一个光纤接口,吞吐率可达2.5Gbps,比普通的千兆网口快了许多,从而增强了系统的实时性。光口与系统相连的情况如图8所示。

该系统数据处理的工作流程如下:待处理的数据通过前端数据传输接口(光口)在前端FPGA2进行处理,通过FPGA之间的高性能数据传输通道(LVDS)发送到后端的FPGA进行进一步处理,最后通过后端FPGA4传输到后向数据传输端口。4片FAGA实现流水线并行,能够很好的满足片上多核处理器并行性要求。

3 开发板调试实验过程和结果

在开发板制版和贴片结束之后,剩下的主要工作是完成开发板整体功能的调试和验证。作者主要从电源配置电路、核心系统电路以及接口电路等方面对开发板的各功能模块进行调试,并进行整体功能验证。目前,已顺利完成电源配置电路、4片FPGA互联结构、FPGA菊花链的加载电路、存储器接口电路等电路系统的调试实验工作。硬件设计的功能验证则由相关的硬件设计人员进行完成,开发板设计人员从旁辅助。开发板实物图如图9所示。

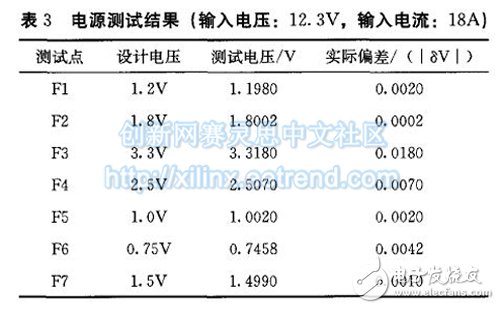

在测试电源管理模块的过程中,采用了线性直流稳压电源,型号是HK1000—11PEP(12V,18A)为开发板提供电源;采用了HP 33401A对开发板上个保险丝测试点进行各种电压的测试,测试结果如表3所示 表3的数据表明电源管理模块能够稳定正常的工作。

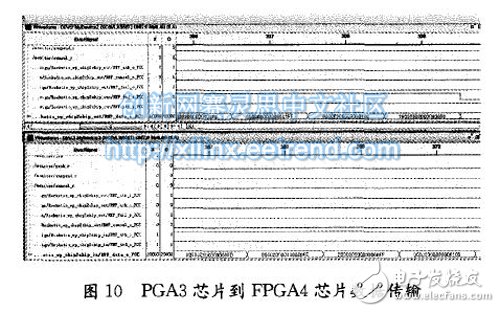

因为开发板是集成4片超大规模的FPGA芯片,所以4片芯片之间的互联能否正常通讯成为了本设计的关键芯片间互连是差分信号相互连接以完成通讯,并遵循Aurora Frame协议,在源芯片包链路传输接口端加入测试激励模块, 目的芯片包链路传输接口端加入监测器,其中设置数值比较模块,使用Xilinx公司的Chipscope软件观测控制信号波形的正确性,并通过比较模块测试数值正确性。图lO为FPGA3芯片到FPGA4芯片数据传输图,上半部分为发送端,下半部分为接收端,证明了FPGA芯片间通过GTX差分高速I()进行通讯的可行性。

至于FPGA菊花链的加载电路已经通过impact软件成功烧写Flash间接证明了链路能够正常工作;存储器接口电路则通过下载IP到开发板对应的FPGA芯片上,能成功地对存储器进行简单的读写数据。

4 结束语

本文设计并实现了基于4片Virtex-6 FPGA的NoC多核处理器原型芯片设计的验证平台。该平台具有超大规模的逻辑资源和丰富的数据存储带宽和空间,片间基于LVDS标准的无缝连接,支持高吞吐率和高速实时的数据传输能力,能够很好的满足片上网络(NoC)多核理器的要求。另外,该平台采用开关电源与线性稳压电源结合的方式,有效的保证了整个系统的供电_15]需要指出的是,系统设计时选用了多FPGA并行的基本设计构架,对未来研究片上网络(NoC)并行计算也有重要意义。

- 相关推荐

- 热点推荐

- FPGA

- xc6vlx550t

-

为什么有多核处理器?从多核到众核处理器2023-11-16 3139

-

多核处理器设计九大要素2011-04-13 3185

-

多核处理器的优点2019-06-20 5067

-

Linux的Spinlock在MIPS多核处理器中的设计与实2009-12-04 744

-

多核处理器架构及调试2010-08-26 1562

-

多核处理器及其对系统结构设计的影响2011-02-27 920

-

多核系统中NoC通讯架构的关键技术2013-01-24 10202

-

基于FPGA的嵌入式多核处理器及SUSAN算法并行化2016-08-30 672

-

多核处理器中的超越函数协处理器设计2017-01-07 885

-

多核处理器会取代FPGA吗?2017-02-11 1335

-

第1章 多核处理器基础2017-04-11 911

-

处理器关于多核概念与区别 多核处理器工作原理及优缺点2017-12-08 32839

-

浅议多核处理器技术2021-03-29 1133

-

Intel多核微处理器技术2021-04-09 1261

-

多核处理器的挑战,多核处理器结构与分类2022-12-05 1773

全部0条评论

快来发表一下你的评论吧 !