基于FPGA的反应堆控制保护系统的设计

FPGA/ASIC技术

描述

摘要:在基于现场可编程门阵列(FPGA)的反应堆控制保护系统设计中,针对各种电子设备的电磁干扰,通过在硬件设计中采用信号隔离、消噪、消激和阈值调节电路等抗干扰措施,并利用软件提高抗干扰能力,实现了电磁兼容性设计,为反应堆控制保护系统提供了较强的抗电磁干扰能力,确保了反应堆的安全、可靠和稳定运行。

1 引言

电磁兼容性是指电子设备所具有的抑制外部电磁干扰的能力,同时该设备产生的电磁干扰应低于规定的限度,不能影响同一电磁环境中其他电子设备的正常工作。随着电子设备的日益普及,电磁干扰日益严重,电磁兼容性的设计变得更加重要。电磁兼容性设计是一项复杂的系统工程,设计中要参照实际电磁环境提出具体要求,进而提出解决的技术措施。

反应堆控制保护系统所涉及的电子设备种类繁多,内部电路复杂,包括数字信号处理系统、输入/{畲出通道、数字显示装置、接口电路、驱动电路、控制模块及稳压电源等,是模拟与数字电路并存、硬件与软件相结合的统一体。电子设备的电磁干扰不仅不同程度地影响反应堆安全重要设备和系统的功能,而且还可能对反应堆的安全运行造成威胁。为了提高控制保护系统的可靠性,必须有效抑制各种电磁干扰、优化电路设计和软件设计,保证反应堆安全可靠运行。本文针对基

于现场可编程门阵列(FPGA)的反应堆控制保护系统,提出了电磁兼容性的设计与实现方法,以保证系统具有较强的抗干扰能力。

2 电磁干扰的成因

2.1 电网干扰

反应堆控制保护系统采用交流供电,电网质量直接影响系统工作的稳定性。电网干扰包括浪涌电压和电磁干扰。系统工作现场的大功率电气设备在启动或停止时,会产生几百伏、甚至上千伏的浪涌电压并伴有火花干扰。

2.2 传输线干扰

传输线干扰是在输入、输出线上形成的干扰。对于反应堆系统,从传感器、探测器传输的各种模拟信号有十多条,从控制台、控制柜传输的开关量信号有几十个,传输线长度达几十米至上百米。这就很容易将工作现场的干扰引入系统中。

2.3 机内干扰

任何~台正在工作的仪器,其本身就是一个干扰源,干扰信号包括由继电器产生的火花放电干扰、自激振荡、尖峰干扰、噪声电压等。

3 硬件设计中采用的抗干扰措施

3.1 隔离技术

在控制保护系统设计中,基于FPGA的每套仪器(包括安全保护系统、脉冲棒控制系统、报警系统、定标保护仪、密码权限单元)都是以FPGA为核心的可编程片上系统(SOPC)嵌入式系统,要接收来自控制台或者从其他仪器传输过来的开关量输入信号,以及从传感器传输来的模拟信号和脉冲信号,同时又要输出重要的控制信号到相关仪器仪表或远程设备作为信号源。

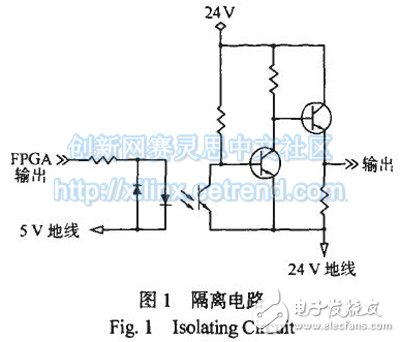

为了避免噪声随着信号一起传输进入仪器内部,每套仪器采用直流值流电源变换器将电源隔离,并在信号输入、输出通道中采用光耦合器,使开关量信号与FPGA的输入/输出信号隔离,不受电磁干扰的影响。图1为信号隔离电路。

3.2 消噪电路

在信号输入端并联一个0.1 laF的消噪电容,可以滤除高频噪声。

在电路设计中,用到了大量的数字仪表控制设备,而每个数字仪表控制设备本身都是一个脉冲干扰源,会通过电源线相互干扰。解决办法是采用去耦旁路措施,即在印制板电源进线端并联一个10 I_tF/35 V的钽电容进行电源退耦,同时在每个芯片的电源进线端再并联一个0.1虾的高频、低分布电感的陶瓷电容。

为了提高系统的抗干扰能力,电路中选用了噪声容限最高的互补金属氧化物半导体(CMOS)集成电路、低噪声的金属膜电阻以及钽电容。

对于电路中运用的运算放大器和交/直流转换器,其速度越高,越容易受电磁干扰的影响。由于设计时对速度要求不高,采用了非高速运算放大器和交/直流转换器,以降低受干扰影响的程度。

3.3 自激的消除

3.3.1 自激产生的原因对于引入了负反馈的放大电路,其输入寄生电容(包括运算放大器的输入电容和布线分布电容)与反馈电阻将组成一个滞后网络,引起输出电压相位滞后。当输入信号频率很高时,寄生电容的旁路作用使放大器的高频响应变差,从而影响电路的稳定性。

此外,在放大电路输出端存在输出负载电容(包括寄生电容),与输出电阻共同造成附加相移,这个附加相移的累加可能产生寄生振荡,使放大器工作极不稳定。

基于以上2种因素,在没有输入信号进入放大电路时,放大器却有输出信号,这就表明系统产生了自激,必须消除。

3.3.2补偿措施

在图2所示的放大器电路设计中,通过在负反馈回路的电阻上并接补偿电容C66,与输入电阻一起补偿附加的滞后相位,可以有效消除寄生振荡川。同时,在放大电路输出端串联一个电阻R159,使负载电容与放大电路相隔离。通过采用适当的补偿方法,解决了自激振荡问题。

3.4建立比较器的外部滞回电压

在基于FPGA的控制保护系统设计中,安全保护系统、报警系统、脉冲棒控制系统等子系统内部都含有阈值调节电路,对输入的信号进行甄别,实现相应的定值保护、定值报警以及控制。而外部输入的模拟信号中可能夹杂噪声和干扰,使比较器在阈值附近出现重复翻转,造成系统不稳定,抗干扰能力差。在实际设计中,采用集成放大器芯片构成迟滞比较器。

在图3中,电阻R150、KWl、R152将输出电压的一部分反馈到比较器的同相输入端,建立比较器的外部滞回电压,可根据需求调节阈值。由于上、下门限电乎不重合,在识别高低电平时有较强的抗干扰能力。

4 利用软件提高抗干扰能力

4.1 消除机械按键引起的抖动

在基于FPGA的控制保护系统设计中,每种子系统都有手动控制的按钮、按键。在操作时,由于机械触点的弹性及电压突跳等原因,在触点闭合或开启的瞬间会出现电压抖动,使得输入信号中存在噪声,如果不进行消抖处理,系统可能

将这些噪声作为输入信号采集进来,从而导致系统误动作。

在控制保护系统设计中,采用FPGA设计了弹跳消除电路(图4)。通过设计一个计数器,将按键使能信号key_pressed作为计数器的重置输入key_pressed=0时,计数器开始对采样脉冲计数。只有在采样时间内(此处设置为10ms)连续计数达到足够次数时认为按键按下(即key_pressed=0)有效,否则视为无效,计数器置0,重新对按键使能信号key_pressed进行采集、识别。这样就可以将短时间内key_pressed=0的情况滤除掉,避免按键按下时产生的抖动效

应被系统采集,造成系统误动作。

4.2 滤波技术

工作现场存在空调、电焊、电钻等大功率干扰源。这些设备的启动或停止瞬间,会产生浪涌电压并伴有火花干扰,通过电源线进入设备。这些干扰仅靠电容无法消除。因此,在抗干扰设计中,使用了FPGA构建数字滤波电路的方法。

在基于FPGA的控制保护系统中,对输入开关量信号的响应时间要求不高,采用了与前述弹跳消除电路相似的设计方法。设计一个计数器,目的是避免尖峰干扰效应使输入信号signal_in发生不必要的变化,而造成重复统计输入信号次数的结果。因此,将signal_in作为计数器的重置输入,在有输入信号(即signal_in=1)时,对采样脉冲开始计数;只有在采样时间内(此处设置为1μs)连续计数达到足够次数时认为信号有效,否则视为无效。针对不同的尖峰干扰,可以设置不同的采样时间,这样就可以将signal_in在短时间内变为l的情况滤除掉,从而消除不稳定的尖峰干扰。

输入信号signal_in上的尖峰干扰经过滤波后,得到了干净的输出信号signal_out,证实了加入滤波的数字电路可以有效提高系统的抗干扰性能,只有真实的输入信号才能对设备产生影响。

但是,经过滤波后的信号响应时间比较长。如果系统对信号响应时间要求很高,这种软件滤波的方法不再适用,这时采用底盘安装插头集成有电源滤波器的地线扼流圈FN329,可以有效减弱干扰源在电源3条线上的干扰,提高设备的抗干扰性能。

5 结论

电磁兼容性设计是保证系统安全稳定的重要指标。参照实际的电磁环境,采用了隔离、消噪、退耦、消除自激振荡、建立迟滞回路、滤波等软硬件相结合的技术途径,选择了噪声容限高的电子器件,在不同程度上对不同的电磁干扰进行削弱,使基于FPGA的反应堆控制保护系统的抗干扰能力得到了较大提高,有利于保证反应堆的稳定可靠运行。

- 相关推荐

- 热点推荐

- FPGA

-

核反应堆工作原理 核反应堆的燃料是什么2024-02-03 5550

-

核电站数字化仪控系统与传统控制系统相比有何优势?2021-07-07 1370

-

核反应堆压力设备环形密封面泄露监测分析2021-06-16 1450

-

核反应堆功率控制系统设计与仿真的详细资料说明2021-03-16 817

-

如何利用变频器升级核电反应堆循环泵控制器2021-01-19 1249

-

美国加快开发先进核反应堆设计2020-12-29 2586

-

华能石岛湾核电高温气冷堆示范工程首台反应堆冷态功能试验成功2020-10-20 2897

-

DIY钢铁侠反应堆制作过程分享!2019-08-19 14962

-

反应堆样品照射控制装置系统设计2019-07-17 1580

-

基于FPGA的反应堆控制保护系统设计2018-10-18 2260

-

基于反应堆功率与冷却剂流量协调控制2018-03-13 1050

-

核反应堆系统的发展及第四代核反应堆系统的简介2017-10-30 2705

-

核聚变反应堆的原理很简单2010-08-17 2895

-

基于LabVIEW的反应堆启动数据采集系统2009-08-31 619

全部0条评论

快来发表一下你的评论吧 !