基于FPGA连接的JESD204B高速串行链路设计需要考虑的基本硬件及时序问题详解

可编程逻辑

描述

与赛灵思FPGA连接的数据转换器正迅速采用全新JESD204B高速串行链路。要使用该接口格式及协议,设计必须考虑一些基本硬件及时序问题。

在当前大多数设计中,通过选用并行低电压差分信号(LVDS)作为数据转换器和FPGA之间的接口。在采用较慢速度转换器的设计中,一些FPGA设计人员仍然使用CMOS作为接口。然而最新数据转换器和FPGA正在从并行LVDS和CMOS数字接口升级为JESD204B串行接口,这是一种由JEDEC固态技术协会(独立半导体工程贸易和标准化组织)开发的新标准。

随着转换器分辨率与速度的提高,对更高效接口的需求也在不断攀升。这种接口是FPGA与模数或数模转换器之间的重要链路 ,在大多数系统中模数或数模转换器都位于FPGA的旁边。与以前的接口技术相比,JESD204B接口不仅可为设计人员带来这种效率,而且还可提供几项优势。支持JESD204B的新型FPGA设计将拥有更快接口的优势,能够与转换器更快采样速率保持步调一致。此外,引脚数的显著减少还可实现更小的封装尺寸以及更少的线迹布线,从而可降低电路板设计复杂性。

所有这一切的实现并非没有代价。

每种类型的接口(包括JESD204B)

都具有时序考量等各种设计问题。具体情况具体确定,但每种接口都有其自己的一套参数,设计人员必须正确分析才能获得令人满意的系统性能。此外,还需要进行硬件选择。例如,不是所有的FPGA及转换器都支持JESD204B接口。此外用户还必须使用诸如信道数据速率等最新参数,才能选择适当的FPGA。

在详细探讨新型JESD2904B接口之前,让我们先看看长期以来设计人员用于FPGA至转换器链路的另外两种选项:CMOS和LVDS。

CMOS接口

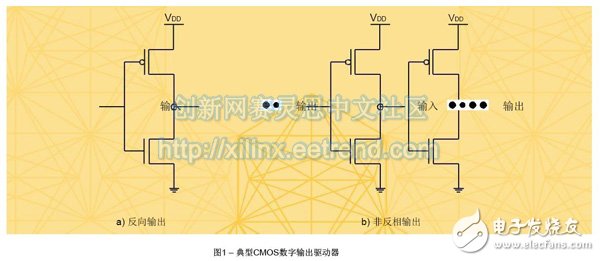

在采样速率不足200百万样本每秒(MSPS)的转换器中,FPGA的接口通常选用CMOS。典型CMOS驱动器可以概括为两种晶体管:一种是NMOS,而另一种则是PMOS,它们连接在电源(VDD)与接地之间,如图1a所示。这种结构会导致输出反向,要避免该问题,用户可使用图1b所示的背对背结构来代替。CMOS输出驱动器的输入是高阻抗而输出则是低阻抗。在驱动器输入端,两个CMOS晶体管的门电路呈高阻抗,其范围可能在数千欧姆至百万欧姆之间。在驱动器输出端,阻抗由漏极电流ID控制,可将阻抗保持在数百欧姆范围内。CMOS的电压电平大致在VDD至接地之间摆幅,因此很大程度上由VDD的量级决定。

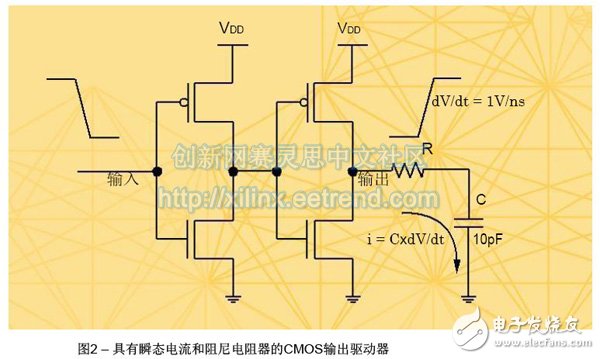

对CMOS来说,需要考虑的重要事项包括逻辑电平的典型开关速度(约1V/ns)、输出负载(每门电路驱动约10pF)以及充电电流(每输出约10mA)。重点是通过使用尽可能最小的电容性负载来最大限度地减少充电电流。此外,阻尼电阻器也将最大限度地减少充电电流,如图2所示。由于这些电流累加速度很快,因此最大限度减少它们非常重要。例如,一个四通道14位A/D转换器可能具有高达14x4x10mA的瞬态电流,即达到了惊人的560mA。

串联的阻尼电阻器将有助于抑制这种大瞬态电流。该技术将降低瞬态在输出端产生的噪声,从而有助于防止输出端产生额外的噪声,防止A/D转换器中出现失真。

LVDS接口

对FPGA设计人员而言,LVDS相对CMOS技术具有某些明显的优势。LVDS接口可提供约350mV峰至峰低压差分信号。较低的电压摆幅不仅可缩短开关时间,还能减轻电磁干扰(EMI)问题。此外,赛灵思FPGA系列中的众多器件,诸如Spartan®、Virtex®、Kintex®和Artix®等均支持LVDS接口。另外,凭借差分特性,LVDS还提供共模抑制能力。这是指耦合到信号中的噪声会同时出现在两个信号路径上,其中的大部分噪声会被差分接收器抵消。

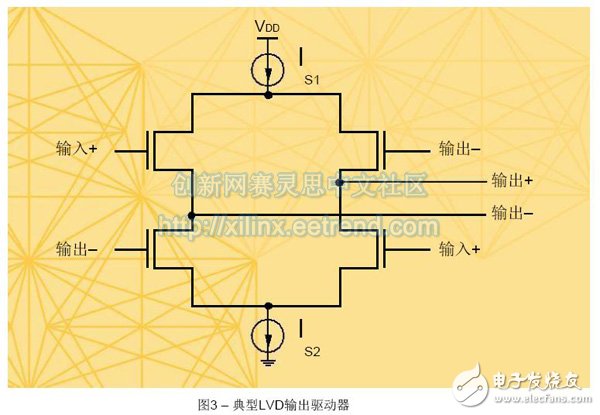

LVDS需要约100欧姆的负载阻抗,这一般可通过在LVDS接收器上并联一个端接电阻来提供。此外,必须采用阻抗受控的传输线来路由LVDS信号。图3所示的是典型LVDS输出驱动器的高级视图。

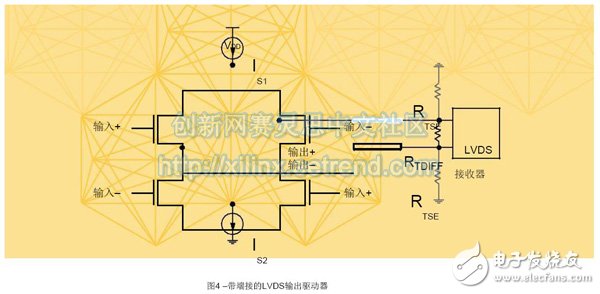

对差分信号而言,要考虑的要点是正确的端接。图4显示了典型LVDS驱动器以及接收器所需的端接。用户既可以使用单个差分端接电阻(RTDIFF),也可以使用两个单端端接电阻(RTSE)。

如果端接不正确,信号质量就会变差,导致数据在传输中出现中断。此外,要进行正确端接,还需要注意传输线的实体布局。通过使用合适的走线宽度来保持合适的阻抗。布局过程的变化不应该引起阻抗的大幅变化。应避免差分传输线间距的突变,以减少可能的信号反射。

JESD204B串行数据接口为转换器向接收器件传输数据提供了一条更好更快的途径。最新转换器和FPGA设计正转向使用支持JESD204B的驱动器。

JESD204B接口

JESD204B串行接口是继高速转换器和FPGA接口之后的最新技术,它采用电流型逻辑(CML)输出驱动器。一般来说,分辨率较高(不低于14位),速度较快(不低于200MSPS),需要较小型封装且功耗较低的转换器使用CML驱动器。这会存在重叠的情况,因为速度在约200MSPS范围的高速转换器也使用LVDS。这就意味着转向使用JESD204B的设计人员可以采用很可能在使用LVDS的高速转换器上已得到验证的设计。这样一来可以简化设计,降低一定程度的风险。

将CML驱动器与串行JESD204B接口结合使用,可让转换器输出端的数据率达到12.5Gbps。 这样的速度有望让转换器采样速率提升到GSPS级范畴。此外,所需的输出引脚数量也大幅度减少。也不再需要路由单独的时钟信号,因为时钟已经嵌入在8b/10b编码数据流中。由于配备CML驱动器的接口一般为串行接口, 故所需引脚增加量与CMOS或LVDS相比,要少得多。

表1列出了具有不同通道数量和位分辨率的200-MSPS转换器的三种不同接口的引脚数。对CMOS和LVDS输出而言,数据负责为每个通道的数据提供同步时钟。对使用JESD204B的数据传输而言,最大数据率达4Gbps。这样的通道速率已经低于许多目前可用的Virtex-6、Virtex-7、Kintex-7和Artix-7系列FPGA器件的最大限值。如果用户注意到使用JESD204B可以明显减少引脚数,那么转向使用JESD204B的原因也就一目了然了。电路板布线复杂性的降低以及 FPGA所需的I/O数减少,可释放这些资源用于其他系统功能。

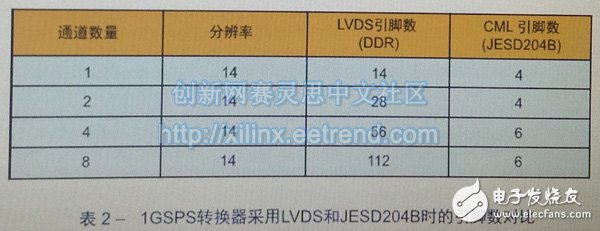

沿着这个方向再向前迈进一步,看看运行在1GSPS的12位转换器,使用JESD204B的优势就更加明显了。这个实例省去了CMOS,因为要将CMOS输出接口用在千兆样本转换器上是完全不切实际的。同时,将转换器通道的数量限制为四个,通道速率限制为5Gbps,这再度与Virtex-7和赛灵思7系列FPGA中的众多器件吻合。可以看到,由于输出引脚数量的下降,JESD204B可以大幅降低输出路由的复杂性。对一个四通道转换器(见表2)而言,引脚数有近6倍的减少。

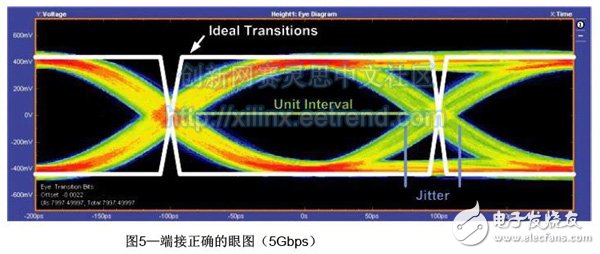

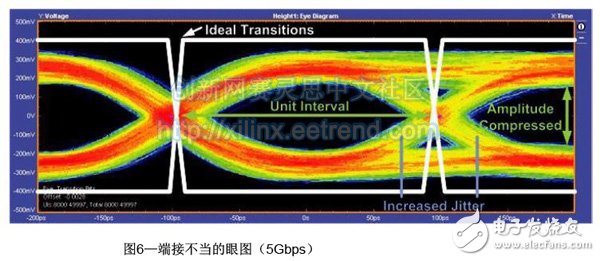

和使用LVDS接口的情况一样,当CML搭配JESD204B接口使用时,需要保持合适的端接阻抗和传输线阻抗。眼图是测量信号质量的方法之一。这是一种显示链路上信号多项参数的测量方法。图5所示的是5-Gbps JESD204链路上端接正确的CML驱动器的眼图。这个眼图过渡良好,眼部充分张开,说明接收器侧的FPGA可以轻松地解读数据。图6所示的是同一5Gbps JESD204链路上端接不当的CML驱动器的眼图。此眼图抖动较多,幅度下降,眼部趋于闭合。在这种情况下FPGA中的接收器难以解读数据。可以看到,需要使用恰当的端接才能实现最佳的信号完整性。

一种更好更快的办法

上述转换器中使用的三种主要的数字输出类型在与FPGA相连时都有各自的优缺点。在FPGA设计中使用采用CMOS、LVDS或CML(JESD204B)输出驱动器的转换器时,需要考虑它们各自的优缺点。这些接口是FPGA和模数转换器/数模转换器之间的关键链路。每一种类型的驱动器都有各自的特性和要求,设计人员在设计系统时必须考虑到这一点,这样FPGA中的接收器才能正确捕获转换器的数据。重点在于了解必须驱动的负载;在适当的地方使用正确的端接;以及对转换器使用的不同类型的数字输出采用正确的布局技巧。随着转换器的速度和分辨率的提高,越来越需要更高效的数字接口。正因为如此,运用最佳布局技巧打造出设计得当的系统,才变得更为重要。

JESD204B串行数据接口为转换器向接收器件传输数据提供了一条更好更快的途径。最新转换器和FPGA设计正转向使用支持JESD204B的驱动器。

这种需求源于系统级对更高带宽的需求,进而要求速度更快、采样率更高的转换器。反过来,更高的采样率也要求更高的输出数据率,为此,JESD204B应运而生。随着系统设计日趋复杂,转换器性能节节攀升,JESD204标准也需要适应和发展,以不断满足新的设计要求。不断发展演进的JESD204标准有助于该接口的推广使用,最终促使其成为转换器和FPGA的默认接口。

-

JESD204B使用说明2024-12-18 3123

-

ADC16DX370 JESD204B串行链路的均衡优化2024-10-09 757

-

JESD204B协议介绍2022-11-21 947

-

如何构建您的JESD204B 链路2022-11-04 975

-

JESD204B协议有什么特点?2021-04-06 2113

-

FPGA高速数据采集设计之JESD204B接口应用场景2019-12-03 5249

-

JESD204B串行接口时钟的优势2019-06-19 3738

-

串行LVDS和JESD204B的对比2019-05-29 3175

-

基于高速串行数字技术的JESD204B链路延时设计2018-11-21 2495

-

在Xilinx FPGA上快速实现JESD204B2018-10-16 3711

-

构建JESD204B链路的步骤2018-09-13 4880

-

JESD204B 串行链路的均衡器优化2015-05-11 4891

全部0条评论

快来发表一下你的评论吧 !