一款基于FPGA的无线电系统教学平台

FPGA/ASIC技术

描述

利用赛灵思Spartan-6器件和一些外设组件轻松为学生和新手构建一款有趣的演示平台。

我们近期打算北京理工大学开发一款数字设计教学平台,它能展现FPGA在通信和信号处理领域的实际效用。这个平台要直观易用,能帮助学生了解数字设计的各个方面,同时还要便于学生针对自己独特的系统设计进行定制。

当时我们电子工程系进就能否用FPGA的I/O引脚作为比较器或直接采用1位模数转换器展开了一场激烈辩论。我们决定验证一下前提条件,试图在XRadio平台设计中采用FPGA比较器。该平台就是我们采用赛灵思低成本Spartan®-6 FPGA和一些常见外设组件设计而成的一个全数字FM无线电接收器。去年赛灵思大学计划(XUP)总监Patrick Lysaght刚好来北京理工大学访问,我们借机向其演示了这款能正常工作的无线电。这款设计的简易性给他留下了深刻印象,他鼓励我们在全球学术社区上分享XRadio设计经历。

系统架构

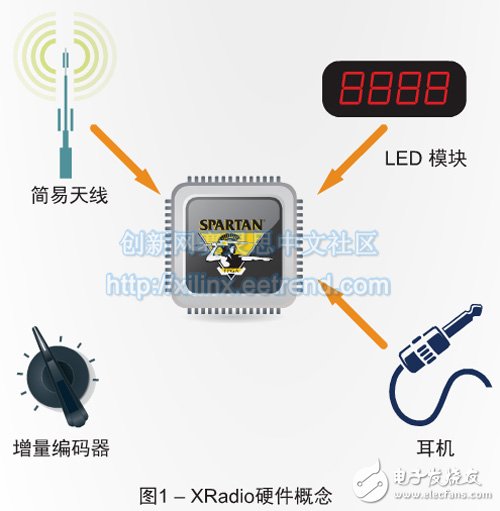

我们几乎完全用FPGA来构建XRadio平台,省略了放大器或分立滤波器等传统模拟组件的使用(如图1所示)。首先,我们将用电线连接成的简单耦合电路链接至FPGA的I/O引脚,创建出基本天线。该天线用于发射RF信号到FPGA,FPGA通过数字下变频和频率解调实现FM接收器的信号处理。我们随后通过I/O引脚向耳机输出音频信号。我们添加机械旋转增量解码器来控制XRadio的调频和音量。我们设计该系统可让调频和音量信息显示在7段LED模块上。

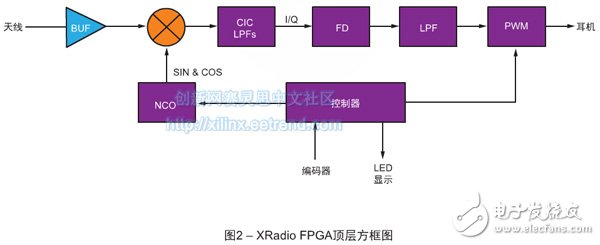

图2显示了FPGA的顶层逻辑方框图。在这个设计中,耦合到FPGA输入缓冲器的RF信号量化为1位数字信号。量化的信号乘以数控震荡器(NCO)生成的本地震荡信号,倍频后的信号经滤波可得到正交IQ(同相正交)基带信号。它随后通过频率解调器和低通滤波器从IQ信号获得音频数据流。

实现细节

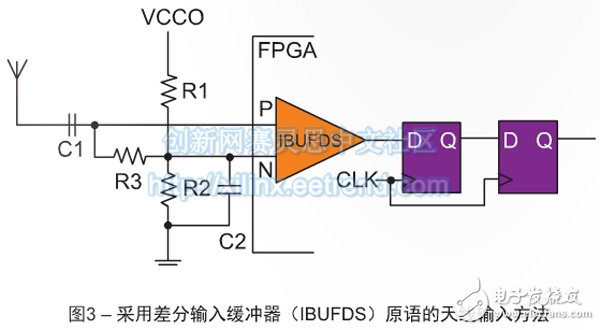

我们要解决的第一大难题就是如何将天线接收到的信号耦合到FPGA。在首次试验性设计中,我们将FPGA I/O配置为标准单端I/O,然后我们用电阻R1和R2构建分压器,以在FPGA引脚处的VIH和VIL之间生成偏置电压。天线接收的信号可通过耦合电容C1来驱动输入缓冲器。由内部240MHz时钟驱动的D触发器的两级负责对该信号进行采样。触发器输出端获得等间隔的1位采样数据流。

数据流随后进入脉宽调制(PWM)模块,在其输出端上生成脉冲信号。脉冲信号经过滤波,可得到驱动耳机的比例模拟值。我们将控制器模块连接到机械旋转增量编码器和LED。该模块从增量编码器获得脉冲信号,以调节NCO的输出频率以及PWM模块控制的音频音量。

为了测试这个电路,我们将结果馈送给另一个FPGA引脚并用频谱分析仪进行测量,看看FPGA是否能准确接收信号。不过,它工作得并不好,因为分析器显示Spartan-6 FPGA的输入缓冲器有一个较小的120毫伏磁滞电压。虽然磁滞一般来说有利于避免噪声,但在本应用中我们并不希望有磁滞。我们必须想办法提高信号强度。

该设计大幅降低了信噪比,这是因为1位采样生成的噪声量化的结果。不过4个台在背景噪声下仍能正常收到。因此我们能证明这样一个理论,那就是FPGA的I/O引脚能用作比较器或XRadio中的1位模数转换器。

为了解决这一问题,我们发现差分输入缓冲器(IBUFDS)原语在正负终端之间灵敏度极高。我们的测试显示低至1 mV的峰至峰差分电压足以让IBUFDS在0和1之间摆动。图3显示了所设计的输入电路。在本实现方案中,电阻R1、R2和R3在IBUFDS的终端P和终端N处生成普通电压。接收到的信号通过耦合电容C1馈送给终端P(sidefile:///app/ds/)。AC信号经N侧的C2电容滤波后,其可用作AC基准信号。就此电路而言,FPGA将FM广播信号成功转换为1位数据流。

无线电能收到强度不同的大约7个FM频道,包括103.9MHz北京交通台。该设计大幅降低了信噪比,这是因为1位采样生成的噪声量化的结果。不过4个台在背景噪声下仍能正常收到。因此我们能证明这样一个理论,那就是FPGA的I/O引脚能有效用作比较器或XRadio中的1位模数转换器。

就数字下变频而言,我们采用DDS Compiler 4.0 IP核构建数控振荡器,其系统时钟为240-MHz。正弦和余弦输出频率介于87MHz—108 MHz之间。NCO生成的本地振荡器信号乘以1位采样流,并通过低通滤波器获得正交基带信号。这里,我们采用CIC Compiler 2.0 IP核来构建三阶低通CIC抽取滤波器,其向下采样率R=240。由于滤波的基带正交信号为窄带信号,采样率降至1 MSPS。

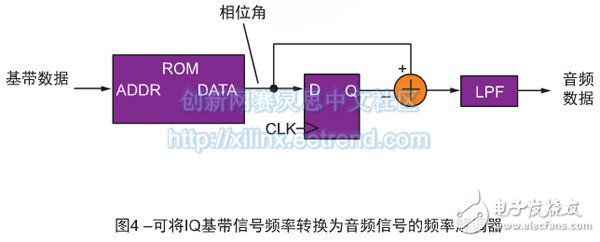

图4显示了可将IQ基带信号频率转换为音频信号的频率解调器。我们用ROM中的查找表提取IQ数据的瞬时相位角。整合IQ数据并用作ROM地址。随后ROM输出相应复角(complex angle)的实部和虚部。接下来我们进行差异操作,按一下触发器,就会延迟相角数据。从原始数据中减去非实时数据,所得结果刚好为所需的音频数据。为了改进输出信噪比,我们通过低通滤波器用简单平均法对音频信号进行滤波。

频率解调器的8位音频数据流输出可根据音量控制参数缩放,并发送到8位PWM模块。PWM脉冲的占空比反映了音频信号的强度。脉冲在FPGA的I/O引脚处输出,且通过电容驱动耳机。这里,耳机发挥低通滤波器的作用,去除音频信号中残余的脉冲的高频成分。

两个旋转增量编码器控制无线电的频率和音量。每个编码器输出两个脉冲信号。旋转方向和速度可由脉冲宽度和相位确定。状态机和计数器可将旋转状态转变为频率控制字和音量控制字。与此同时,对频率音量值进行解码,并显示在7段LED上。

定制余地

XRadio平台的印刷电路板如图5所示。利用Spartan-6 XC6SLX9 FPGA,您可设计出一个只占很少一部分FPGA逻辑资源的广播节目,如表1所示。这就意味着学生们可以定制设计并加以改善。举例来说,就1位采样而言,XRadio的音质不如标准FM无线电,不过这给学生们留下了很大的遐想空间,让他们设法如何改进XRadio音质以及如何实现立体声。

图5 – 合著者、研究生Xingran Yang展示工作模型

-

liccil_lic

2018-10-29

0 回复 举报求详细资料.. 收起回复

liccil_lic

2018-10-29

0 回复 举报求详细资料.. 收起回复

- 相关推荐

- 热点推荐

- FPGA

-

FPGA-CPLD在软件无线电中的工程应用2009-04-18 6861

-

基于FPGA的软件无线电硬件平台设计2014-07-30 4179

-

软件无线电、无线电的技术概述及应用2018-08-21 4198

-

中频软件无线电的实现方案和基于FPGA的通用硬件平台2019-05-28 1954

-

基于FPGA的软件定义无线电参考设计2019-07-04 1872

-

基于FPGA的软件无线电应用2019-07-29 2244

-

如何利用FPGA设计软件无线电平台?2019-08-02 2173

-

分析一款不错的中频软件无线电系统的FPGA实现方案2021-04-29 1399

-

怎么实现一款基于FPGA的软件无线电平台设计2021-05-06 1162

-

实现软件定义无线电和认知无线电的自适应特性2010-03-05 514

-

基于FPGA的软件无线电通信平台2011-10-13 1093

-

基于FPGA的软件无线电平台设计详细教程2018-05-02 4279

-

软件无线电硬件平台的FPGA动态配置2019-06-22 1483

-

如何使用FPGA实现软件无线电平台的设计2020-11-03 948

-

如何使用Labwindows CVI实现软件无线电的通信实验系统的资料说明2020-09-17 1238

全部0条评论

快来发表一下你的评论吧 !