用纯硬件解决方案加速部分重配置进程

FPGA/ASIC技术

描述

对视频等时序关键型应用,采用纯硬件解决方案可提升赛灵思 FPGA 的运行能力。

在视频处理等众多新型应用中,尽可能缩短FPGA 重配置时间对避免丢失过多图像至关重要。部分重配置指用户在不影响 FPGA 周边逻辑单元的情况下对其的一小部分进行重新配置的技术。如果要人眼观察不到图像的闪烁,重配置所花的时间不得超过 40 毫秒。除了最小型的 FPGA,对重配置整个器件而言这点时间太短。但在某些特定的情况下,该重配置时间还需要进一步压缩。于是部分重配置技术应运而生,因为部分重配置的比特流比完全重配置的比特流小,所以重配置所花的时间也更少。

我们这些在 Sagem DS 工作的开发人员已设计出一种技术,能够让 FPGA 设计人员以极快的速度完成部分重配置工作。我们使用赛灵思 ML507[1] 开发板来测试、验证解决方案和测量时序。一般情况下该开发板由一片Virtex®-5 FPGA(XC5VFX70T-FFG1136)、一片CPLD(用作路由组件)和两片XCF32P 存储器(赛灵思平台闪存)组成。

MICROBLAZE 与硬件解决方案的对比

在许多技术文档中,部分重配置 (PR)技术使用像 MicroBlaze® 这样的内部控制器或外部处理器。根据具体的配置,在 FPGA 内实现处理器需要占用开发时间,消耗大量的器件资源。同样,使用外部处理器会增加成本,占用电路板空间。另外,像 PLB 或 AXI 这样的总线存在时延,这样会延长重配置时间。

基于上述种种原因,我们采一款基于小型状态机的纯硬件解决方案,并采用内部配置访问端口 (ICAP) 接口加载比特流。这种方法具有多种优势:不存在时延,这种方法基本不占用资源(在 FPGA 上占用的查找表不足300 个),而且设计人员可以优化部分重配置的时序。

开发流程概览

从 VHDL 概念到比特流和部分比特流的创建,除了没有嵌入式处理器,我们的纯硬件部分重配置流程与赛灵思辅导教程、用户指南[2] 和应用指南中介绍的一般流程一样。用户必须在PlanAhead™ 中定义可重配置区域(RP),并为每个区域导入可重配置模块(RM)。对于所有的configurationruns 静态逻辑都可以从以前跑出的runs 导入。

在部分重配置的过程中,FPGA必须处于从模式。这就是说,可用的接口只有 JTAG、从串、从 并(Slave SelectMap)或 ICAP。完成重配置需用外部组件驱动 FPGA 的CCLK;ICAP 在 FPGA 首次启动时不能访问。为节省重配置所需的时间,可以不使用串行接口。这样就给我们留下至少两种接口供选择:SelectMap 和ICAP。

第一种选择是使用 SelectMap 接口供全部和部分比特流加载。这种配置方法需要在创建比特流的时候增加一个Bitgen 选项(-g Persist)。这样就由FPGA 保持对 SelectMap 引脚的控制,以便加载部分比特流。另外在使用SelectMap 的情况下,没有信号非常准确地提示流程结束(比如完全配置的完成 ( DONE) 信号)。所以难以确切地知道部分重配置是什么时间结束的。用户必须创建一个模块,用于估计所有配置数据完成发送的时间。

这就是为什么我们最终选择使用ICAP 原语加载部分比特流的原因。ICAP 不是一种像 SelectMap 这样的自配置接口, 所以我们在使用SelectMap 实现 FPGA 的首次启动之后,就由用户代码完全控制 ICAP原语。

与纯粹的 SelectMap 设计相比,ICAP 具有两大优势。首先, 转换(SelectMap 用于首次启动,ICAP用于部分比特流加载)对用户是透明的,无需使用 Bitgen 选项。因此用户可以控制存储器引脚。其次,也是最主要的优势,ICAP 能够不断将状态反映到输出上。如果 FPGA 处于重配置模式,这个状态就会发生改变。这样用户就能够“看到”部分重配置的结束。

重配置功能和组件

在我们公司,我们使用 FPGA 开发视频处理应用。这些功能会用到逻辑元件、部分 BRAM 组件和大量DSP。研究这三种元件的重配置时间非常有意义,因为它能指导我们在回答下面两个问题的基础上设定可重配置区域的大小:要满足我们的应用要求的 40 毫秒图像刷新时间,我们应如何设定可重配置区域的大小?我们需要在这个区域中放入多少个不同的元件?我们通过在 ML507 上测试不同类型的配置,回答了这两个问题。

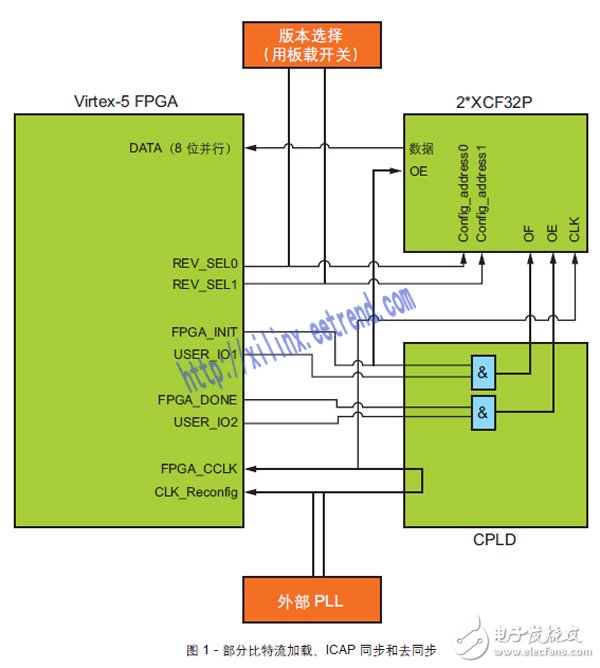

如图 1 所示,在 ML507 上我们选择外部锁相环 (PLL) 用作部分重配置控制的基准时钟。部分连接并非我们刻意选择,而是电路板设计所需。该原理图没有显示避免走线网络电平冲突的保护电路。时钟频率为33MHz,是开发板上两个 XCF32P 存储器的最高速率。[3] 数据总线宽度为8 位,可实现高达 264Mbps 的数据传输速率。

FPGA 上最小的可重配置区域是一帧。帧大小随 FPGA 的类型变化。例如,在 Virtex-5 上,一帧的大小是 20CLB,[4] 但在 Virtex-6 上,帧的大小是其2 倍。部分比特流就是基本帧、BRAM、DSP 和一些配置字的组合。配置接口和部分比特流的结构(内含的元件数量)是缩短部分重配置时间的关键。

重配置流程

图 2 是为部分重配置设计的 FPGA 的粗略架构。接通开发板上的开关即可启动流程。FPGA 通过并行SelectMap 接口加载全部比特流。此后由用户代码控制图中浅绿和深绿色区域中的所有模块。去耦逻辑是一个围绕部分重配置模块设计的专门区域。

在重配置过程中,连接网络走线上可能会出现未知状态。这个区域可以让用户在静态区域和可重配置区域之间的连接网络走线上保持已知状态。去耦逻辑实际上很小,仅由每个网络上的一个 D 触发器和一个多路复用器组成。信号“PR_END”负责控制多路复用器。

现在开始对存储器中的部分比特流的新配置对 PR_MODULE(例如直方图修正函数)进行重配置。“请求重配置”信号启动部分重配置流程,随后是一系列状态(图 2 中的状态清单并未完全列举)。

状态 1,ICAP 初始化,用于赋予控制信号以默省值(CE 和 RW 高电平)。

状态 2,让 ICAP 准备从存储器接收数据。ICAP 现已激活,目前处于写模式(向FPGA 里写入配置)。

状态 3,负责控制存储信号,并初始化从存储器到 FPGA 的部分比特流传输序列。同时,去耦逻辑负责保持静态区域和可重配置区域之间的信号。这样可以防止不需要的数据在用户功能中传输。

状态 4 为等待状态。在这期间,ICAP 将配置帧载入 FPGA,同时“状态检查”模块读取 ICAP 输出状态。在检测到“去同步”字时即从等待状态中退出。

状态 5,负责启动 PR_MODULE内的同步复位功能,进行复位,使得新的逻辑元件处于已知状态。

最终状态释放去耦逻辑, 禁用ICAP 和存储器。

ICAP 内部

用户无需准确了解或关注 ICAP 的工作原理。这是因为部分比特流已经提供了 ICAP 实现该应用所需的一切。尽管如此,还是应该了解 ICAP 中的两个 32 位字:同步和去同步。

第一个字,“同步”,在输入上体现为 5599AA66h。这个字让 ICAP的输出从 9Fh 变为 DFh(DFh 意为“组件同步”)。在 ICAP 输出状态为 DFh 时,FPGA 负责加载新的配置帧。

在配置数据发送后,比特流中包含一个“去同步”字,即 000000B0h。当 ICAP 接收到这个字,其输出状态变为 9Fh,说明该组件已经去同步。因此,检查 ICAP 的输出状态就能够让我们准确地掌握部分重配置时间。图 3 是带有相关信号的帧的重配置时间。

实验和结果

设计诸如自动直方图修正 (AHC) 等视频处理函数, 需要使用逻辑单元、BRAM 和大量的 DSP。由于对照明系统、热显影和电视视频来说,修正量并非一样多,FPGA 必须具备自适应能力,以满足最低响应时间要求(低于 40 毫秒,即眼睛暂留一幅图像的时间)。图 4(a)、(b) 和 (c) 显示的结果让我们对我们所用接口的重配置时间有了准确的认识。我们使用微型重配置模块(一个只有逻辑,一个有逻辑和 BRAM, 最后一个有逻辑和DSP)来测量这些时序结果。结果表明,各组件的时间是线性的。当然,这个结果只对我们的接口规范有效(33MHz 时钟,8 位宽总线)。

更大功能的重配置( 比如处理AHC 的功能的重配置)与我们的产品更密切相关,也检验了 FPGA 的运行情况。简单介绍一下 AHC 功能。一幅电视图形有Y、Cr 和Cb 三个分量。Y 代表亮度,Cr 和 Cb 分别代表红色和蓝色。AHC 模块必须将图像转换为RGB 格式,并对每种颜色进行特殊处理。对黑白图像而言,可以通过求最大值、最小值、平均值,然后运用放大、偏移或同时放大和偏移来增加亮度(对暗图形)和对比度。用 FPGA 资源来衡量,这种校正需要占用约 5,000 个查找表 (LUT)、4,000 个触发器、100个 DSP Slice 和 20 个 BRAM Slice。

图 5 是我们为 AHC 功能选择的可重配置区域。该区域内含 7,840 个查找表 (LUT) 和触发器、112 个 DSPSlice 以及 28 个 BRAM Slice。在该设计中,我们遵循了赛灵思提出的可重配置区域中的逻辑密度不得高于80% 的建议。Virtex-5 架构的一个Slice 中有 4 个 LUT 和 4 个触发器。一个可重配置逻辑模块 (CLB) 有两个 Slice,故一个帧中含有 160 个LUT 和 160 个触发器。我们的区域中含有 49 个帧。

根据图 4(a)、(b) 和 (c),我们可以用下列方法计算出重配置时间。逻辑需要 9.8 毫秒、112 个 DSP 需要 2 毫秒,28 个 BRAM 需要 6.4毫秒。这个区域共需要 18.2 毫秒即可完成重配置。这比眼睛暂留一幅图像所需的 40 毫秒要低得多。图 5 是可重配置区域的 PlanAhead 视图。

无需软件开发

如图 1 所示,我们可以使用定制板上的逻辑组件替代 CPLD。目前该解决方案运行良好,但尚未达到理想状态。我们可以使用更宽的总线(ICAP支持多达 32 位并行)和更高的频率来改进该可重配置接口。

纯硬件部分可重配置与MicroBlaze 解决方案相比,由于在系统开发过程中,无需进行软件开发,从而显著节约了开发成本。通过使用ICAP 接口,设计人员能够完全掌控FPGA 中工作情况,同时 ICAP 还极大地改善了系统的性能和功能。最后,尤其是对我们的视频处理应用而言,纯硬件部分重配置是一种能够增强我们产品性能的重要功能。

- 相关推荐

- 热点推荐

- FPGA

-

赛灵思发布ISE12.2强化部分可重配置FPGA技术2010-07-31 626

-

基于SPI FLASH的FPGA多重配置2014-01-24 15985

-

赛灵思公司在2017年闪存峰会上展示可重配置存储加速解决方案2017-09-20 3684

-

Xilinx PlanAhead部分动态重配置疑问2015-06-01 3094

-

动态部分重配置2019-05-14 1656

-

如何找出部分重配置的配置架构2020-05-29 1363

-

基于ARM和FPGA的终端重配置硬件平台实现2010-09-14 446

-

WP374 Xilinx FPGA的部分重配置2012-03-07 623

-

Xilinx的可重配置加速堆栈为云级应用提供业界最高计算效率2016-11-16 908

-

FPGA多重配置硬件电路的原理及其设计方案的介绍2017-10-12 1595

-

赛灵思可重配置加速堆栈方案,旨在快速开发和部署加速平台2018-07-31 1114

-

基于Visual C++程序与C++语言的FPGA可重配置设计方案2018-12-30 3563

-

Vivado Design Suite的部分重配置的新功能介绍2018-11-20 4621

-

协助全球最大的云端服务提供商着手开发和部署可重配置加速平台2019-08-01 2168

-

FPGA应用中部分重配置的操作过程2021-07-05 4828

全部0条评论

快来发表一下你的评论吧 !