利用FPGA进行基于动态比特自校正技术的高速数据无差错传输设计

可编程逻辑

描述

在Virtex-5系列的FPGA中包含了一些高级的数据传输和处理资源,如双倍数据速率(DDR)操作、可编程输入延迟(IDELAY)以及数据串行器/解串器(SERDES)。在FPGA资源应用中,中北大学电子测试技术国家重点实验室对FPGA的低压差分信号(LVDS)高速差分接口应用做了一些相关的研究。在芯片间的高速数据传输应用中,也有一些诸如PCI等方式的研究。下面重点研究了如何利用FPGA自身资源,进行基于动态比特自校正技术的高速数据无差错传输。

1、动态校正模式

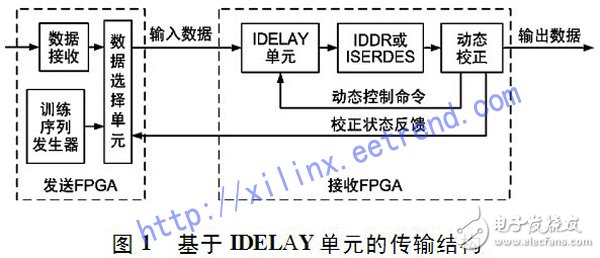

高级输入输出选择(SelectIO)资源中的可编程输入延迟单元(IDELAY)由64个tap的环绕延迟单元组成,每个延迟单元都有标定的tap分辨率。一个IDELAY的最大延迟是200MHz的一个时钟周期即5ns,那么每个tap的延迟时间为78.125ns。IDELAY单元的校正延迟功能对于高速数据和采样时钟的匹配是非常有用的。结合具体的工程应用直接用时钟去采样高速数据会出现误码,采用基于IDELAY单元的动态校正延迟的接收结构能有效的解决此问题。基于IDELAY单元的传输结构如图1所示。

1.1、训练序列和数据选择

训练序列作为动态校正在学习过程中的数据源,要满足实际数据随机特性的要求,每个链路的数据源也应该具有一定的差异。训练序列的长度可以根据实际情况而定。

IDELAY单元的64个tap最大延迟是5ns,而实时数据速率为320Mbps,即一个时钟周期为3.125ns。在发送端保证同步后,实际的接收端数据之间的延迟差异较小,在一个时钟周期以内。考虑到实际延迟差异和校正的最大动态范围,数据在经过IDELAY单元后,任意两两之间的延迟差异都在2个时钟周期以内。训练序列的周期时间应该大于最大延迟差异的2倍,即训练序列长度应该大于4,才能满足链路间数据的同步要求。

在实际工程应用中,为了减少程序的复杂度,降低FPGA资源的消耗,选用长度为5的训练序列。实际采用的训练序列如表1所示。

数据选择模块根据动态校正模块反馈的状态信 息选择发送给接收端的数据源。在动态校正成功之前一直发送训练序列,直到校正成功后再发送AD采集数据。数据选择在整个数据流中起到一个总开关的作用,要求动态校正模块能准确地进行数据延迟,使采样时钟的边沿在数据窗口的中间,保证能够稳定地采集到数据。

1.2、动态校正

动态校正模块的主要功能是完成数据的动态延迟,使采样时钟能够正确采集到数据。由于动态延迟的范围在2个时钟周期以内,有可能会使通路间的数据相差1个或者2个时钟周期,而通路内部比特之间的延迟差异较小。通过训练序列的先验信息来修正IDELAY的延迟tap数,使其通路内部比特实现同步。bit校正的主要功能是调整每个通路内部所有比特,保证每比特都能被采样时钟正确采集,同时使整个通路数据比特之间没有周期差异。动态延迟的范围是正负32tap,包含在2个工作时钟周期以内,在同一时刻的输出,可能会造成8个字节数据的不同步,而每个字节内部的比特间的延迟差异较小,通过训练序列的先验信息来修正同一字节内单bit的IDELAY延迟tap数,使单字节内部比特达到同步。

2、bit动态校正

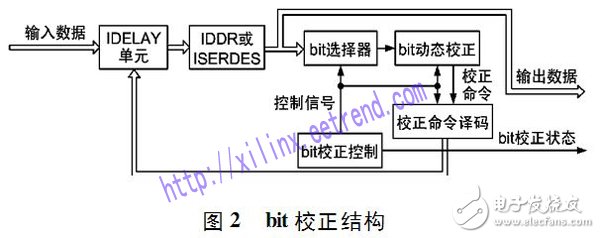

bit动态校正模块主要包括:bit选择器、bit动态 校正状态机、bit校正控制和校正命令译码器等子模块。bit校正结构图如图2

所示。

bit校正控制的主要目的是管理bit选择器和校正命令译码器,使其能实现一对一的准确校正而不出现混乱。校正控制首先选择第1比特进行校正,校正结束后接着选择第2比特进行校正,直到最后一比特完成bit校正完成后,给出整个通路bit校正结束的标志。

bit选择器模块根据bit校正控制给出的数据选择控制线,选出需要校正的相应比特对应的双沿数据转单沿数据的原语(IDDR)或者ISERDES的输出数据。

校正命令译码器的功能是bit选择器的逆过程。具体来说,它是根据bit校正控制的数据选择控制线,然后把bit动态校正状态机给出的校正命令译码给相应的IDELAY单元,使此比特的延迟校正到最佳状态。

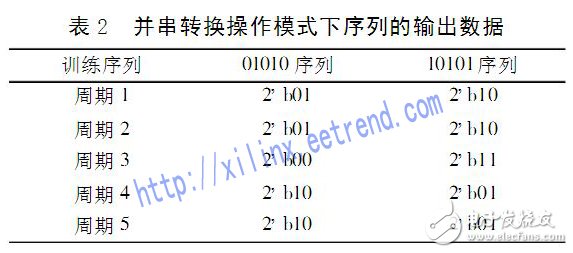

bit动态校正状态机是整个动态校正过程的关键模块。首先对通路的最低位进行校正,最低位即bit选择器选择的第1比特,以第1比特为例,训练序列为8’h01、8’hFE、8’h01、8’hFE、8’h01的循环序列,最低位为10101的周期序列。不同通路的训练序列不同,训练序列中第1比特也会出现01010的周期序列,所以这2种序列的检测同时进行。序列检测不仅和发送的序列相关,还与数据速率操作模式有关。无论采用双倍数据速率还是4倍数据速率操作模式,由于训练序列本身具有的周期性,所以不论经过1:2还是1:4串并转换后仍然具有周期性,2种操作模式下的序列周期都是5个时钟周期。2种操作模式下2种序列的输出数据如表2所示。以双倍数据速率操作模式为例,发送端在一比特单端线上传输01010的周期序列,那么接收端双倍速率输出为发送序列的1:2的串并转换输出,即2‘b01、2’b01、2‘b00、2’b10、2‘b10的周期序列。

第1比特校正成功后进行其余比特校正时,以此通路训练序列为标准进行相应的序列检测。训练序列具有良好的规律性,一个通路中每比特极性变化规律完全一样。只需知道此通路中每比特与第1比特的极性相同还是相反,就可以检测此比特数据是否正确。因此第1比特除外的其余比特可以直接根据此通路的训练序列进行极性对比,得出相应的极性标识,再由极性标识直接进行数据对比即可判定数据正确与否。

检测到正确序列后,如果没有超过最大延迟,那么将继续进行延迟操作,同时跟踪数据,检测数据是否仍然为正确序列。直到数据窗口延迟到边缘时停止延迟,如果数据窗口大小达到基本要求后,那么锁定此数据窗口,纠正采样点回到数据窗口的中间位置,此采样点得到的采集数据正是稳定的期望数据。

3、测试结果分析

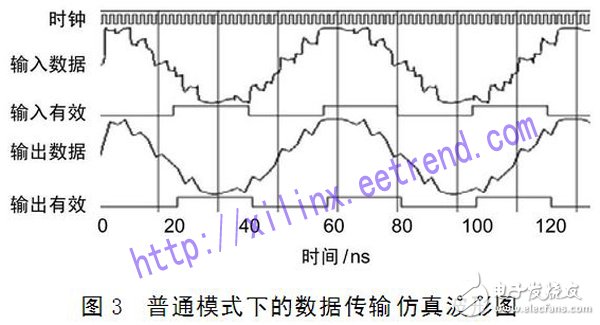

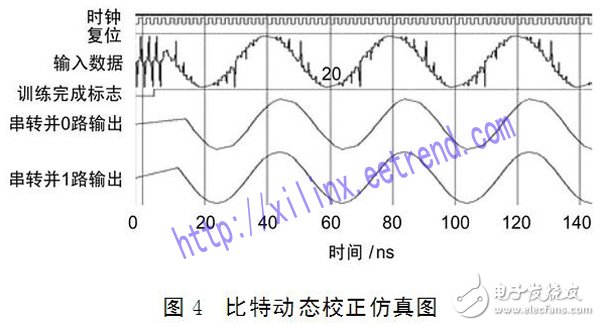

按照前述的动态校正的方法,用信号源、高速AD以及单片的xc5vsx95t芯片进行实际的硬件测试,得到普通模式下数据传输的波形结果和经过动态校正后的波形结果对比图,分别如图3和图4所示。

图3中原始数据是由信号源产生的一个标准正弦波形,由于传输线的不同延迟、信号间干扰和热噪声等多方面影响,出现了图中接收端的输入信号的畸变波形,导致普通模式接收到的传输数据波形不平滑。从波形对比分析来看,普通传输模式虽然资源消耗小,操作简单,但在高速数据传输时时序问题比较突出,误码率较高,高速数据传输的质量比较差。

图4为比特校正模式下,串转并后2个通路输出数据的仿真结果。测试时,用信号源产生正弦信号,送到高速AD去采样得到320Mbps的高速数据信号进入FPGA,即是图4中的输入信号,很显然,比特间存在较大延迟差异。校正模块准备就绪后(即训练完成标志变为高电平),立即开始输入数据,从图4中可以看出,经过比特校正后的输出波形0路输出和1路输出比输入数据光滑很多。与普通的数据传输模式相比较,波形有非常好的改善,克服了时序问题及逻辑和误码的问题,通过对比试验证明了此方案的可行性。

4、结束语

上述提出了一种高速数据并行传输的比特自校正方法,充分利用了FPGA的高级SelectIO资源中的可编程输入延迟单元进行比特校正,使数据的建立时间或保持时间能较好地满足实际要求,解决了320Mbps、64bits并行总线高速数据并行传输的难题。通过测试结果及分析可以发现,经过比特校正后,高速信号传输的质量得到了很大改善,能够满足实际的工程应用要求。目前这种技术已经在类似的高速数据传输项目中进行了广泛应用,均取得了良好的效果,由此也证明了此方法的可靠性和可移植性。

- 相关推荐

- 热点推荐

- FPGA

-

高速公路GPS车辆动态监控技术研究2009-04-16 5417

-

基于FPGA与DDR2 SDRAM的高速ADC采样数据缓冲器设计2010-04-26 10353

-

差错控制产生的原因2011-07-08 4280

-

在用鼎阳示波器什么情况下需要进行自校正?自校正有多...2013-01-08 5182

-

基于FPGA的高速LVDS数据传输2014-03-01 6826

-

如何利用RFID技术减少医疗差错?2019-08-07 881

-

怎么利用FPGA和光纤传输设计高速数字信号传输系统?2019-09-02 2590

-

基于FPGA器件和LVDS技术设计的高速实时波束形成器2020-11-25 1659

-

如何利用FPGA实现高速连续数据采集系统设计?2021-04-08 2337

-

PCIE高速传输解决方案FPGA技术XILINX官方XDMA驱动2021-05-19 6783

-

如何利用ARM和FPGA设计一种高速图像数据采集传输系统?2021-06-02 2566

-

基于FPGA的高速数据接口的实现2009-08-04 871

-

基于FPGA的高速可靠数据传输系统的实现2017-11-22 5769

-

数据链路层的功能2019-02-21 15074

全部0条评论

快来发表一下你的评论吧 !