基于FPGA的VME总线和CAN总线之间的传输转换方案设计

可编程逻辑

描述

为了扩展VME总线和CAN总线的应用范围,充分利用两种总线的不同传输特点,采用了模块设计方法,提出一种基于FPGA和MCU的总线转换方案。该方案给出了FPGA与上位VME总线部分的VME总线接口设计,利用MCU控制CPLD扩展的多通道CAN节点完成CAN总线部分的设计,还给出软件实现上的重点、难点和流程。实现了两种不同总线的转换,满足了工业环境对两种总线混合使用的要求。

CAN(Controller Area Network控制器局域网)以其高性能、高可靠性以及独特的设计等优点,为分布式控制系统实现各节点之间实时、可靠的数据通信提供了强有力的支持。CAN总线突出的可靠性、实时性和灵活性显示了它突出的优势,成为公认的最有前途的总线标准,广泛地应用于工业自动化、船舶、医疗设备、工业设备等方面。VME(Versa Module Eurocard)是一种通用的计算机总线,结合了Motorola公司Versa总线的电气标准和在欧洲建立的Eurocard标准的机械形状因子,是一种开放式架构。其独特的紧密耦合(Closely coupled)硬件构架,为其外围系统模块的设计提供了良好的基础,使VME总线广泛地应用于工业控制、军用系统、航空航天、交通运输和医疗领域。

本文提出了基于FPGA的VME总线和CAN总线之间的传输转换方案,满足一些特殊工业环境的需要,具有一定的研究意义和实用价值。

1 转换系统的硬件设计

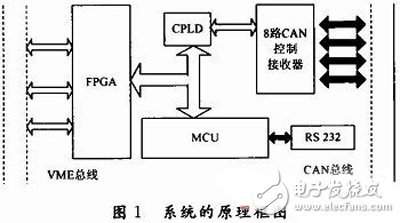

该系统由VME总线接口模块、CAN总线节点(8路CAN节点)模块、复杂可编程逻辑器模块、MCU模块4部分核心模块构成。整个系统在一个3U标准的VME板卡上实现,机构紧凑,布局合理。系统的原理框图如图1所示。

1.1 VME总线接口模块

整个系统实现是两种通信之间的转换,所以数据的发送都是由上位主机发送的。由于FPGA控制灵活,所以很方便实现与VME总线的连接。文中FPGA器件选用XILINX公司的XC2S200系列的5PQ208,56Kb专用存储器,最高运行速度200MHz,I/O电压在3.3~5.5V,地址总线、数据总线,/AS,/IACKIN,/IACKOUT,SYS CLK等可以直接与5PQ208连接。

1.2 CAN总线节点模块

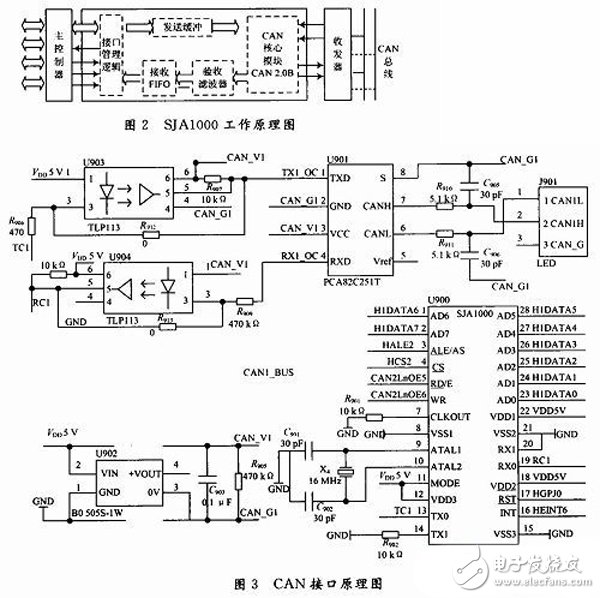

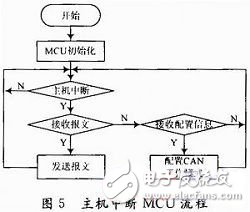

CAN总线节点模块是该系统中的主要模块,选用Philips公司生产的SJA1000,它负责连接总线与8路CAN选通主控制器CPLD之间的数据通信,其整个系统功能如图2所示。收发器选用P82C251T。CAN接口原理如图3所示。

1.3 复杂可编程逻辑器件(CPLD)模块

在系统中,由于FPGA的地址总线和数据总线是分开的,而SJA1000的地址和数据线是分时复用的,所以在总线接口上有一定差异,因此选用MAX3000系列可编程逻辑器件EPM3128来进行逻辑变换。该CPLD芯片有丰富的宏单元,80个用户I/O管脚,管脚间延迟时间是10ns,最高速度可达100MHz,能够满足系统设计的需要。可编程逻辑器件在系统中的功能为:转换FPGA与CAN控制器SJA1000之间的地址总线和数据总线;通过对FPGA的地址线译码,扩展CAN控制节点的通道。

1.4 MCU处理器

由于CAN总线的最高传输速度是1Mb/s,所以该部分选取宏晶STC12C5A60S2,FLASH程序存储器为56KB。SRAM为1280B,2个专用的UATR,丰富的CPU资源满足作为下位机的CPU控制单元,主要完成两种总线协议的转换,负责将从FPGA过来的VME总线转换成CAN总线格式,并传输到指定CAN节点;同时也将CPLD选通的CAN通道数据,转换为FPGA能识别的VME总线格式,并在MCU中断主机时,将数据反馈给VME主机。

2 转换系统的软件设计

2.1 软件设计思路

由FPGA构建8个双口RAM,8路CAN控制器通过这8个双口RAM与上位VME总线主机进行数据通信,RAM口分别映射到VME总线主机内存地址和MCU存储器空间中。系统数据传输采用MCU中断主机(VME主机)和主机中断MCU两种方式,前者通过触发主机外部中断实现,由双口RAM里面的中断控制来决定的,在触发中断后,提示主机读取CAN控制器接收到的数据以及CAN控制器的工作状态。主机中断MCU方式是通过MCU的外部中断管脚实现的,是由主机写入双口RAM的控制字实现的。触发该中断后,MCU就从主机接收要发送的报文,并发送到相应的CAN节点上,并配合主机配置CAN控制器的控制模式。中断流程如图4,图5所示。

2.2 FPGA的软件设计

在该系统中,数据都由VME主机控制,所以FPGA构造双口RAM(或者8个区域即可),使VME主机和MCU在RAM中完成数据传输。即主机要发送的数据放入RAM中等待MCU提取,同时MCU发送的数据放入RAM中等待VME主机提取。

2.3 CAN节点软件设计

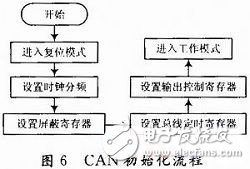

CAN节点软件是本系统的重点,它包括CAN控制器初始化、报文发送和报文接收3个部分。初始化主要完成设置工作方式、接收方式、屏蔽寄存器、验收代码寄存器、波特率和中断寄存器,并且要在复位模式下进行初始化。初始化流程如图6所示。

报文发送就是将代发的数据按照CAN总线协议的数据格式,组成一帧一帧的报文,送入SJA1000的发送缓冲区,触发SJA1000发送即可;报文接收同理。

2.4 MCU转换程序设计

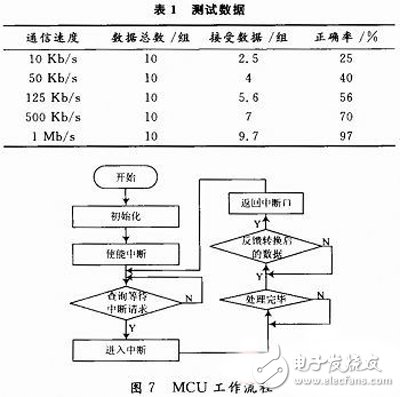

微控制器程序设计的主要目的是以最快的速度响应中断请求,完成两种总线数据的转换和传输。编程时采用模块化思想,每个模块完成一定的功能。编程采用Keil公司的Keil μVision3编程工具,设计分为:初始化系统、使能中断、查询总线,随时准备响应MCU中断主机(VME主机)和主机中断MCU两种中断触发,并且完成VME总线和CAN总线之间的重组和交换,及时将转换后的信息相应地传送给VME主机或者发送到CAN节点上。流程如图7所示。

3 测试分析

测试过程由VME总线端和CAN总线端互相发送数据包。其中,测试了5组由VME总线发送到CAN总线的数据包;5组由CAN总线发送到VME总线的数据包,记录如表1所示。由表1测试结果所示,该系统中CAN总线节点都设置在1Mb/s的速率下,系统可以准确地接受和发送数据包。系统正确率之所以会随通信速度的提高而提高,主要原因在于系统在不同的通信速度时,数据包发送频率、发送的最小延时间隔都不相同。如果需要进一步的提升数据发送的正确率,需要系统在硬件设计和PCB板制作上分别努力,才能保证尽可能小的干扰,尽可能大的提高系统的稳定性和抗干扰性。

4 结语

该系统充分利用了VME总线和CAN总线的优点,在FPGA和MCU的基础上实现相应的电路的连接和软件的设计,成功地完成两种不同总线之间的转换,扩展了两种总线的应用范围。

-

VHDL语言实现多DSP局部总线与VME总线接口设计2019-04-12 1158

-

用FPGA实现多DSP局部总线与VME总线接口设计2019-04-22 1482

-

一种基于FPGA和MCU的总线转换方案设计2019-06-28 4009

-

用CPLD实现DSP与背板VME总线之间的连接2009-08-15 787

-

基于VME总线的以太网接口设备2010-11-13 1046

-

VME总线原理及应用2010-03-11 10540

-

基于FPGA的CAN总线通信系统2016-05-10 785

-

基于FPGA的VME总线与DSP通信接口设计2017-10-19 1357

-

基于FPGA的CAN总线转换USB接口的设计方案2017-11-24 2973

-

CAN总线的双绞线及光纤传输2021-04-20 1579

-

CAN总线特点及FPGA的实现2021-11-18 7111

-

基于FPGA的CAN总线通信节点设计2023-06-18 4548

-

can总线的传输速率是多少?2023-09-07 22790

-

can总线为什么要用双绞线?can总线不用双绞线可以吗?2023-09-14 8047

-

can总线传输距离2023-12-07 5758

全部0条评论

快来发表一下你的评论吧 !