基于FPGA的异步FIFO设计方法详解

可编程逻辑

描述

在现代电路设计中,一个系统往往包含了多个时钟,如何在异步时钟间传递数据成为一个很重要的问题,而使用异步FIFO可以有效地解决这个问题。异步FIFO是一种在电子系统中得到广泛应用的器件,文中介绍了一种基于FPGA的异步FIFO设计方法。使用这种方法可以设计出高速、高可靠的异步FIFO。

在现场可编程逻辑芯片的设计过程中不同模块之间的数据接口尤其是不同时钟系统的各个模块之间的数据接口是系统设计的一个关键用异步FIFO模块来实现接口,接口双方都在自己时钟的同步下进行工作它们之间不需要互相握手只需要跟接口FIFO模块进行交互即可即向接口FIFO模块中写入数据或从FIFO模块中读出数据。用这样一个缓冲FIFO模块实现FPGA内部不同时钟系统之间的数据接口使设计变得非常简单和容易所用的FIFO接口是XILINX公司提供的IP核。经过充分测试和优化,系统运行稳定占用的FPGA内部资源也非常少。

1 FIFO 类型

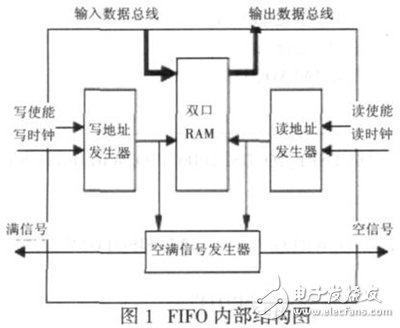

FIFO先进先出队列是一种在电子系统得到广泛应用的器件通常用于数据的缓存和用于容纳异步信号的频率或相位的差异FIFO的实现通常是利用双口RAM 和读写地址产生模块来实现的图1显示出了FIFO 的内部结构。

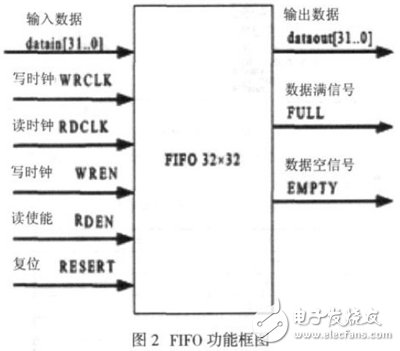

FIFO的功能框图如图2 所示

根据读写操作的同步/异步标志方案的同步/异步第一个写操作以及复位功能的不同FIFO 存储器可分为4 大类:

(1)异步FIFO。 通常只有两个控制信号读使能( RE )与写使能( WE)信号标志信号有全空标志(EF)全满标志(FF) 可选半满标志(HF)几乎全满标志(AF) 几乎全空标志(AE)这些标志并不与任何时钟或事件同步但是反映读写指针的即时对照。

(2)选通式FIFO。与异步FIFO存储器相似选通FIFO通常使用读写选通UNCK和LDCK信号以及输出使能OE信号这类FIFO 通常提供半满标志(HF)可选几乎满标志(AF)几乎空标志(AE)全空标志(EF)和全满标志(FF)这些标志虽然反映读写指针但不与任何时钟或事件同步。

(3)标准同步FIFO。同步FIFO需要自由运行的读和写时钟RCLK 和WCLK 读写操作是与这些时钟同步的控制信号包括读使能信号FEN 写使能信号WEN和输出使能信号OE 标志方案使用全空标志全满标志和半满标志时序上不是FWFT 的因此写入FIFO 的第一个字先停留在一个在存储单元中。

(4)FWFT 同步FIFO。FWFT First Word Fall Through FIFO与标准FIFO相似它需要自由运行的读时钟和写时钟RCLK和WCLK读写操作与这些时钟同步控制信号包括读使能REN写使能WEN以及输出使能信号OE内部结构是首字直接通过First Word Fall Through 的即是写入FIFO 的第一个数据单元直接进入输出缓冲区而不是停在存储器单元其标志方案是FWFT结构的直接结果也与标准同步FIFO不同。FWFT FIFO 存储器使用输出预备OR和输入预备IR标志而不使用全空标志和全满标志。FWFT FIFO 也使用半空标志,也可选几乎全空标志和全满标志。

2 FPGA内部软FIFO的设计

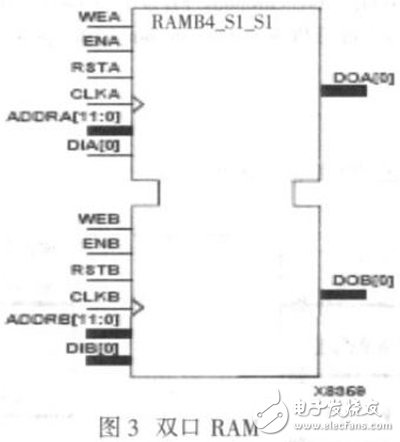

FPGA中有几个大容量的RAM,本文以XILINX公司Spartan-ⅡE系列芯片为设计芯片。在Spartan-ⅡE系列芯片中包含两列Block RAM,并且沿垂直边摆放。如图3所示

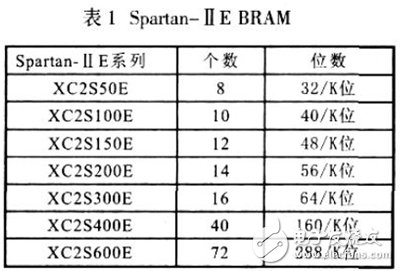

不同的Spartan-ⅡE系列芯片的所包含的Block RAM个数和位数如表1所示:

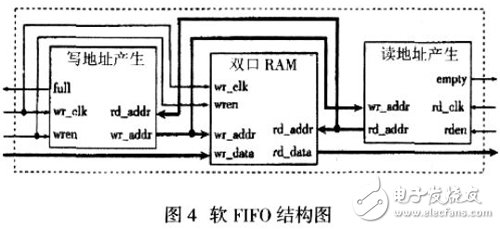

FPGA 中的软FIFO由三部分构成:写地址产生模块、双口RAM和读地址产生模块。如图4所示

由图4可以看出,写地址产生模块根据写时钟和写有效信号产生递增的写地址,读地址产生模块根据读时钟和读有效信号产生递增的读地址。FIFO的操作如下:在写时钟wr_clk的升沿,当wren有效时,将wr_data写入双口RAM中写地址对应的位置中;始终将读地址对应的双口RAM中的数据输出到读数据总线上。这样就实现了先进先出的功能。写地址产生模块还根据读地址和写地址关系产生FIFO的满标志。当wren有效时,若写地址+2=读地址时,full为1;当wren无效时,若写地址+ 1=读地址时,full为1。读地址产生模块还根据读地址和写地址的差产生FIFO的空标志。当rden有效时,若写地址-1=读地址时,empty为 1;当rden无效时,若写地址=读地址时,empty为1。按照以上方式产生标志信号是为了提前一个时钟周期产生对应的标志信号。

3 FPGA内部软FIFO的仿真

现场可编程门阵列FPGA是在专用ASIC 的基础上发展出来的,它克服了专用ASIC不够灵活的缺点。与其它中小规模集成电路相比,它有很强的灵活性,即其内部的具体逻辑功能可以根据需要配置,对电路的修改和维护很方便目前FPGA的容量已经跨过了百万门级使得FPGA 成为解决系统级设计的重要选择方案之一。现在FPGA 已经成为多种数据采集系统应用的强有力的解决方案。由于可编程方案的灵活性,数据采集系统设计可以适应日益变化的标准协议和性能需求,FPGA具有集成优势和更低的系统成本。

甚高速集成电路硬件描述语言VHDL 广泛用于描述数字系统的结构、行为、功能和接口。它的语言形式和描述风格与句法是十分类似于一般的计算机高级语言。

本文利用XILINX 公司Spartan-ⅡE 系列的FPGA器件现场用VHDL编程实现了软FIFO设计。在Quartus II 4.0 环境中仿真,得到了很不错的效果。部分程序和仿真结果分别如以下程序和图5所示。

部分VHDL 程序

…

FIFO1TO2:FIFO32TO32 PORT MAP

( wrclk=》FIFO1TO2WE,

rdreq=》FIFO1TO2RREQ,

rdclk=》FIFO1TO2RE,

wrreq=》FIFO1TO2WREQ,

data=》FIFO1TO2DATAIN,

rdempty=》FIFO1TO2EMPTY,

wrfull=》FIFO1TO2FULL,

q=》FIFO1TO2DATAOUT);

…

------------------------------PROCESS_FIFO_DSP1_TO_DSP2FIFO1TO2WRITE:PROCESS(FIFO1TO2WE)

BEGIN

IF (FIFO1TO2WREQ=‘1’ AND FIFO1TO3FULL=‘0’)

THEN

FIFO1TO2DATAIN《=DSP1DATA;

END IF;

END PROCESS FIFO1TO2WRITE;

FIFO1TO2READ:PROCESS(FIFO1TO2RE)

BEGIN

IF (FIFO1TO2RREQ=‘1’ AND FIFO1TO2EMPTY=‘0’)

THEN

DSP2DATA《=FIFO1TO2DATAOUT;

ELSE

DSP2DATA《=“ZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZ”;

END IF;

END PROCESS FIFO1TO2READ;

4 结论

文中针对异步FIFO设计中的难点和要点,提出了具体的解决方案,并用VHDL语言给出了电路的设计,利用XILINX的Spartan-ⅡE 系列FPGA实现,并被应用于多种电路中,在实际应用中取得了较好的效果。

-

同步FIFO和异步FIFO的区别 同步FIFO和异步FIFO各在什么情况下应用2023-10-18 2568

-

异步fifo详解2022-12-12 5368

-

Xilinx异步FIFO的大坑2021-03-12 1380

-

基于FPGA器件实现异步FIFO读写系统的设计2020-07-16 1501

-

基于FPGA的异步FIFO的实现2018-06-21 7112

-

异步FIFO在FPGA与DSP通信中的应用解析2017-10-30 1679

-

基于异步FIFO在FPGA与DSP通信中的运用2017-10-19 938

-

异步FIFO在FPGA与DSP通信中的运用2011-12-12 907

-

Camera Link接口的异步FIFO设计与实现2010-07-28 737

-

高速异步FIFO的设计与实现2010-01-13 613

-

异步FIFO结构及FPGA设计2009-04-16 731

-

一种异步FIFO的设计方法2006-03-24 1482

全部0条评论

快来发表一下你的评论吧 !