基于Xilinx FPGA的嵌入式串行千兆以太网设计

FPGA/ASIC技术

描述

随着通信技术的发展,千兆以太网因在传输中具备高带宽和高速率的特点,成为高速传输设备的首选。基于Xilinx FPGA的嵌入式系统设计整合了一系列的知识产权(IP)核使其功能强大,从而使得利用FPGA进行嵌入式串行千兆以太网开发成为可能。

本设计使用Xilinx公司65 nm工艺级别的Virtex5 FXT系列芯片,满足嵌入式系统设计所应具备的高性能、高密度、低功耗和低成本的要求。V5 Hard TEMAC模块提供了专用的以太网功能,并通过FPGA内部高速串行收发器GTX和Marvell公司的88E1111物理层接口芯片相连,完成串行千兆以太网的接口功能。物理层接口芯片支持MII、GMII、RGMII 和SGMII四种以太网接口模式。相对GMII接口而言,SGMII接口的I/O端口数目少,便于PCB布线,并且数据信号以差分对的形式出现,有利于保证信号完整性[1]。

本文将FPGA内嵌PowerPC硬核处理器、Xilinx精简嵌入式操作系统Xilkernel,以及相应的外设IP Core相结合,完成嵌入式串行千兆以太网的设计。

1 总体设计

系统硬件平台中选用Xilinx公司的Virtex5 FX70t作为主控芯片,它集成了PowerPC440处理器模块和高速RocketIO GTX收发器。

外部存储器采用Micron公司的128M×16位DDR SDRAM芯片MT47H128M16HG 31T,为程序运行提供空间。

在网络芯片方面有两种方案可供选择,即单物理层芯片方案和物理层加MAC层集成于同一芯片方案[2]。基于易于控制方面的考虑,采用Marvell公司的88E1111单物理层接口芯片作为解决方案,该芯片支持10BASET、100BASETX和1000BASET以太网协议。本系统硬件由Virtex5 FX70t芯片、88E1111 PHY芯片、DDRII芯片、8个拨码开关(8DIPS)、8个LED灯和RJ45接口构成,其连接框图如图1所示。

图1 系统硬件连接框图

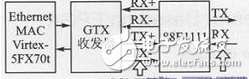

串行千兆以太网设计中,需使用FPGA内部RocketIO GTX收发器完成SGMII链路的建立。RocketIO GTX是集成在Virtex5 FX70t芯片中灵活的、功能可配置的千兆位级串行收发器,支持750 Mbps~6.5 Gbps的数据传输速率,满足千兆以太网系统设计中数据传输速率的要求。本设计通过在FPGA中例化EMAC硬核,并将相应的FPGA端口和外部PHY芯片88E1111相连完成SGMII链路的建立。SGMII接口使用全双工模式,有收发两个独立的通道,每个通道使用一对差分信号线,采用无时钟信号模式,RocketIO GTX收发器从串行数据中恢复时钟用于差分数据的发送与接收。

SGMII接口实现框图如图2所示。

图2 SGMII接口实现框图

本系统基于Xilinx公司嵌入式系统开发工具EDK12.3完成软硬件协同设计。EDK12.3由XPS (Xilinx Platform Studio)、SDK(Software Development Kit)等组成。设计时需在XPS环境下添加所需的IP核,生成硬件系统框架,并添加相应的引脚约束和时序约束,然后调用Platgen生成嵌入式系统硬件部分的网表(.NGC)文件和比特(.bit)文件,并通过软件描述文件(.MSS文件)来设置系统软件配置;接着将硬件设计导入到SDK中,并在SDK中生成各个外设的驱动层和库,设置相应软件的操作系统、库、外设驱动的属性,添加应用软件项目并编写应用软件;最后,调用处理器对应的编译器编译软件并和硬件可执行文件合成后,生成最终的二进制比特文件,下载到目标板进行系统调试[3]。

2 PowerPC的硬件设计

设计中采用的FPGA内嵌硬核处理器PowerPC440属于32位精简指令集嵌入式处理器,它采用扩展型BookE结构,其内部包括一个高性能、可双指令处理并有七级流水线的微内核。同时,具有灵活的存储器管理单元(MMU)、3个相互独立的128位PLB总线接口、4个直接存储器存储(DMA)控制单元,以及设备控制寄存器(DCR) 等[4]。它集成了32 KB指令和32 KB数据缓存,在550 MHz时钟频率下可提供高达1 100 DMIPS的性能。在本设计中,PowerPC440通过PLB总线与外设端口相连,其硬件架构如图3所示。

图3 嵌入式系统硬件架构

系统硬件平台的搭建(包括PowerPC处理器功能配置、系统总线结构以及相应的地址映射)均在EDK集成开发环境XPS中完成。

设计中采用片内高速数据总线PLB连接各种控制IP核,PowerPC440通过PLB总线完成对内部IP核以及外设的访问和控制功能。其中,外部PHY芯片通过与在FPGA内部例化EMAC核(Ethernet MAC)相连,挂载在PLB总线上,完成SGMII链路的建立;DDR II芯片通过IP核多端口存储控制器(Multiport Memory Controller,MPMC)挂载在PLB总线上,实现外部存储功能;串口通过串口控制器IP核(Xps_uartlite)与PLB总线相连,用于打印输出调试状态信息;8个拨码开关DIP和LED灯分别通过GPIO口与PLB总线相连,实现简单的控制与状态显示功能。

硬件结构如图4所示。

图4 PowerPC硬件结构图

本系统使用时钟生成器IP核生成系统各模块工作时所需时钟。该IP核模块的输入时钟为FPGA全局时钟引脚输入的100 MHz时钟,经过相应的倍频,生成400 MHz的PowerPC440工作时钟,生成200 MHz的DDR II工作时钟以及125 MHz的Ethernet MAC工作时钟。

在各模块添加及连接结束后,需添加UCF约束文件,包括FPGA引脚约束和相应的时序约束等,并对XPS自动生成的微处理器硬件规范MHS文件进行相应的修改,对系统进行适当的优化。生成的系统在综合、布局、布线无误后生成最终的.bit文件,准备下载到电路板上。

3 嵌入式系统软件设计

本系统软件部分需实现TCP/IP网络协议,TCP/IP协议模型包括应用层、传输层、网络层和网络接口层[5]。网络接口层分为PHY层和MAC层两部分。其中,PHY层由外部PHY芯片88E1111实现,MAC层由Xilinx公司的Hard Ethernet MAC IP核实现,并作为整个PowerPC系统硬件的一部分在FPGA的内部实现。

网络层和传输层主要采用LwIP协议模块编写相应的软件代码。LwIP同时支持服务器模式和客户端模式,提供RAW和Socket两种API。它的特点是在保持TCP/IP协议主要功能的情况下,减少对RAW的使用,使得LwIP在各类高档嵌入式系统开发中得到广泛的应用。本设计选择Xilinx公司的精简嵌入式操作系统Xilkernel,用于更好地管理系统资源。

Xilkernel能与EDK形成的硬件系统紧密结合,是一种可定制的简单高效系统。Xilkernel系统的配置可以在开发环境SDK中进行手动设置。本设计中运用LwIP协议模块编写运行在Xilkernel操作系统上的应用软件,实现了Web Server(网页服务)、FTP(File Transfer Protocl)、Telnet远程登录服务、iperf应用等功能。下面以网页服务程序、iperf服务器和客户端程序为例对软件设计流程进行说明。

具体流程描述如下:

① 在Xilkernel系统的静态启动线程main_thread()中,初始化网络协议和文件系统。

② 调用线程生成函数sys_thread_new()生成并启动线程1。

③ 在线程1中设置电路板硬件的MAC地址、网关、IP地址和子网掩码等参数,并初始化网络接口。具体设置方式如下:MAC地址为00:0a:35:00:01:02;IP4地址为192.168.1.10;IP4地址掩码为255.255.255.0;IP4地址网关为192.168.1.1。

④ 初始化一个Socket,将它与IP地址和端口号绑定,然后开始监听网络,一旦监听到网络请求,再由函数sys_thread_new()生成一个线程2去响应,用于缓存接收到的数据包。然后,通过函数launch_app_threads()判断监听到的网络请求属于哪种类型,并由函数sys_thread_new()生成相应的线程3去处理。

如果是网络服务请求,则将网页文件输出到PC机上,并接收PC机传输的控制数据信息,其程序流程如图5所示。如果是iperf应用请求,则发送或接收相应的数据完成对请求的响应。

图5 网页服务程序流程

网页服务程序运行前需在FPGA外部的DDR中建立文件系统,将用于控制的相关网页文件保存在该文件系统中。系统在运行时,访问预设的IP地址,会将相关网页文件传输到远端控制电脑上,并通过网页中的超链接命令脚本将预设的控制信息传送给PowerPC处理器,用以控制电路板上的LED灯亮灭,或者读取电路板上拨码开关的状态值并在服务器首页上显示。

本设计中采用iperf网络测试软件对其性能进行测试。采用9 000字节巨帧可以实现高达490 Mbps的传输速率。

结语

本文成功使用Virtex5 FX70t芯片实现串行千兆以太网系统,并通过网页服务程序对其功能加以验证。本系统在硬件电路设计阶段具有I/O端口数目少、便于PCB布线,以及信号完整性容易保证等优点。通过iperf网络测试软件对其传输速率进行测试,其结果达到高速数据传输的要求。

参考文献

[1] Xilinx.Virtex5 FPGA Embedded TriMode Ethernet MAC User Guide. [EB/OL].[20120711]. ~cs150/sp10/Project/Checkpoint2/ ug194.pdf.

[2] 高一沅,黄春晖.基于MicroBlaze的以太网通信系统平台设计的研究[J].现代电子技术,2007(17):2931.

[3] 王长清,陈栋.基于FPGA的千兆以太网通信板的设计与实现[J].河南师范大学学报:自然科学版,2011,39(1):8689.

[4] 宋晓翠,张晋宁.基于PowerPC440的嵌入式系统设计与研究[J].新特器件应用,2009,11(7):1921.

[5] 徐欣,于红旗,易凡,等. 基于FPGA的嵌入式系统设计[M].北京:机械工业出版社,2005.

- 相关推荐

- 热点推荐

- 嵌入式

-

简谈基于FPGA的千兆以太网设计2023-06-01 1222

-

FPGA如何为以太网和千兆以太网解决低功耗问题2022-05-07 5454

-

怎样去设计一种基于嵌入式Linux的千兆以太网卡驱动程序2021-12-17 1403

-

如何完成嵌入式串行千兆以太网的设计2020-04-09 2273

-

基于SOPC技术的嵌入式千兆以太网接口设计2017-11-07 978

-

基于嵌入式FPGA的10M_100M以太网自动协商模块设计与实现2017-03-16 1549

-

基于Xilinx FPGA的千兆以太网控制器的开发2015-01-23 31250

-

嵌入式工业以太网的应用研究2014-05-21 6210

-

嵌入式工业以太网控制器的设计和应用2011-11-17 1189

-

基于FPGA的嵌入式三态以太网设计2011-05-13 574

-

Xilinx FPGA设计的千兆以太网及E1信号的光纤传输方2010-07-06 3052

-

基于OpenTCP的嵌入式以太网模块设计2010-01-06 635

-

基于Altera FPGA的千兆以太网实现方案2009-12-26 4528

-

嵌入式以太网设计2008-06-27 1001

全部0条评论

快来发表一下你的评论吧 !