tlc549与单片机连接图

AC-DC/DC-DC转换

描述

TLC549 是采用IinCMOSTM 技术并以开关电容逐次逼近原理工作的8 位串行A / D7 芯片,可与通用微处理器、控制器通过I/0 CLOCK、CS、DATA OUT.三条口线进行串行接口。TLC549 具有4MHZ 的片内系统时钟和软、硬件控制电路,转换时间最长为17u s,允许的最高转换速率为40000次/S.总失调误差最大为土0.5LSB,典型功耗值为6 mW。

TLC549 采用差分参考电压高阻输入,抗千扰,可按比例量程校准转换范围,由于其VREF-接地时,(VREF+)-(VREF-) 21V,故可用于较小信号的采样,此外,该芯片还单电源3~6v 的供电范围。总之,TLC549 具有控制口线少,时序简单,转换速度快,功耗低,价格便宜等特

TLC549的极限参数如下:

电源电压: 6.5 V;

输入电压范围: 0.3V~VCC: +o.3V;

输出电压范围: 0.3V~VCC: +0.3 V;

峰值输入电流(任一输人端) :土10 mA;

峰值输人电流(所有输入端): 土30mA;

工作温度: TLC549C: 0C~70~C、OTLC549I :-40C~85C、TLC549M.-55“C~125*C

TLC549 芯片的工作原理:

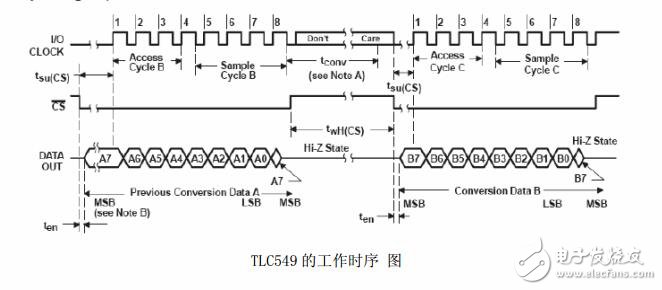

TLC549 带有片内系统时钟,该时钟与I/OCLOCK 是独立工作的,无需特殊的速度或相位匹配。当CS 为高时,数据输DATA OUT 端处于高阻状态,此时I/0 CLOCK 不起作用。这种CS控制作用允许在同时使用多片TLC549时,共用I/OcLOCK,以减少多路(片)A/D使用时的1/0控制端口。一组通常的控制时序操作如下:

(1)将CS 置低,内部电路在测得CS 下降沿后,在等待两个内部时钟上升沿和一个下降沿后,再确认这一变化,最后自动将前一次转换结果的最高位(D7)位输出到DATAOUT 端;

(2)在前四个1/0 CLOCK周期的下降沿依次移出第2、3、4 和第5 个位(D6,D5,D4,D3),片上采样保持电路在第4 个I/0 CLOCK 下降沿开始采样模拟辅人:

(3)接下来的3 个I/0 CLOCK 周期的下降沿可移出第6、7、8(D2,D1,DO) 各转换位;

(4)最后,片上采样保持电路在第8 个I/OCLOCK周期的下降沿将移出第6、7、8(D2,D1,DO) 各转换位。然后使保持功能持续4 个内部时钟周期,接着开始进行32个内部时钟周期的A/D转换。在第8个I/0 CLCOK后,CS必须为高或I /0 LOCK保持低电平,这种状态需要维持36 个内部系统时钟周期以等待保持和转换工作的完成。

如果CS 为低时,I/0 CLOCK 上出现一个有效干扰脉冲,则微处理器,控制器将与器件的I/0时序失去同步; 而在CS 为高时若出现一次有效低电平,则将使引脚重新初始化,从而脱离原转换过程。在36 个内部系统时钟周期结束之前,实施步骤(1)~(4),可重新启动一次新的A/D转换,与此同时,正在进行的转换将终止。但应注意,此时的输出是前一次的转换结果而不是正在进行的转换结果。

若要在特定的时刻采样模拟信号,则应使第8 个I/0 CLOCK时钟的下降沿与该时刻对应。因为芯片虽在第4 个I/0 CLOCK 时钟的下降沿开始采样,却在第8 个I/0 CLOCK的下降沿才开始保存。TLC549的工作时序图如图所示。

tlc549与单片机连接图:

TLC549 可方便地与具有串行外围接口(SPI)的单片机或微处理器配合使用,也可与51系列通用单片机连接使用。与51系列单片机的接口如图5 所示。

tlc549电路连接图

- 相关推荐

- 热点推荐

- TLC549

-

TLC549通用串行输出8位AD转换器相关资料分享2021-03-24 1252

-

如何使用状态机实现对TLC549的采样控制2020-08-07 849

-

TLC549的仿真与逻辑代码问题2018-08-29 2338

-

基于单片机和TLC549的多功能智能照明系统2018-02-19 5712

-

tlc549中文资料汇总_tlc549引脚图及功能_工作原理_特性参数及典型应用电路程序2017-12-19 55567

-

TLC549程序2017-11-22 2846

-

TLC549英文2016-12-16 975

-

TLC549数据手册2016-11-10 1721

-

求8086通过8255读取TLC549的汇编!!2013-04-29 2147

-

基于TLC549工作时序编程技术研究2010-02-11 925

全部0条评论

快来发表一下你的评论吧 !