一种AES密码算法的实现

FPGA/ASIC技术

描述

密码学是保障信息安全的核心技术,应用涉及军事、国防、商贸及人们日常生活的各个方面。2001 年美国标准技术研究所决定用AES 算法逐渐取代日益不安全的56 bit 密钥长度的 数据加密标准(DES)算法。AES算法是迭代分组密码算法,分组长度为128 bit,而密钥长度可为128 bit、192 bit、256 bit,其对应不同的密钥长度相应的迭代循环次数为10轮、12轮、14 轮。现实现的是128 bit 的AES算法[1-2]。

一种AES 算法实现是采用轮展开的流水线结构[3],吞吐量很大可达到10 Gb/s 量级,但消耗大量的逻辑面积。考虑在资源少的FPGA 上实现AES 算法,能满足低端应用的加、解密速度一般不超过100 Mb/s 的需求。现设计采用顺序结构[3],多轮加密共用一个轮运算结构,加密模块和解密模块共用一个密钥扩展模块,能保持较高加解密速率,同时节省了逻辑面积,在50 MHz 时钟下加解密速率可达530 Mb/s。

1 AES 算法描述

AES 算法中的字节表示为有限域上的元素,并在有限域上定义加法和乘法两种运算,运算的基本单位是字节和双字(4 个字节)。AES 算法将128 位的中间结果和密钥都分成16 个字节,构成4×4 以字节为元素的状态矩阵,AES在加解密过程中就是以状态矩阵为操作对象的。加密算法中每一次轮操作都由字节替换、行移位、列混淆和轮密钥加这四个函数组成,最后一次轮操作不含列混淆操作。

2 在FPGA 上实现AES 算法

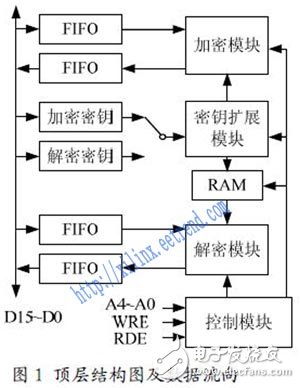

2.1 顶层结构图

该设计的顶层结构图如图1 所示,由控制模块、加密模块、解密模块、密钥扩展模块、随机存储器(RAM)和FIFO组成。接口采用16 位并行数据总线结构。加密数据流向为:明文数据通过数据总线写入16 位入128 位出的FIFO 缓存;由控制模块启动AES 加密模块进行一次加密运算;运算完成输出128bit 密文存入128 位入16 位出的FIFO 中。解密过程与之相同。加密模块和解密模块完全独立,保证模块能同时进行加密和解密运算,以满足快速双向保密通信的需求。

2.2 加解密部分设计

2.2.1 加密模块

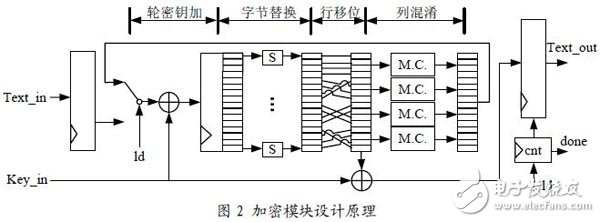

由于输入8 次16 位数据才能提供一个128 bit 明文,这一过程至少需要8 个时钟,因此采用逻辑面积较大的多轮展开流水线结构方式意义不大。该设计采用多轮运算复用一个轮操作结构的顺序方式,设计原理图如图2 所示。

轮运算包括轮密钥加、字节替换、行移位和列混淆4 个部分。其中,轮密钥加只是轮数据与轮密钥进行异或运算,结构比较简单;行移位也只是简单的逻辑连线,几乎不产生时延并且几乎不耗逻辑资源。

字节替换如果采用模乘求逆运算[4]实现,则逻辑延时较长,速度较慢。为加快速度,采用时延小的基于只读存储器(ROM)查找方式的S 盒结构,即输入8bit 数据作为地址而相应数据输出则为字节替换后的8 bit 数据。S 盒结构若采用基于块存储的查找表(LUT)来实现,一个轮运算中16 个S 盒将占用16×128 个LUT,占用逻辑资源较大。可采用FPGA 内部集成的块 RAM 来实现S 盒。

列混淆是系数在有限域上的四次多项式矩阵乘法,输入列向量(X0, X1, X2, X3),输出列向量(Y0, Y1, Y2, Y3),加密过程是在上乘以01、02、03、01,解密过程是乘以09、0E、0B、0D。为了优化用FPGA 逻辑实现,采用一个xtime 函数来实现上的乘02 运算,对输入的一个字节b 做以下变换[5]:xtime = { b[6:0], 1'b0 } ^ ( 8'h1b &{ 8{ b[7]} } )。则列混淆在上所有矩阵乘法就可以通过分解成有限个xtime 运算和异或运算来实现。

轮密钥加、行移位和列混淆三步运算实现的逻辑资源较少并且逻辑时延较小,可以合并在一个寄存器传输层间实现。

2.2.2 密钥扩展模块

密钥扩展模块设计比较简单,只需要4 个S 盒和一个轮常数字计算模块,外加一些异或运算和逻辑连线即可完成。密钥扩展模块也是一个迭代运算的结构,与加密模块的轮运算同步,即每个时钟计算出一轮加密的密钥。

当解密密钥更新时,密钥扩展模块计算出的各轮密钥作为解密的轮密钥,需要按每个时钟存储在RAM 中,解密运算时从RAM 中读取。

2.3 接口设计

模块的外部接口采用了16 位数据总线的接口。由于输入的加密密钥和解密密钥各128 位, 占用地址为128×2/16=16 个。另外,加密需要一个输入明文寄存器和一个输出密文寄存器,解密需要一个输入密文寄存器和一个输出明文寄存器。因此芯片地址数总共20,即需要5 位地址线。接口读写时序的设计以TMS320C5509 型号数字信号处理器(DSP)总线读写时序作为标准。16 位数据线采用双向三态设计。16 位三态口由片选信号CS 和读使能信号RDE 控制,当CS 和RDE 均有效时三态口数值为输出数据寄存器的值以输出数据,否则三态口数值为高阻将数据输入。

3 测试与分析

3.1 加密模块和解密模块功能仿真

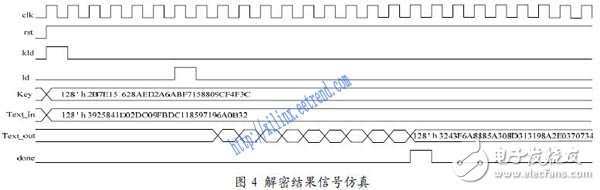

用Xilinx ISE Simulator 分别对加密模块和解密模块进行信号仿真,仿真图如图3 和图4 所示。

两图中text_in[127:0]为输入数据,key[127:0]为密钥,text_in[127:0]为输出数据。在图4 和图5 中,明文均为(3243,

F6A8, 885A, 308D, 3131, 98A2, E037, 0734 H),密钥均为(2B7E, 1516, 28AE, D2A6, ABF7, 1588, 09CF, 4F3C H),密文均为(3925, 841D, 02DC, 09FB, DC11, 8597, 196A, 0B32H),证明其加密和解密正确。

3.2 功能测试

将设计的FPGA 模块连接到TI 的5509 的DSP 开发板的总线扩展口,FPGA 模块通过JTAG 线与计算机连接,DSP开发板通过仿真器与计算机连接。 通过C 程序将明文和密钥写入FPGA 模块,加密后读出密文,解密过程与之类似。通过DSP 测试,结果与3.1 仿真结果完全一致,证明AES算法在FPGA 上准确实现。

使用在线调试逻辑分析软件通过JTAG 口对FPGA 总线接口的信号波形进行采样并显示,地址、数据和控制信号正确。通过加密或解密时连续输出128 bit 结果间隔的时钟数可以计算出,在50 MHz 时,数据处理能力可达530 Mb/s。

4 结语

所采用的AES 算法设计采用16 位并行总线接口,能方便的与上层处理器扩展。在算法实现上,采用多轮运算共用一个轮结构的迭代结构,适用于在较少逻辑资源的FPGA 芯片上实现,满足了较高吞吐率和较小的芯片面积的应用需求,能满足当前各种数据流的加密。算法的实现采用ROM 来实现字节替换,同时优化实现列混淆运算。该设计在赛灵思(Xilinx)公司的xc3s500e 芯片上实现,仅占用4230 个Slice,其中7222 个LUT 和1758 个触发器,消耗的逻辑资源较少。

-

AES加解密算法逻辑实现及其在蜂鸟E203SoC上的应用介绍2025-10-29 200

-

请问如何使用Verilog硬件描述语言实现AES密码算法?2021-04-14 1347

-

什么是AES算法? 怎样快速实现AES算法?2021-04-28 2180

-

TN404_ELF2 AES加密使用指南2022-10-28 924

-

AES中SubBytes算法在FPGA的实现2010-11-09 882

-

Whirlpool的一种改进算法2011-11-30 607

-

一种基于AES图像加密技术改进2015-12-24 1035

-

一文详解AES最常见的3种方案_AES-128、AES-192和AES-2562018-06-29 162954

-

AES加密算法说明2017-11-30 2856

-

面向RCSP的AES算法软件流水实现方法2017-12-01 800

-

基于AES算法研究与设计2017-12-03 834

-

一种并行AES加密方案2017-12-28 1458

-

用matlab实现AES加密算法2018-05-25 2349

-

如何低成本实现AES密码算法的硬件2020-03-19 1467

-

使用FPGA实现类AES分组密码统一框架的详细资料说明2021-03-26 946

全部0条评论

快来发表一下你的评论吧 !