基于Xilinx ISE结合MATLAB对数字系统进行联合设计与仿真的方法设计详解

可编程逻辑

描述

1 数字信号处理FPGA设计实现和验证中存在的问题和解决方法

用FPGA来实现信号处理的算法有可能碰到以下一种或几种情况:

a. 实现复杂的数字处理功能,例如实现DFT、数字滤波等通信信号处理算法;

b. 模块多且功能验证十分繁琐;

c. 数字系统尚包含某些不确定因素,例如环路参数等;

d. 数字系统包含范围较大的反馈环节。

实际设计中碰到的困难主要是以前的设计流程中系统方案和原理性仿真与硬件设计仿真脱节,尤其是在高速数字信号处理FPGA设计实现中没有很好的算法仿真验证手段。

联合设计与仿真的方法针对数字信号处理FPGA设计实现中碰到的问题和困难,提出了有效可行的解决方法,大大提高了数字信号处理算法FPGA设计实现的效率,有较高的推广应用价值。联合设计与仿真的方法主要包括以下3个方面。

a. 分别创建数字系统的MATLAB仿真的数据源产生程序和实现特定功能的系统算法程序以及VHDL设计仿真程序模型;根据硬件性能对MATLAB 中的数据源进行量化,由浮点数转化成定点数据源,把系统仿真(浮点)中的某些功能模块改造成定点模型的MATLAB 模型,比如用定点的Simu-link模块来建立定点模型。

b. 对VHDL源程序需要仿真的部分分层次建立VHDL Testbench文件,把原文件关联进去;在Testbench文件中运用VHDL语言的TextIO程序包实现对输入输出数据的读写,再结合ModelSim仿真软件实现对数字系统的仿真;仿真后输出的测试数据可以在VHDL Testbench文件指定的输出文本文件中找到,它的数据存储格式是按列向量存储的,可以直接被MATLAB读取,做有关数学运算或者数字信号处理运算如FFT等的运算并绘图显示。

c. 特殊功能模块的仿真与验证,如对一些存储器的初始化和仿真以及一些双向总线的仿真都是由特定的测试方法来完成的的。

2 VHDL Testbench的概念和高效的Testbench文件编写

2.1 FPGA测试与验证的基本概念及方法

(1)测试基准

一旦设计者描述了一个设计,必须对其进行验证,以检查是否符合设计规范。最常见的验证方法是在模拟时施加输入激励信号,然后“读”该设计的输出信号。ModelSim等波形仿真软件可以完成这个“读”的功能,但是输入激励信号需要用模拟器来完成。使用模拟器输入激励语言的一个主要缺点是它随着模拟器的不同而不同。

验证的另一个方法是用VHDL编写一个测试模型发生器和要检查的输出,称为测试基准( Test-bench) ,它既提供输入信号,又测试设计的输出信号。由于测试基准也可能产生错误,所以它必须也能被测试。建议既要有VHDL测试基准,又要用环境模型来验证元件,称为系统模拟。VHDL测试基准的建立可以用VHDL语言标准程序包中的TextIO来实现,具体的TextIO在下一节介绍。

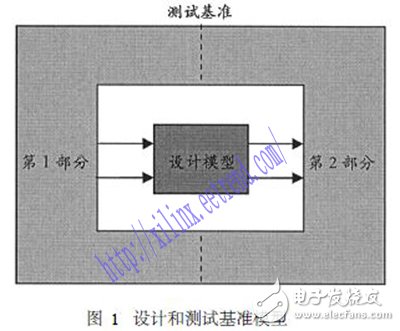

系统模拟的优点是元件的激励由系统仿真的数据源产生,近似于表示实际的模型产生。系统模拟的时间由输入的需要模拟的数据量来决定。在通信信号处理的仿真中,往往需要很大的数据量来验证设计的正确性,所以系统模拟的一个缺点就是所需时间过长。VHDL测试基准的优点是其速度与平台无关,所以在某些情况下,例如前面提到的用FPGA进行信号处理的几种情况,可以对这些情况全部或者部分地建立一个测试环境。图1示出一个测试基准逻辑结构。设计模型接收输入激励(输入信号,第一部分) ,并给出对测试基准的响应(输出信号,第二部分) 。

(2)VHDL中的TextIO

TextIO例程是在VHDL标准中建立的,用它可以读/写文件,这些例程的用法如下:

Read ( ⋯)

Readline ( ⋯)

Write ( ⋯)

Writeline ( ⋯)

为了能使用这些例程,在设计程序中应引用VHDL 的标准程序包,即在VHDL代码的开头应当包含下面的行:

use std. TextIO. all;

这些标准程序包是在进程中对行变量或列变量进行操作,然后在程序中给这些变量进行赋值或引用。

TextIO的一个很重要的应用就是在集成电路设计或FPGA设计中的测试基准中的应用,测试基准是测试方法学中一个很重要的测试和验证工具,它提供了设计模型和外部数据的输入输出接口。具体来说:模型的输入信号可以放在外部文件中,输出信号的期望值可以放在另一个文件中,而且这个文件是以行向量方式存取,所以可以被MATLAB的系统级仿真软件读取。

在测试基准中使用TextIO的方法非常灵活,也相当简单。调用TextIO的缺点是,与普通的VHDL代码相比,其模拟速度往往较快。

有必要指出, TextIO的调用不能被综合,只能用于模拟。

2.2 高效的Testbench文件编写

(1)VHDL Testbench文件实现的功能

VHDL Testbench已经成为验证FPGA或ASIC顶层设计最典型的方法。在VHDL Testbench文件中主要完成以下任务:

·例化被测试的设计单元(DUT) ;

·在Testbench文件中对测试模块引入测试向量;

·输出结果可以在ModelSim仿真软件的波形窗口显示或者作为测试结果向量保存在文本文件中;

·也可以在ModelSim仿真软件中比较测试输出结果和系统仿真期望结果,验证设计的正确性。

(2)VHDL Testbench文件结构

VHDL Testbench文件结构主要包括4部分:实体和结构体声明、信号声明、例化顶层设计模块、测试进程程序。

2.3 自检功能Testbench的程序编写

自检功能Testbench的实现是先通过MATLAB 等系统仿真软件产生一系列期望输出的测试向量,存放在期望输出的向量文件中,然后在VHDL Testbench文件中编写程序,让程序在运行时对预设的不同运行时间间隔的实际输出和期望输出进行比较;如果实际输出结果和期望输出结果匹配,那么这个仿真结果就是正确的;如果实际输出结果和期望输出结果不匹配, Testbench就会在预设的时刻产生差异或者错误报告。这种功能的VHDL Testbench程序是利用VHDL语言的TextIO程序包来实现的。

自检功能Testbench对同步电路的设计来说是很简单的,因为同步电路实际输出结果和期望输出结果的比较可以在同一个时钟沿或者滞后几个时钟周期进行。比较方式取决于具体的设计,比如存储器I/O的Testbench,必须在每次有新数从某个地址读出或者给某个地址写入新数的时候检查其结果;同样,如果某个设计使用了很多的组合逻辑,那么期望输出结果就要考虑组合逻辑的延时。

自检功能Testbench是通过在特定时间对实际输出和期望输出进行比较而自动对仿真结果检查错误,这种仿真方式特别适合中、小规模设计使用。当数据量很大时仿真会很慢,尤其当数据量以指数增加时,编写Testbench会很费时和困难,这时可通过TextIO把实际输出数据导出,联合MATLAB等系统仿真程序对FPGA设计进行验证。后面的应用举例就是使用这种方法来综合验证FPGA设计的正确性。

在VHDL Testbench文件中,仿真输入向量数据和期望输出向量数据都各自存放在向量数据文本文件中,VHDL语言的TextIO程序包被用作从向量文件中读入数据和显示错误信息。

3 应用实例

在某课题数字解调部分位定时误差估计算法设计实现中使用了VHDL Testbench联合MATLAB系统仿真软件,并对在FPGA中实现的位定时算法进行了验证,证明该方法切实可行。

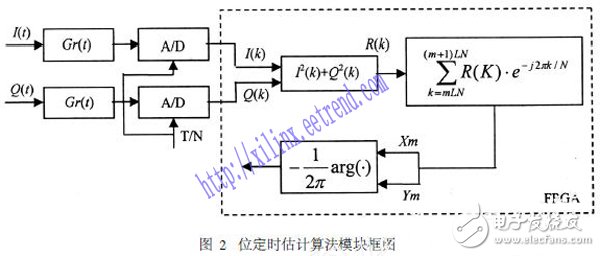

数字解调位定时估计算法框图如图2所示,其中虚线框内部分是要在FPGA中实现和验证的算法。按照FPGA联合设计仿真的方法步骤,首先利用MATLAB创建了该算法的浮点仿真模型,并且验证无误。在此基础上,按照以下步骤进行系统的设计与调试。

第一步,根据MATLAB浮点仿真模型中的数据源产生模块,编写可以产生定点数据(如8比特或16比特量化的有符号数)的定点数据源产生模块;编写实现算法的各模块的MATLAB定点代码;运行程序,产生设计模块输入数据向量和期望输出数据向量,并分别存储在不同文件中。

第二步,根据位定时估计算法,用VHDL语言编程在FPGA中实现该算法,并根据第二节中讲到的VHDL Testbench的写法编写对应的测试基准文件,其中包括VHDL语言的TextIO数据包和在程序中编写读入和写出的程序代码。

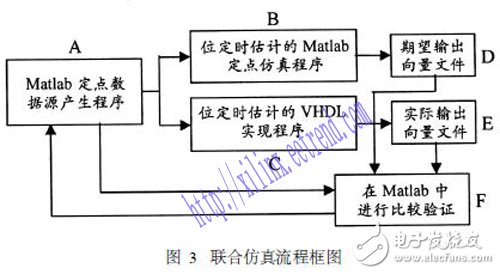

第三步,把定点数据源产生模块产生的定点数据源分别输入MATLAB程序和FPGA程序,如图3所示。产生的输出文件分别作为期望输出向量文件和实际输出向量文件。

第四步,分别对实际输出向量文件中的输出和对应期望输出向量文件中的数据进行分析验证,如果不正确,则重新产生输入数据进行联合仿真;当程序较大时,反复进行几次联合仿真,直到该模块功能和时序仿真都正确为止。

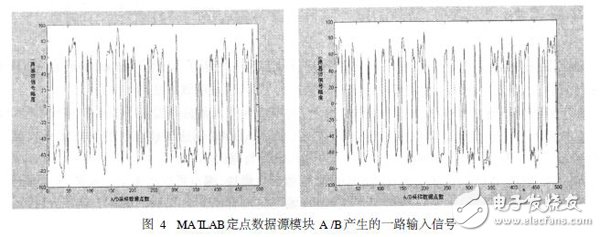

需要指出,在此仿真阶段,输入数据量化要尽可能模拟硬件实际输入数据。图4为MATLAB定点数据源模块A /B产生的一路输入信号,图5为期望输出向量文件模块D和实际输出向量文件模块E在MATLAB中绘制的图形。

从图中可以看出, FPGA测试的输出和MATLAB定点仿真很相似,证明了FPGA设计的正确性。

4 结束语

在电子产品设计领域已经涌现出大量先进的设计技术与设计方法学,并且成功地应用在设计实践中。这些先进的器件技术、设计技术逐步应用在现代信号处理电路的研发中。随着集成电路工艺水平的提高,现场可编程器件FPGA的规模和速度快速增长,这给FPGA的设计实现和仿真验证带来很大困难。尤其是在信号处理算法的FPGA实现中,很难把系统仿真和设计实现仿真有机结合起来;而采用Xilinx ISE结合MATLAB对数字系统进行联合设计与仿真的方法是解决这一问题的有效途径。

-

svpwm的MATLAB仿真的实现2021-04-28 1218

-

ISE联合Modelsim进行仿真2018-01-12 4735

-

ISE和modelsim联合仿真的问题2017-02-21 3203

-

减少Xilinx Ise与Modelsim联合仿真的错误方法2017-02-11 1879

-

LabVIEW与Matlab的联合仿真过程详解2016-04-03 21167

-

《LabVIEW与Matlab的联合仿真过程详解.pdf》2015-12-23 9371

-

【PDF】LabVIEW与Matlab的联合仿真过程详解2015-12-04 3544

-

MODELSIM仿真(适合xilinx ISE)2015-11-30 910

-

Matlab2011b-simulink联合Xilinx 14.2硬件联合仿真问题2015-04-26 3971

-

Xilinx ISE 12.2 调用Modelsim进行行为仿真详解2012-03-05 13124

-

Xilinx ISE 12.2 调用 Modelsim 进行行为仿真详解2012-02-29 10251

-

MATLAB通信仿真及应用实例详解2010-02-08 1285

-

FPGA CPLD设计工具——Xilinx ISE使用2009-07-24 876

全部0条评论

快来发表一下你的评论吧 !