关于XILINX系列FPGA芯片的架构性能剖析

可编程逻辑

描述

XILINX公司拥有多种不同系列的FPGA芯片,随着微电子技术的发展,芯片的结构与功能也发生了相应的变化。本文参考了XILINX系列芯片的相关资料,结合微电子电路相关知识,重点针对Virtex系列芯片,从其基本结构、CLB (可配置逻辑块) 、IOB (输入输出模块) 、可编程内连等方面进行了详细的分析研究。最后通过比较的方式给出了各系列芯片间芯片结构以及性能上的差异。

1 Virtex系列芯片基本概况

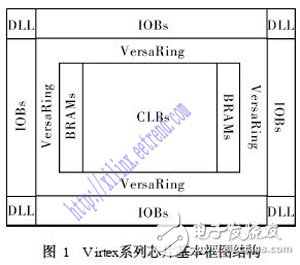

Virtex系列芯片的基本电路框图结构如图1 所示。它主要由可配置逻辑块( Configurable Logic Blocks, CLB)组成的规则阵列构成内部核心部分;周围是输入输出模块( Input/Output B locks, IOB) ;在管芯的四个角上有4个时钟锁相环;遍及整个芯片分布着4个通用低摆率的全局时钟分配网络;在CLB与IOB之间,有两列RAM块,分别位于左右对称的两侧,这一系列的芯片可以把配置数据存在其内部的静态存储单元中,通过这种方式可以实现无限循环次数的重复编程,存储在静态存储单元中的值控制着可配置存储单元及内连资源,这些值在上电时加载到静态存储单元中,如果需要改变系统功能时可重新对其进行配置,同时,它还提供了基于函数发生器的单端口与双端口的分布式RAM。

Virtex系列芯片最多可容纳的逻辑门数为1000000门,系统时钟频率可达200MHz;它采用5层金属板的CMOS工艺。

2 Virtex系列芯片详细分析

1)输入输出逻辑块( IOB)

它提供了包装引脚与内部逻辑之间的接口界面。

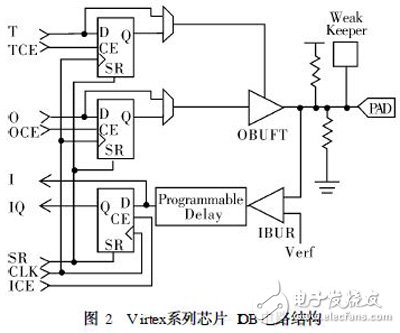

Virtex系列芯片的IOB的电路结构如图2所示。

图2中,三个IO寄存器既可作为D型触发器也作为边沿敏感的琐存器,它们共用同一个时钟,共用同一个置位/复位信号,但各自有独立的时钟以始能信号。对每一个寄存器,输入数据可配置成同步置位、同步复位、异步预置位、异步清零,具体配置可以通过软件编程进行控制。上拉电阻、下拉电阻以及弱保持电路是焊盘的附属器件。配置前,与配置无关的输出均被置于高阻状态,下拉电阻与弱保持电路处于非活动状态,但输入处于激活状态,配置模式中的全局原则控制着上拉电阻的激活,如果上拉电阻没有被激活,所有引脚处于浮动状态。当静电和电压过高时所有焊盘均可处于保护状态之下。

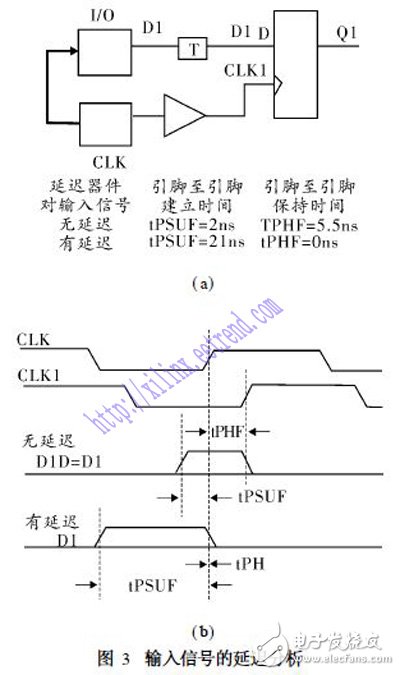

a. 输入通路。通过可编程的输入缓冲把信号直接或经过寄存器的输出送入,信号在送入寄存器前,由可编程延迟器件对输入信号进行延时配置[ 2 ] ,使信号的延时与FPGA里时钟的分配延时相同,故输入信号焊盘与输入时钟焊盘之间的保持时间为0;如果延迟器件不对输入信号进行延时处理,则输入信号与芯片输入时钟之间的保持时间不为0。如图3所示。

图3 ( a)中,电路图中左边的红色箭头表示从CLK焊盘到IO焊盘之间的延迟。T单元实现图3 ( b)所示延时功能,它可以决定是否对输入信号D1进行延时。若有延时,焊盘与焊盘之间的保持时间为0,但此时的建立时间增加到21ns;若无延时,保持时间为5. 5ns,建立时间为2ns。所以,当延时编程器件对输入信号进行的延时是以延长建立时间作为代价的,而且代价还比较大,相当于无延迟的10倍! 图3 ( b)是相应的对输入信号是否进行延迟时的时序图。另外,输入信号对于CLK1 的保持时间是0,建立时间图中未画出;CLK1对于CLK也有一个延迟,这是时钟信号通过时钟缓冲以及全局时钟分配网络在整个芯片上对时钟进行分配过程中产生的延迟。

b. 输出通路:图2中,输出信号可以经过输出缓冲直接输出,也可先进入寄存器然后再进行输出。每一个输出焊盘上有一个弱保持电路,它监视着焊盘上电压的微妙变化,并对之进行调整以匹配输入信号。

2)可配置逻辑块(CLB)

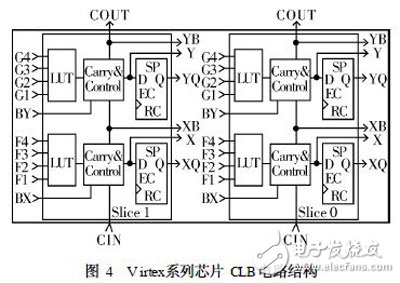

Virtex系列的CLB电路结构如图4所示。

CLB的基本组成单元为LC (逻辑单元) 。图中列出了两个LC,每个LC包括两个4输入的函数发生器、两个进位逻辑和两个存储单元。

a. LUT与函数发生器。函数发生器被用来实现一个4输入的查找表,每个查找表可提供一个16 ×1bit的同步RAM,或形成一个可以存储随机的突发的快速数据的16bit的移位寄存器;同一个LC中的两个部分可组合成一个16 ×2 - bit或32 × 1 - bit的同步RAM,或者组成一个16 x 1 - bit的双端口的同步RAM。

b. 存储单元。它可以被配置成D边沿触发器或者电平敏感的琐存器,输入可以是LUT的输出也可是直接来自于LC的输入信号,旁路掉函数发生器。

c. 快速进位逻辑。为高速算术函数的运算提供了快速运算进位功能,它支持两个独立的进位链。

3) RAM块

Virtex系列中包含64个CLB的芯片中每列有16个RAM块,所以共有32个RAM块。每一个RAM块都是完全同步的双端口的4096 - bit的。每个端口都有独立的配置信号,且每个端口的数据宽度都是各自独立配置的。

4)可编程的布线阵列

包括以下几种布线。

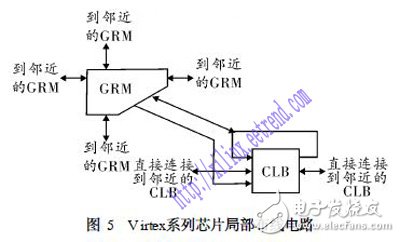

a. 局部布线: Virtex系列的局部布线有三种方式的连接,即: LUT、触发器、常规布线矩阵(GRM)之间的连接; CLB内部把同一个CLB的输出反馈回来作为自身LUT输入的连接,这种连接提供了最小的延时;在相邻的CLB间提供水平连接,这种连接消除了信号在GRM中的延迟。这三种方式如图5所示。

b. 常规布线: Virtex系列中在CLB的通道中,水平与竖直方向各有24根单长线连入GRM中,通过GRM中的可编程开关实现是否互连,以实现CLB 间的互连;四个方向各有12条带缓冲的16进制线每跨过6个CLB从一个GRM汇入下一下GRM;每个CLB分别在水平与竖直方向相邻着12根带缓冲的双向的长线,长线的长度与CLB区域的长或宽相同。

c. IO布线:这是一种在芯片的周围附加的布线资源,它提供了CLB 阵列与IOB 的交换界面,称为多功能环,同时,除了能把IOB与CLB连接起来之外,还可以实现引腿之间信号的交换。

d. 直接连线:一些信号需要专门的连线来达到最优性能的实现,直接连线便实现了这一目的,在Virtex芯片中,有两类这样的信号:在两个独立网络中,每个CLB传输进位信号给相邻的CLB;水平布线资源在一个通道内提供4条三态总线来与CLB交换信号。

e. 全局布线:它为时钟及其实遍及整个芯片的多扇出信号提供分配通路。Virtex包括两类全局布线资源:主全局布线与次全局布线。主全局布线由4个以最小摆率来分配高扇出时钟信号的有专门输入引脚的全局网络构成。次全局布线包括24 条主干线, 12 条穿过芯片上端, 12条通过芯片下端,通过这些线,每一个CLB列中可以有12条信号分布式地通过这列中的12条长线。

5)时钟分配

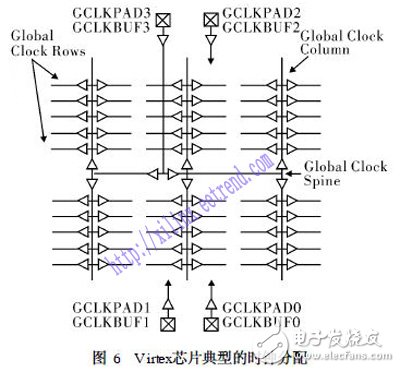

通过主全局布线Virtex在整个芯片上提供高速、低摆率的时钟分配。典型的时钟分配如图6所示。它提供了4个全局时钟缓冲器, 4个专门的时钟焊盘分别与每一个全局时钟缓冲器相匹配,全局缓冲的输入可以来自于这些焊盘,也可以来自于常规布线。

时钟延迟琐定环。与每一个全局时钟缓冲器相关联的是全数字的延迟琐定环,它可以有效地消除时钟输入焊盘与遍及整个芯片的时钟输入之间的摆率。每个DLL可驱动两个全局的时钟网络,DLL监视着总时钟信号与被分配开的时钟信号,自动调整时钟延迟因素,它可以精确地实现从时钟从焊盘输入至其边沿到达内部触发器时延迟1 - 4个时钟周期的功能。这个闭合的环通过确保时钟边沿同步到达内部触发器来有效地消除时钟分配延迟。为了保证系统时钟在配置完毕刚开始启动FPGA时能够正常工作,DLL 可以延迟配置的完成直到它已经琐定了时钟为止。

3 结束语

本文仅给出了Virtex系列芯片的内部基本结构与性能分析。现结合本文分析,对XILINX其它各系列芯片结构与性能进行如下比较。

器件容量与系统速度的提高。在芯片所容纳的晶体管的门数上由较早XC3000 系列的最高7500 门的容量到Spartan - II系列的200000门直至Virtex系列的1000000门容量;在系统的时钟速度上由原来的不足百兆到最后的200多兆,实现了质的飞跃。

与CLB相关的内置器件功能的增多。XC4000在XC3000的基础上,增加了快速进位逻辑,从而提高了器件进行多种逻辑运算的能力与速度。

IOB方面。XC4000的IOB 中除了对输出配置较3000更加灵活外,还增加了一个输出的MUX,它可以在输出通路中实现多种基本的函数运算;而在Spartan- II系列与Virtex系列的IOB中则更加强了对延时的控制,通过专有的延时电路可以实现信号与时钟的良好匹配。

系统内连方面, Spartan - II系列与Virtex系列的内连,连接方式比XC4000更加条理化与模块化,随着器件内部时钟的大量使用,这两系列把时钟的分配单独划分出一系统,建立了单一的时钟分配网络。

-

AMD UltraScale架构:高性能FPGA与SoC的技术剖析2025-12-15 736

-

Xilinx fpga芯片系列有哪些2024-03-14 6368

-

简述Xilinx 7系列FPGA芯片相关知识2023-11-27 1993

-

XILINX FPGA 芯片整体架构是如何构成的2021-10-29 3481

-

Xilinx 7系列FPGA简介--选型参考2021-01-30 3070

-

关于Xilinx FPGA如何获取FPGA的Device DNA2021-01-02 5744

-

怎么选择Xilinx FPGA芯片?2020-12-23 2834

-

Altera、Xilinx、Actel这些芯片公司的FPGA系列产品都有哪些特点?2018-08-20 11708

-

Xilinx系列FPGA芯片IP核详解2017-06-06 31300

-

直击关于Xilinx UltraScale架构、Virtex和Kintex UltraScale架构FPGA 和最新的Vivado开发工具的9大要点2017-02-08 1131

-

Xilinx_FPGA系列入门教程(一)—如何搭建Xilinx2016-01-18 897

-

选择赛灵思(Xilinx)FPGA 7系列芯片的N个理由2012-09-06 4529

-

全新赛灵思(Xilinx)FPGA 7系列芯片精彩剖析2012-08-08 3806

-

xilinx公司的7系列FPGA应用指南2012-08-07 2343

全部0条评论

快来发表一下你的评论吧 !