基于Xilinx FPGA特点的嵌入式Bootloader设计与实现

可编程逻辑

描述

Bootloader程序是指嵌入式系统在正常工作之前,配置系统运行环境,引导操作系统的一小段程序。通过这段程序,我们可以初始化硬件设备、建立内存空间映射等,从而将系统的软硬件环境带到一个合适的环境,为系统的正常运行做好准备。对于不使用操作系统的嵌入式系统而言,应用程序的运行同样也需要依赖一个准备好的软、硬件环境,因此从这个意义上来讲,BootLoader程序对于嵌入式系统是必需的。

BootLoader程序与硬件系统密切相关,依赖于具体的嵌入式板级硬件设备的配置。比如板卡的硬件地址配置、微处理器的类型和其他外设的类型等。也就是说,即使是基于相同嵌入式微处理器构建的不同嵌入式目标板,BootLoader程序也不是完全通用的,仍需要修改其源程序。

与ARM等嵌入式系统的启动过程所不同的是,FPGA必须先将内部硬件逻辑配置完成之后,才能运行程序代码。虽然可以直接将程序代码例化到片内BRAM中,但是由于FPGA内部的BRAM资源有限,而且硬件逻辑配置时就会占用其中的资源,因此遇到大型系统设计时(例如带有TCP/IP协议的大型程序),片内BRAM资源不够,就必须使用外部的RAM来储存程序代码和堆栈,这就需要设计Bootloader程序来完成用户程序的引导。

本文结合Xilinx FPGA的特点详细给出了Bootloader程序设计和实现过程。本设计所实现的Bootloader程序是在FPGA硬件配置完毕之后在MicroBlaze软核处理器上运行的一段启动代码,用来把Flash中的用户程序传输至外部RAM,并引导系统从用户程序中开始运行。

一、系统硬件平台的实现

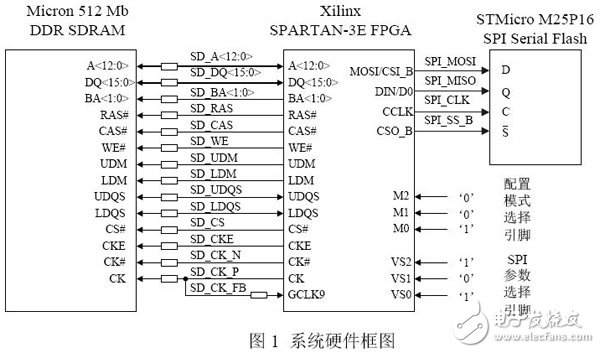

本设计的实现是以Xilinx公司的Spartan-3E FPGA、STMicroelectronics公司的SPI串行Flash(M25P16)、Micron Technology公司的DDR SDRAM (MT46V32M16)为主要器件构建硬件平台。下图(图1)为系统硬件框图。

基于SRAM工艺的FPGA是易失性的,系统掉电以后其内部配置数据将丢失,因此需要外接存储器件保存其配置数据,比如外接Flash芯片。

本设计选择的是STMicroelectronics公司的SPI 串行 Flash(M25P16),容量是16Mbit。基于SPI接口的串行Flash的配置方式不需要另外的单片机或CPLD进行配置控制,简化了电路设计。同时所需的FPGA引脚较少,节省了FPGA芯片的管脚资源,对于需要诸多外设的复杂系统的设计是十分有利的。

Xilinx公司的Spartan-3E系列FPGA支持多种配置方式,因此需要配置模式选择管脚来选择SPI方式进行启动配置。因此3个模式选择管脚应该被配置SPI模式即M[2:0]=0x01。同时还需要配置FPGA的SPI参数选择管脚,本设计配置为VS[2:0]=0x03。

本设计中RAM是作为系统运行时,用户程序储存,用户数据储存,堆栈等的存储器。所以可以选择多种类型的器件,比如SRAM,DDR SDRAM。本设计使用的是Micron Technology公司的DDR SDRAM (MT46V32M16),是一片容量为512 Mbit (32M x 16)的16位总线宽度的芯片。由于DDR SDRAM是高速器件,要注意时序问题,所以在PCB布线时要布等长线,必要时使用蛇形线来实现等长线。该芯片使用SSTL2_I电压标准(2.5V),而FPGA的同一个Bank的I/O引脚只能使用一个电压标准,所以DDR SDRAM的引脚应连接在FPGA的同一个Bank上。这样在分配FPGA的Bank电压时,不同I/O引脚电压标准的外设使用不同的Bank,以避免引发冲突。

二、系统的软件设计:

本系统的配置文件设计采用了IP(Intellectual Property)资源复用的设计方法。IP资源复用是指在集成电路设计过程中,通过继承、共享或购买所需的智力产权内核(IP),然后再利用EDA工具进行设计、综合和验证。

Xilinx公司对其公司的FPGA芯片提供了专用开发工具EDK(Embedded Development Kit) 。此工具包含了各种与嵌入式系统开发相关的IP。本系统的设计即是在EDK中完成。开发流程分为硬件逻辑设计流程和软件设计流程。

1、硬件逻辑设计流程

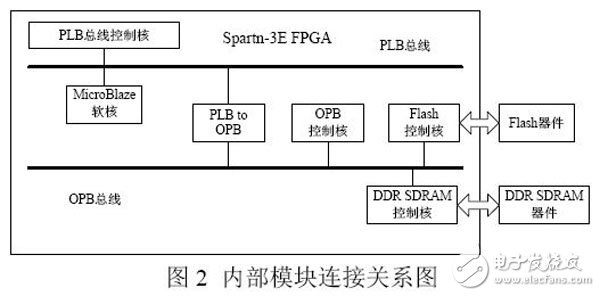

在硬件逻辑开发流程中,首先根据系统需求在EDK中选择IP核,按照系统架构进行连接和组合。本系统以MicroBlaze软核处理器为中心,EDK中提供了两种同样符合IBM CoreConnect标准的总线:PLB(Processor Local Bus) 和OPB(On-Chip Peripheral Bus)供MicroBlaze软核使用。PLB总线和OPB总线的工作频率为50MHz。OPB为32位总线,主要用于与外部设备相连接;PLB为64位总线,用于高速IP核之间互连。PLB与OPB的通信是通过转换访问控制IP核(PLB to OPB)完成的。

本设计的用户程序的运行需要外部存储空间,因此在OPB上为MicroBlaze外接DDR SDRAM内存芯片。MicroBlaze通过挂载在OPB总线的DDR SDRAM控制IP核从DDR SDRAM的读写数据。由于配置文件存储在SPI 接口的Flash中,MicroBlaze通过 SPI控制 IP核,对SPI Flash存储器进行读写,此核也使用OPB总线与MicroBlaze处理器相连接。系统启动时需要先运行BootLoader引导程序,这段代码需要配置在系统的BRAM中,所以Block RAM (BRAM) IP核也是必须的。系统调试时还需要串口连接PC机,所以用于控制串口的OPB UART IP核也是需要的。

EDK根据用户选用IP核搭建出的系统结构,生成MHS(Microprocessor Hardware Specification)文件。此文件中主要定义了系统硬件细节、MicroBlaze软核、SPI控制IP核等的具体配置参数、系统所需的各种存储空间的地址分配。MHS文件生成后,EDK根据此文件以及FPGA的其余功能文件一起,综合生成下载配置文件,硬件设计部分完成。整体连接关系如下图(图2)所示。

2、软件设计流程

完成了以上各项选择工作,接下来就可以开始进行实际的Bootloader程序设计了。由于本设计处理器首先执行Boot Loader的代码,再引导至用户程序。因此,软件部分的设计应包括Boot Loader程序的设计,系统及用户程序设置,配置文件制作三部分。

2.1、Bootloader程序设计

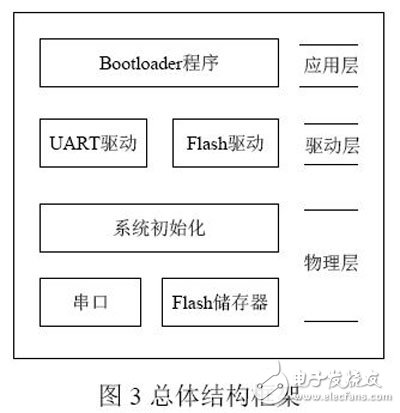

Bootloader的总体结构框架如下图(图3)。Bootloader主要由驱动程序和应用程序两部分组成。这样的分层结构有利于快速的开发和移植。驱动程序负责驱动串口和SPI Flash。应用协议负责对系统进行引导。

系统加电或复位后,处理器通常都从预先确定的地址上取指令。一般来说处理器复位时都从地址0x00000000处取它的第一条指令。而嵌入式系统通常都有某种类型的固态存储设备(比如:ROM、EEPROM或FLASH等)被安排在这个起始地址上。因此在系统加电或复位后,处理器将首先执行存放在起始地址处的程序。通过开发工具EDK可以将BootLoader程序定位在起始地址开始的存储空间内。所以,BootLoader程序是系统加电后,用户应用程序运行之前,首先必须运行的一段代码。对于MicroBlaze软核处理器,第一条指令是从0x00000000地址取出的,此地址分配给了可引导的挂载在PLB总线上的BRAM存储器。

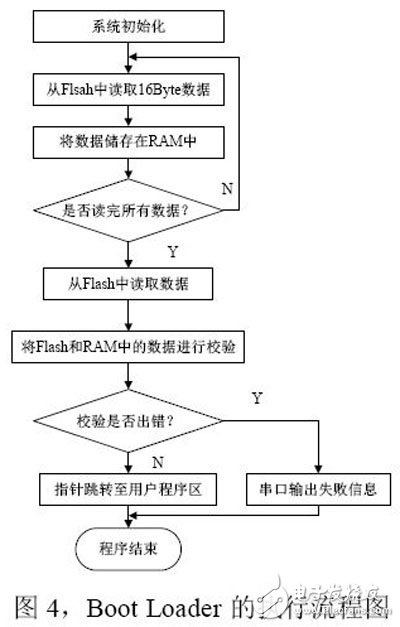

BootLoader的通常包括以下主要步骤(以执行的先后顺序):

1)硬件设备初始化。

2)复制用户程序到RAM空间(DDR SDRAM)。

3)校验已复制的用户程序。

4)指针跳转到预先设定的用户程序RAM空间首地址。

下图是Boot Loader的执行流程图。

Boot Loader主要内容及其代码实现:

首先初始化SPI控制器,其中XPAR_SPI_FLASH_BASEADDR是SPI Flash器件的首地址。

Initialize_Spi_Controller(XPAR_SPI_FLASH_BASEADDR);

XSpi_mEnable(XPAR_SPI_FLASH_BASEADDR);

其次复制SPI Flash内的代码至DDR SDRAM,BOOT_SECTOR参数是Flash中存储用户程序的段首地址,本设计中取为0x60000,注意这里的地址要与之后制作的配置下载文件的相应参数保持一致。WORDS_TO_COPY参数是用户程序的最大长度,本设计取值为0x10000,即64KB。destination_location参数是由* destination_location = (unsigned char *) DESTINATION_ADDR而来,DESTINATION_ADDR为DDR SDRAM在系统中的首地址,也就是用户程序将要存贮在DDR SDRAM区间的首地址。

M25P16_start_read (XPAR_SPI_FLASH_BASEADDR, BOOT_SECTOR, 0x00, 0x00, SCK_FASTER_THAN_20MHz);

for (i = 0; i 《 WORDS_TO_COPY/16; i++)

{

spi_transfer(my_send, my_receive, 16);

for (k=0; k《16; k++)

*destination_location++ = my_receive[k];

}

M25P16_end_read (XPAR_SPI_FLASH_BASEADDR);

再次,对复制的代码进行部分校验:

destination_location = (unsigned char *) DESTINATION_ADDR;

M25P16_start_read (XPAR_SPI_FLASH_BASEADDR, BOOT_SECTOR, 0x00, 0x00, SCK_FASTER_THAN_20MHz);

for (i=0; i《150; i++)

{

spi_transfer(my_send, my_receive, 16);

for (k=0; k《16; k++)

{

if (my_receive[k] != *destination_location++)

{

print(“\n\r !ERROR! File not copied correctly\n\r”);

while(1);

}

}

}

M25P16_end_read (XPAR_SPI_FLASH_BASEADDR);

最后进行指针跳转,跳转到用户程序所在位置:

boot_app = (int (*) (void)) DESTINATION_ADDR;

boot_app();

while(1) { ; }

2.2、系统及用户程序设置

在实际应用的时候,系统中除了Bootloader程序,还会有实现嵌入式系统功能的用户编写的应用程序。也就是说,在EDK环境中将会有两个工程。首先需要将Bootloader工程例化到BRAMs中,即系统会先运行Bootloader程序。其次,需要修改用户程序存放的地址空间,即将用户程序写入DDR SDRAM的首地址,本设计将用户程序存放在以0x44000000开始的DDR SDRAM的地址空间。之后,还需要修改用于生成下载文件的配置参数文件bitgen.ut,将“-g StartUpClk:JTAGCLK”修改为“-g StartUpClk:CCLK”。这是因为从外部RAM配置FPGA时,外部RAM的时序将由FPGA提供,而不是由JTAG接口的时钟信号线来提供。FPGA通过它的CCLK引脚输出时钟信号,引导整个配置过程。

2.3、配置文件的制作

由于总体配置文件是由包含Bootloader及硬件平台的系统配置文件和用户程序文件两部分所组成。所以无法利用EDK工具直接生成。下面将给出制作系统配置文件的主要过程。

首先,利用Xilinx公司的ISE软件的iMPACT工具将原系统配置文件转化为可下载至Flash的MCS文件。

其次,将系统编译用户程序生成的ELF文件(Executable and Linkable Format)转化为二进制文件,再利用Xilinx公司提供的二进制文件转化工具(xbitread.exe)将二进制文件转化为十六进制文件。

第三步,利用Xilinx公司的MCS文件制作工具(xmcsutil.exe),将十六进制用户程序文件转化为可下载的MCS文件,然后将第一步生成的MCS文件和刚才生成的MCS文件合并为最终的配置文件。

最后,使用iMPACT工具通过JTAG口,将配置文件下载至Flash中,整个系统构建完毕。

结束语

基于Xilinx FPGA嵌入式Bootloader的设计方法已经在省部级项目“用于强力输送带的高速X射线探测器系统”中得以实现。通过这种设计,该系统可以进行灵活的修改和升级。Xilinx公司的Spartan-3E/A系列芯片,以及目前最高端的Virtex5系列芯片,都支持SPI启动方式,因此这些FPGA器件均可按本文提出的系统架构设计整个系统,该设计方法具有广泛的适应性。

-

基于Xilinx ZYNQ7000 FPGA嵌入式开发实战指南2024-12-10 978

-

fpga是嵌入式吗2024-03-14 5627

-

基于ARM的FPGA嵌入式系统实现2021-07-30 1286

-

基于Xilinx FPGA的嵌入式系统该怎样去设计?2021-04-30 1278

-

单片机/ARM/FPGA/嵌入式系统的特点2021-02-01 1952

-

基于FPGA的嵌入式Linux操作系统解决方案2017-11-24 7107

-

基于Xilinx FPGA的嵌入式串行千兆以太网设计2017-11-23 4086

-

Xilinx FPGA上的嵌入式系统设计实例2017-10-31 3187

-

FPGA实现嵌入式系统2016-05-10 570

-

基于网络加载的嵌入式BootLoader的设计与实现2013-01-16 3104

-

基于Xilinx MicroBlaze的嵌入式I/O系统设计2011-05-14 1030

-

Xilinx嵌入式扩展处理平台2010-05-23 414

-

嵌入式系统Bootloader开发移植2010-02-11 748

-

如何用FPGA实现嵌入式系统2009-04-02 8024

全部0条评论

快来发表一下你的评论吧 !