基于FPGA的高速PCB的设计

FPGA/ASIC技术

描述

随着现场可编程门阵列(FPGA)已发展成为真正的可编程系统级芯片,利用这些芯片设计印制电路板(PCB)的任务变得愈加复杂。要完全实现FPGA 的功能,需要对PCB 板进行精心设计。

采用高速FPGA 进行设计时,在板开发之前和开发期间对若干设计问题进行考虑是十分重要的。由于I/O 的信号的快速切换会导致噪声产生、信号反射、串扰、EMI 问题,所以设计时必须注意:

(一)电源过滤和分布

所有电路板和器件上干净、平台分布电源Vcc 可以减少系统噪声。

滤除由供电源处产生的低频(<1kHz)噪声,建议就近供电源入口处放置100uF 的电解电容;若使用电压调整器,直接放置电容到最终给器件供电的Vcc 处。电容不经滤除供电源产生的低频噪声,而且也能为许多输出切换同时发生时提供额外的电流。

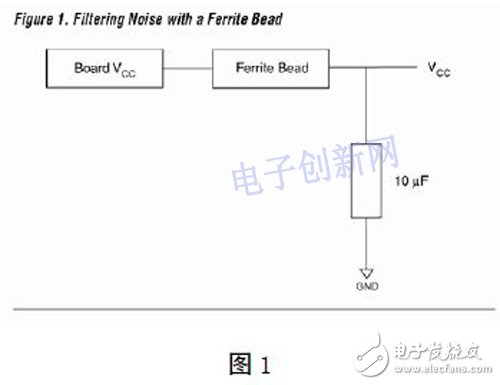

另一种滤除供电源噪声的方法是串入一个铁氧体磁珠,并就近磁珠放置一个10uf~100uF 的旁路电容。一个合理的终端、布局、滤波的设计不需要磁珠,使用一个0 欧姆的电阻取代即可。

为了滤除器件中的高频噪声,建议就近Vcc 和GND 放置退耦电容。

电源分布也会影响系统噪声。总线分布的电源和电源面(独立电源层)都会散布电源到PCB 中。通常两层板的电源采用总线分布式,PCB 的密度限制了走线宽度,电源总线有DC 阻抗,总线上最后的元件接收到Vcc 可能会被削减了最多0.5V。因此,建议使用独立的电源层传播电源,可以有效降低DC阻抗。

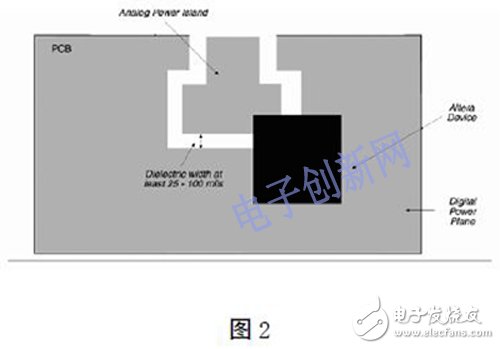

关于模拟电源和数字电源,如果无法做到使用独立的层,那么应该进行电源平面的切割。图2 就是PLL 电源供电隔离的例子。

减少电源分布产生的系统噪声:

1.为平坦式电源分布使用独立的模拟电源供电;

2.PLL 电源供电避免走线和多信号层;

3.靠近PLL 电源供电面仿真一个地层面;

4.只能把模拟和数字元件放置在它们相应的地平面上;

5.使用磁珠隔离PLL 供电源和数字供电源。

(二)传输线和信号走线

快速切换导致噪声产生、信号反射、串扰、地反弹的不同程度,取决于PCB 原材料结构特性。PCB 板的介电常数Er,

决定了信号在板上的传输速率,下面的公式即介电常数和信号传播速率的关系(C=光速=3×(10 的8 次方)m/s):

Vp= C/(Er 开根号)

计算信号在PCB 板上的传播延时Tpd=l/Vp 。

一条信号走线是采样集总线还是分布线取决于信号切换时间(Tr)是否大于4 被的Tpd 。

集总线:Tr > 4 × Tpd

分布线:Tr < 4 × Tpd

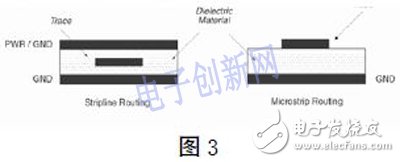

微波传输线和带状传输线的走线如下:

(三)时钟信号布线

推荐以下的时钟布线技巧:

1.避免过多的绕转,时钟走线应该尽可能的走直线;

2.尽量让时钟信号只走一个信号层;

3.时钟信号传输中避免打过孔,因为过孔会导致阻抗变化和反射;

4.以微波传输线方式走时钟信号线(顶层更合适);

5.靠近外层布地面以最小化噪声干扰,如果你使用内层走时钟信号,使用地平面夹着一减少延时;

6.合适的终结时钟信号线。

(四)差分信号走线

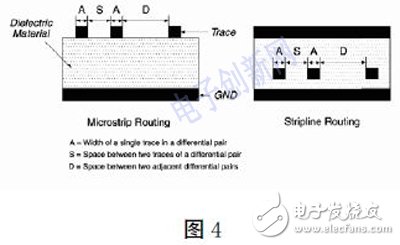

推荐以下的差分信号走线技巧:

1.保证图中的D > 2S 以最小化串扰;

2.在信号离开器件后,尽可能的靠近两条差分信号对,最小化信号反射;

3.在两条差分信号对的整个走线过程中保持恒定的距离;

4.保持两条差分信号对的走线长度一致,最小化偏斜和相位差异;

5.避免使用过孔,最小化匹配阻抗和感应系数。

(五)阻抗匹配和终端设计

为了消除信号反射,源阻抗Zs 必须等于走线阻抗Zo,也必须等于负载阻抗ZL。负载阻抗通常会高于走线阻抗,走线阻抗高于源阻抗。为了消除信号反射,串入或者并入一些电阻达到ZL 或Zs 与Zo 相匹配。

并行方式很多,下面介绍常用的串行匹配方式。串行匹配电阻主要是为了削弱次级反射。经验值推荐为33 欧姆。例如我们常在时钟信号的走线上串入一个33 欧姆的电阻。

(六)串扰

串扰是指并行走线之间有害的耦合。两种类型的串扰:前向(电容性的)和后向(感应性的)。前向串扰主要是由于两个长的并行信号之间的相互电容导致,其中一个信号跳变时会影响另一个信号线。后向串扰常发生在磁性区域,其中

一个信号对另一个信号的影响。

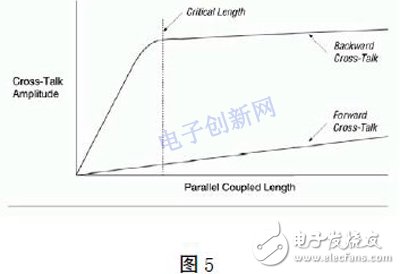

下图是并行走线的长度与串扰程度的关系。

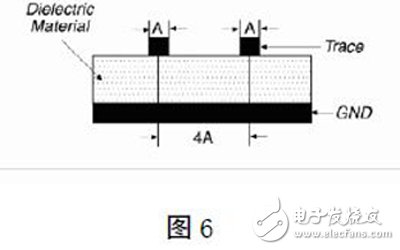

为了有效减低并行走线间的串扰,必须保证两个并行走线的信号的中心距离大于4 倍的走线宽度,如下图。

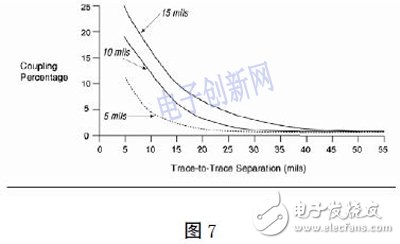

此外,如果它们之间的走线距离无法得到保证,那么拉近地面与并行走线信号间的距离也可以有效削弱串扰的影响。下面是不同的地平面与信号间的距离对信号串扰的影响程度。

(七)EMI 问题和调试

印制电路板引起的电磁干扰与电流或电压随时间的变化,以及电路的串联电感直接成比例。高效的电路板设计有可能把EMI 最小化,但不一定完全消除。消除“入侵者”或“热”信号,以及适当参考接地平面发送信号,也有助于减少EMI。最后,采用当今市场很常见的表面贴装元件也是减少EMI 的一种方法。

调试和测试复杂的高速PCB 设计已越来越困难,因为某些传统的板调试方法, 比如测试探针和“ 针床式(Bed-of-nails)”测试仪,可能不适用于这些设计。这种新型的高速设计可以利用具有系统内编程功能的JTAG 测试工具和FPGA 可能带有的内建自测试功能。设计人员应该使用相同的指导方针来设置JTAG 测试时钟输入(TCK)信号作为系统时钟。此外,把一个器件的测试数据输出和另一个器件的测试数据输入之间的JTAG 扫描链线迹长度减至最短也是相当重要的。

上述几点结合起来就可以实现一个具有稳定的可制造性的可靠设计。所有这些因素的仔细考量,加上正确的仿真和分析,就可以把电路板原型中发生意外的可能性降至最小,并将有助于减轻电路板开发项目的压力。

-

FPGA的PCB板高速电路板设计2022-11-02 2457

-

72 高速PCB Layou 设计,欢迎咨询。高速PCB Layou 设计,欢迎咨询。车同轨,书同文,行同伦 2022-08-04

-

利用高速FPGA设计PCB的要点及相关指导原则有哪些?2021-04-25 979

-

如何使用Xilinx的FPGA对高速PCB信号实现优化设计2021-01-13 1116

-

如何利用高速FPGA设计PCB?2019-08-20 915

-

基于高速FPGA的PCB设计技术介绍2019-07-10 2282

-

在FPGA高速AD采集设计中的PCB布线解决方案浅析2019-03-07 7350

-

基于高速FPGA的PCB设计2018-09-21 1690

-

基于高速FPGA的PCB版图设计2018-08-30 1913

-

高速FPGA PCB设计指南2012-08-16 2746

-

基于高速FPGA 的PCB 设计技巧2012-08-06 2842

-

基于高速FPGA的PCB设计技巧2012-05-15 1497

-

基于高速FPGA的PCB设计技术2009-09-20 389

全部0条评论

快来发表一下你的评论吧 !