基于FPGA的双线性CFA插值算法的设计

FPGA/ASIC技术

描述

摘 要:实现了基于FPGA 的双线性CFA 插值算法。该算法的处理对象是每个像素为8 bit的XGA @15 Hz 的Bayer 模板数据,目的是能得到每个像素是24 bit 的XGA @15 Hz 的彩色图像数据。输入的数据先进入缓存模块,缓存模块是由FPGA 内部的双口的RAM 构成,从缓存中输出的数据被分成奇行组和偶行组,然后奇行组的数据经选择器进入奇行奇列运算块和奇行偶列运算块,偶行组的数据经选择器进入偶行奇列运算块和偶行偶列运算块,最后在插值控制模块的作用下,各运算块处理的数据经输出选择器输出。

像数码相机这样的数字图像设备,考虑到成本和包装, 输出的一般是贝尔(Bayer ) 模板[1 ] CFA(Color Filter Array) 图像,需要通过CFA 插值算法来获得全彩图像。

在实现算法时,通常需要专用的DSP (digital signal processing) ,后然采用C 语言或者其他语言编程进行实现;随着半导体技术的发展, FPGA (field pro-gramming gate array) 作为可编程芯片,其集成度也已达上千万门, FPGA 的可编程特性使其在SOC( system on a chip) 中发挥着越来越重要的作用,这样就产生了用FPGA 直接实现算法,而不需要再用价格昂贵的DSP ,笔者就尝试基于FPGA 实现CFA插值算法。

1 双线性插值算法

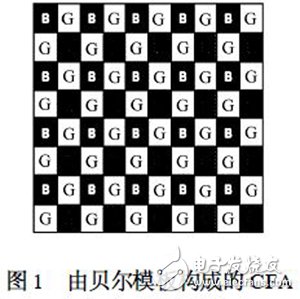

双线性插值算法[2 ,3 ] 是非自适应算法的一种,输出的图像使用邻近像素中相同颜色成份做线性平均计算来补偿每个像素丢失的颜色。如图1 中,像素(2 , 3) 仅有蓝色成份。因此丢失的绿色部份可通过求其上、下、左、右像素的绿色成份的平均值得到。同样,丢失的红色可通过对相邻四个对角上的像素的红色成份求平均值。这种算法可以被视频所接受,因为人类的眼睛不容易在动态的两帧视频中查觉到模糊。

2 双线性插值的模块化设计

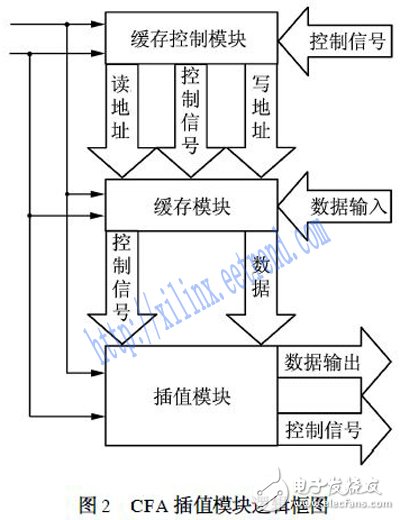

整个设计采取自顶向下的模块化设计[4 ] 方法,代码采用VHDL 语言进行编写,顶层模块定义为CFA 插值模块,定义输入输出接口信号、复位、时钟信号,并且描述了内部各子模块的逻辑连接关系。顶层的下层是由3 个模块构成,框图如图2 所示,设计内容如下:

1) 缓存控制模块。设计了两个控制器,其中一个是写控制器,另一个是读控制器。写控制器主要由一个12 位的计数器构成,用高两位对4 个存储体进行选择,低10 位用来产生相应的地址,配合输入的写信号对缓存的进行写操作。读控制器主要由一个10 位的计数器构成,产生对4 个存储体进行读操作的地址。

在此模块的设计中,考虑到实时处理的因素,在每一帧图像进来时先写满两个存储体,每个存储体的长度刚好等于每行有效像素的个数,也既是存储了两行有效像素,在写到第3 行的第3 个有效像素时,进行存储体的读操作。

缓存存放数据的顺序是这样的,最初的一帧图像的第1 行有效数据存放在1 号存储体,依次存放下去,第5 行数据再存放到1 号存储体,这样循环下去即可,存完一帧后,写控制器复位,下一帧来时按上述操作进行,如此往复。

缓存控制器对缓存的写操作是同一时刻只对一个存储体进行操作,而读操作是对4 个存储体同时进行。

2) 缓存模块。该模块由4 个相同的1024 ×8 bit的存储体构成,每个存储体由FPGA 内部的2 个BLOCKRAM构成,每个存储体都是双口的SRAM ,把其中一个端口定义为只写,另一个端口定义为只读。每个存储体的每个端口靠缓存控制模块发来的读写使能信号来进行相应操作。对这4 个存储体进行编号,依次为1、2、3、4 号存储体,其中的1、3 号存储体在这里称为奇行,2、4 号存储体在这里称为偶行。

3) 插值模块。此模块由2 个子模块构成,插值控制模块和插值运算模块。

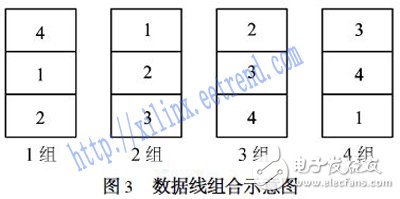

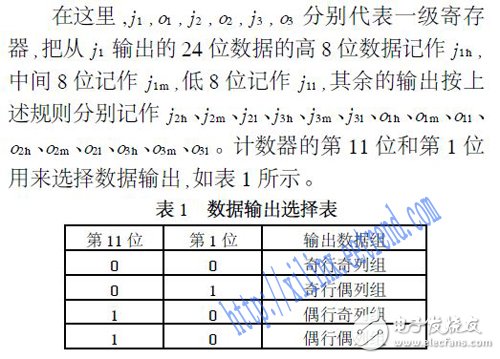

插值控制模块先对存储体输入的数据线进行组合,并对组合后的数据线编号,如图3 所示,图3 中方框内的数字分别代表各个存储体输出的数据线,经过这样组合后,就得到24 位宽的数据线,并且数据线的高低位也是如图示的顺序,以1 组为例,存储体4 的数据线的最高位是组合后的最高位,存储体2 的数据线的最低位是组合后的最低位。在这里,把1 、3 组称为奇行组,2 、4 组称为偶行组。

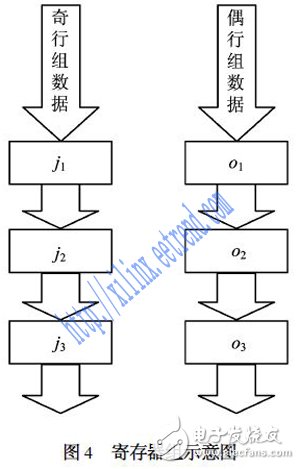

插值控制模块内部有一个12 位的计数器,最高位控制进入插值模块的数据是1 、2 组还是3 、4 组,奇偶行组的数据分别进入各自的3 级寄存器组,如图4 所示。

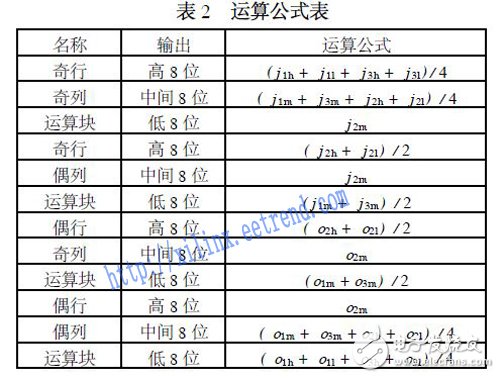

插值运算模块由4 个运算块构成,分别是奇行奇列运算块、奇行偶列运算块、偶行奇列运算块、偶行偶列运算块。在设计的过程中,插值处理是以图1 所示的Bayer 模板为标准进行,奇行奇列运算块要处理的就是补充绿色和红色,奇行偶列运算块要处理的就是补充蓝色和红色。各运算块的输出数据按高8 位是红色,中间8 位是绿色,低8 位是蓝色进行排列。

各运算块的运算公式如表2 所示。

3 仿真结果

整个设计是在XIL INX(赛灵思) 公司ISE 6. 1i开发环境下完成的,完成用V HDL 编写逻辑代码的工作之后,接下来是对逻辑代码的仿真验证,使用的仿真工具是Modelsim XE Ⅱ5. 7C ,此仿真工具是所使用的开发环境是配套的。

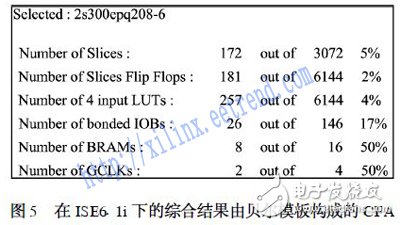

4 实现

在完成上述工作之后,剩下的就是在FPGA 上实现, 本课题选用的FPGA 是XILINX 公司的XC2S300E262PQ208C。此FPGA 有30 万个系统门,1536 个CLB ,16 ×4 kbit 的块RAM ,146 个可用I/ O 口,4 个DLL ,其内核运行电压是1. 8 V 。

综合结果如图5 所示, 此设计是在基于XC2S300E262PQ208C 的FPGA 开发平台上验证的,此平台是自主设计的,并且已经在这个平台上实现了实时高清晰度双SDRAM 显示控制器,此IP 核是完全拥有自主知识产权的。在验证时是将CFA

插值模块作为显示控制器的一个子模块进行的,用OmniVision 公司的OV9650[5 ] 提供输入,每个像素是8 位的XGA @15 Hz 的Bayer 模板数据,CFA 插值模块把接收到的数据进行处理,然后将彩色图像数据传给显示控制器,剩下的工作交给显示控制器进行处理,以后的处理在此不再详谈,有兴趣的读者可查阅文献[6 ] 。

5 结束语

笔者用FPGA 实现实时高分辨率Bayer 模板数据的双线性CFA 插值算法,是作为FPGA 实现算法的一种尝试,从实际效果看,是可行的;从实时性角度出发,算法用硬件实现是一个趋势,FPGA 的可编程特性使得其成为这方面的首选,相信以后会有更多的基于FPGA 实现算法的设计出现。

-

神经网络加速器的双线性插值上采样2025-10-29 207

-

基于FPGA的图像旋转和双线性插值算法设计2023-09-04 3530

-

双线性插值算法的讲解2022-09-19 4516

-

在FPGA上如何实现双线性插值的计算2019-08-09 5067

-

一种基于FPGA的实时视频图像处理算法研究与实现2019-06-28 3978

-

双线性轻量级Ad Hoc网络匿名路由协议2018-02-07 1310

-

基于双线性滤波器的自适应有源消声算法的研究_伍彩云2017-03-16 719

-

基于双线性插值的图像缩放在GPU上的实现2017-01-08 970

-

基于Matlab的双线性插值算法在图像旋转中的应用2016-05-04 779

-

求双线性插值法的C语言程序!帮帮忙!拜托各位了!2014-04-20 2869

-

一种改进的线性图像插值算法2012-08-20 1545

-

基于协方差矩阵的CFA插值盲检测方法2009-11-18 1456

-

双线性变换法设计数字Butterworth和Chebyshe2009-05-10 1400

-

基于双线性映射的非对称公钥叛逆者追踪2009-03-28 641

全部0条评论

快来发表一下你的评论吧 !