基于FPGA与DSP中实现的TS201的LinkPort口的协议设计

可编程逻辑

描述

随着科技的进步,对DSP 的处理速度以及相互之间的通信速度要求越来越高。ADI 的TS201 是目前业界性能最高的DSP 处理器之一,具有极强的数据处理能力和丰富的硬件资源, 其主频可高达600MHz ,总体性能可以达到3GFLOPS 或者12GOPS ,外部数据通信速度就成为发挥其性能的瓶颈。为了配合发挥其强大的处理能力,TS201 专门为高速通信设计了基于LVDS 技术的LinkPort 口。LVDS 是一种小振幅差分信号技术,使用非常小的幅度信号(350mV) 通过一对差分PCB 走线来传输数据,在两条平行的差分信号上流经的电流和电压幅度相反,噪声同时耦合到两条线上,于是噪声被抵消。LVDS差分信号技术降低了对噪声的关注。TS201 使用LinkPort 进行高速通信,解决了TS201 之间的通信瓶颈问题,但无法和需要高速通信的实时系统之间实现连接。FPGA 具有接口灵活,硬件设计软件化的功能,可以方便的实现各种数据接口和协议的对接。本文介绍了用FPGA 与DSP 的LinkPort 的对接原理和实际应用,在实时系统和TS201 之间搭起了一条高速通道。

1 LinkPort 介绍

TS201 上有4 个LinkPort 口,每个LinkPort 口有24 根线,包含收发两个模块,每个模块中包含了5对差分数据线和两个控制线,分别是LxDATO3 - 0P ,LxDATO3 - 0N , LxCLKOUTP , LxCLKOUTN , LxACKI ,LxBCMPO , LxDATI3 - 0P , LxDATI3 - 0N , LxCLKINP ,LxCLKINN , LxACKO , LxBCMPI。其中接收和发送数据的数据线以及时钟线都是使用LVDS ,这样有利于实现高速的数据传输,在应用中,DSP 之间的Link2 Port 传输数据可高达每对线500MHz。

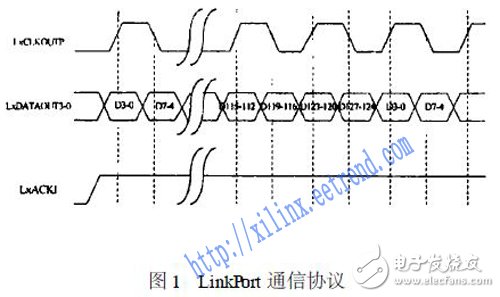

LinkPort 通信协议:LinkPort 口发送和接收数据的逻辑是很直接的,但是通过采用LVDS 技术,可以运行在很高的速度上。TS201 处理器所使用的Link2 Port 协议的一个简化说明如图1 所示。

数据帧的开始是由LinkPort 时钟的上升沿来指示的,在时钟的上升沿和下降沿分别传送数据,时钟结束,则数据传送也停止。所以LinkPort 口上的时钟是不连续的。TS201 的LinkPort 发送数据是以128bit 为基本单位的,所以一次发送数据至少需要16 个时钟周期来完成。

2 在FPGA 中实现LinkPort 口

Xilinx 的Virtex - II 系列的FPGA 是一款高性能,资源丰富的产品,它支持和TS201 DSP 之间的LinkPort 互联。由于LinkPort 口具有收发两个模块,所以在FPGA 中要实现和LinkPort 口的对接,需要在其内部实现收发两个模块来分别和DSP 的LinkPort 口相对应。

2. 1 FPGA 中的时钟以及DCM

要在FPGA 中实现LinkPort 口的收发功能,就必须要进行复杂的时序控制,Virtex 系列的FPGA 中提供了功能强大的DCM(数字时钟管理器) 模块,它可以实现延迟锁相环,数字频率合成器,数字移相器,数字扩频。在LinkPort 的实现中,至少要用到两个DCM,其中一个DCM 作为延迟锁相环,另一个作为移相器。利用这两个DCM 模块,可以给LinkPort 的实现提供同频率的,相位分别是0 度,90 度,180 度和270 度的时钟供LinkPort 口实现的时候使用。

FPGA中实现LinkPort 涉及到多个时钟: FPGA的外部输入时钟,FPGA 的LinkPort 口的发送时钟,FPGA 的LinkPort 口的接收时钟。对于这些不同的时钟采取了不同的处理方法。FPGA 的外部输入时钟是由外部的时钟输入管脚经过FPGA 的全局时钟缓冲IBUFG模块送到DSP 内部的DCM 模块供内部系统使用。FPGA 的LinkPort 口的接收时钟直接使用Xilinx 所提供的差分接收模块ibufds_lvds_25_dt 直接转换成内部的单端时钟信号使用。使用这个时钟以及它的反向时钟来锁定LinkPort 口上的上升沿数据和下降沿数据。LinkPort 口的发送时钟则是由Xilinx 的FDDRRSE 模块来实现的。

2. 2 LinkPort 接收模块的设计

接收模块首先调用FPGA 内部的差分信号转单端的模块ibufds_lvds_25_dt ,把外部传输线上的LinkPort 口差分信号转换成内部的处理信号。由于LinkPort 口在LinkPort 时钟的上升沿和下降沿分别传送4 位的数据, 同时一次LinkPort 传送最少是

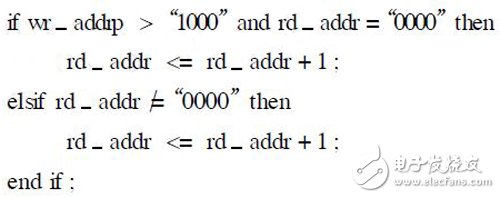

128bit 的数据,也就是一次LinkPort 传送至少需要16个LinkPort 的时钟周期。因此需要将接收的数据进行拼装组合并保存。为了实现这个功能,利用双端口RAM采用了两级缓冲的机制,先用8 个16 位深度的1bit 小的数据缓冲模块RAM16X1D 将数据从LinkPort 口接收下来,然后以8bit 为单位写到FPGA内部内建的一个较大的非对称双口RAM 模RAM16_S9_S18 中。这个小的数据缓冲区利用一个状态机控制它的地址变化,形成一个循环的数据缓冲区。使用以下语句实现了一个类似乒乓缓冲的小的数据缓冲区:

数据接收的时候,开始接收的数据超过8 个的时候,就开始从RAM16X1D 的这个小的数据缓冲区中读取数据。当接收的数据收全之后,wr_addrp =“0000”,接收停止,而rd addr 此时处于高的缓冲区,这个时候程序会自动的读取剩下的8 组数据,将其送到大的数据缓冲区RAM16_S9_S18 ,保证接收的数据全部正确地放到内部的RAM 中去,此时rdaddr 也为“0000”,接收模块停止工作。

发送模块的关键是如何控制时钟和数据的发生以及保证他们之间的相位关系,使得在时钟的上升沿和下降沿都可以进行数据传输,同时数据是稳定的。实现这个功能的关键是使用了FPGA 内部的带有两个相位相差180 度的独立时钟的双数据速率的D 触发器(FDDRRSE) 。保证数据的稳定性是靠前面所提到的DCM模块所提供的不同相位的时钟信号,LinkPort 模块发送时钟使用90 度和270 度相位的时钟,要发送的数据使用的是0 度和180 度的时钟。LinkPort 发送模块的数据和相位之间90 度的相差可以保证LinkPort 的时钟发送时的数据是稳定的。

FDDRRSE 模块有一个复位输入R ,一个置位输入S ,一个时钟使能输入CE ,两组数据和时钟对D0与C0 和D1 与C1 ,一个数据输出Q。复位输入R ,当它为高的时候,重载所有的输入,并在时钟(C0 或者C1) 从低到高的过程中,将Q 的输出置为低(复位的优先级比置位的优先级要高) 。当S 的输入是高而R 的输入是低的时候,触发器被置位,在时钟(C0 或者C1) 从低到高的时候输出高电平。当R 和S 为低,CE 为高,C0 时钟从低到高的时候D0 上的数据加载到D 触发器中。当R 和S 为低,CE 为高,C1 时钟从低到高的时候D1 上的数据加载到D 触发器中。调用FDDRRSE 产生LinkPort 口的发送时钟时,

R和S 为低, CE 为高,D0 为时钟产生控制信号CLOCKOE ,D1 为低,C0 为90 度相位的时钟txclk90 ,C1 为270 度相位的时钟txclk90not 。正常工作的时候,在txclk90 的上升沿将D0 的clockoe 的信号输出到lxclkout ,在txclk90not 的上升沿将D1 的低电平输出到lxclkout 。这样当clockoe 为低的时候, lxclkout就一直为低,需要传输数据的时候,将clockce 设置为高- 这样就可以根据需要产生非连续的LinkPort时钟。

当双口RAM 中存在要发送的数据的时候,LinkPort 的发送模块先从双端口RAM 中取一个16位的数据,通过内部的时钟控制和时序调整,将这个16 位的数据串行化成LinkPort 上传输的4 位一组的数据,这些数据分批以txclk ,txclk180 的时钟发送到LinkPort 口,同时以txclk90 ,txclk90not 的时钟产生相应的LinkPort 时钟。在FPGA 的输出到管脚之前,调用FPGA 内部的obufds_lvds_25 模块将内部的单端信号转换成差分信号。

3 工程应用及性能指标

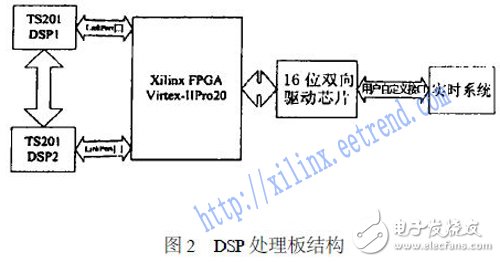

采用LinkPort 通讯的技术在DSP 处理板上已经得到了应用,该板的结构如图2 所示。

在这个实时处理系统中,利用FPGA 提供的高速LinkPort 数据接口,实现了雷达测速系统和DSP处理器之间的无缝连接,很好地满足了应用的要求。

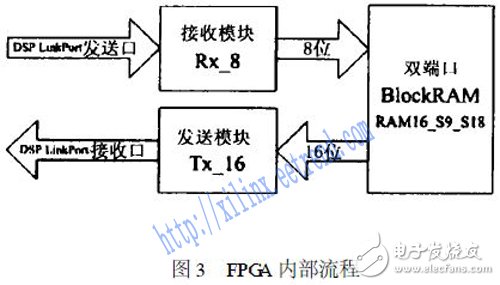

要求该板上的FPGA 和DSP 之间的LinkPort 口上的时钟能够达到200MHz。板上的时钟同时提供给TS201 芯片和FPGA ,使用一个DSP 的LinkPort 口和FPGA 进行测试,由于FPGA 内部的LinkPort 接收数据是以8 位为单位进行处理,发送数据是以16 位为一组进行处理的,把LinkPort 口的接收模块称为rx_8 模块,发送模块称为tx_16 模块。FPGA 内部的数据流程如图3 所示。

经过实际验证, 在LinkPort 口上的时钟达到300MHz 及300MHz 以下的频率时可以可靠收发数据。而LinkPort 口每个时钟可以传送1Byte 数据,也就是说FPGA 和TS201 之间的LinkPort 的通信速度已经达到双向2. 4GbitPs。对于目前的应用来说已经足够了。

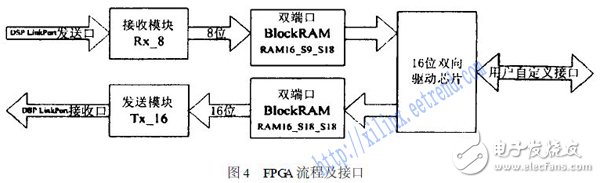

FPGA 中的接收模块和发送模块是可以分别使用的,通过和FPGA 内部不同模块进行组合以及时序控制就可以应用到实际系统中,在西部某雷达测速系统中已经将方案进行了实际应用,实际应用中FPGA 的内部框架及接口如图4 所示。

4 结束语

本文介绍了TS201 的LinkPort 口的协议以及在Xilinx V2Pro20 FPGA 中实现该协议的原理, 并给出了该方案的具体指标和典型应用。因为FPGA 具有很强的灵活性,可以很方便地实现各种数据接口格式和协议的对接,根据实际系统的需要实现FPGA 与系统的对接,就可以利用FPGA 和DSP 之间的LinkPort 高速通道,实现DSP 和系统之间数据交换的无缝连接。

-

如何利用FPGA与ADSP TS201去设计总线接口?2021-04-28 1313

-

如何利用FPGA与ADSP TS201设计总线接口?2019-08-09 2437

-

FPGA和DSP高速通信接口设计方案2019-06-21 2221

-

采用USB协议实现DSP高速上位机接口设计2019-05-31 1956

-

ADSP-TS201的外部接口技术和连接实例2019-04-12 1761

-

FPGA与DSP的高速通信接口设计与实现2018-12-04 2649

-

ADI TS201的RS422串口通信和与SDRAM读写的程序交流2018-10-30 1785

-

请教关于TS201的EPROM启动模式问题2018-08-01 2243

-

利用FPGA 实现与TS201 的LinkPort 高速数据2010-09-22 975

-

基于TS201的高速数据记录仪的设计与实现2010-07-15 819

-

基于TS201 EZ-KIT板的软件开发及应用2010-01-07 841

-

FPGA与ADSP TS201的总线接口设计2009-12-11 2774

全部0条评论

快来发表一下你的评论吧 !