以功能建模为基础的含FPGA电路板测试方法研究过程详解

可编程逻辑

描述

1 引言

FPGA 具有高速度、高集成度,可重复编程的特点,将其用于电路系统设计,可简化电路设计,增强电路功能。而作为电路系统的“中枢控制神经”,FPGA 的故障会引起整个电路系统的瘫痪,而用一般的测试方法很难对其实施故障测试诊断。

目前,某修理单位的自动测试设备对不含上述复杂逻辑器件电路板的测试诊断已有解决措施。但这些自动测试设备尚不能对含复杂逻辑器件电路板进行有效地测试,现有的自动测试设备未包含DSP和FPGA、CPLD 等仿真系统,不能对复杂逻辑器件的工作状态进行有效控制。

因此,含FPGA 电路板测试及故障诊断方法的研究,将显著提高电子装备的可维修性,使复杂逻辑器件给电子装备水平带来的提高能得到最大限度的发挥。

2 基于边界扫描的含FPGA电路板测试

系统级测试一般采用BIT( 内嵌测试) ,即在系统运行过程中,由内嵌测试程序实时监控系统的运行状态。一旦有故障发生,内嵌测试程序报告是哪个部件出错,就可拔出该部件进行修理。对现场级维修而言,含FPGA 器件电路板的故障检测要求快速准确,方法简单实用,能在最短时间内自动将故障定位到现场可更换单元( LRU) ,多采用边界扫描测试( BST,Boundary Scan Test) 方法。

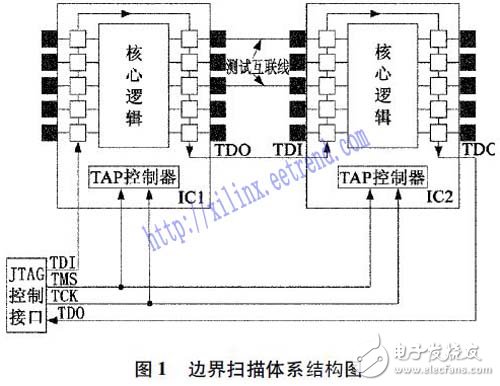

边界扫描是一种可测试的结构技术,用来解决测试探针所不能实现的测试问题。它是在芯片的I /O 端上增加移位寄存器,把这些寄存器连接起来,加上时钟复位、测试方式选择以及扫描输入和输出端口,而形成边界扫描通道。由于边界扫描测试可直接获得芯片管脚的信息,所以完全可以实现芯片级、板极、系统级的测试。每个IEEE1149. 1 兼容的器件,都包括一个4 线或5 线的测试端口( TAP) 、一个状态机( TAP 控制器) 和由边界扫描单元构成的边界扫描移位寄存器。其接口和总线常被称为JTAG 接口和JTAG 总线,其结构如图1 所示。

3 非完全边界扫描FPGA 电路板测试

由于测试性设计水平的限制,由边界扫描器件和非边界扫描器件组成的非完全边界扫描电路板广泛存在,如何对该类电路进行故障检测与隔离是需要研究的关键问题。

3. 1 非完全边界扫描电路板簇测试

利用“虚拟数据通道法”,通过电路板上的BS器件实现非BS 器件的测试。其基本原理为: 首先将常规器件芯片聚类合并构成相应的逻辑功能簇“cluster”,其输入输出端口与若干BS 器件相连,按照一定的算法生成簇测试矢量。边界扫描测试开始时,簇测试矢量通过其输入端BS 器件加载,测试响应由输出端BS 器件捕获并通过边界扫描链移出,然后进行结果分析和处理。这种方法可以利用BS器件的虚拟通道对与其相连接的cluster 输入输出节点进行诊断,即通过虚拟输入和虚拟输出对逻辑功能簇进行诊断。对不与BS 器件相连的剩余输入输出端口,可以用其它方式加载测试矢量和捕获测试响应,进行实体输入与实体输出,即串行测试与并行测试相结合。

3. 2 基于BS 与数字I /O 测试向量的测试方法

在含有FPGA 器件的电路板中有部分电路,属于非边界扫描器件,位于电路板边缘连接器和FPGA器件形成的边界扫描链之间。这部分器件的功能测试难以进行,可以采用边界扫描测试技术与传统的外部输入矢量测试相结合的方法。

该方法能实现非边界扫描器件的测试,但由于数字I /O 模块输入的矢量信号必须等到边界扫描完成一个循环周期后,才能接着输入下一个向量,受边界扫描测试矩阵中并行测试向量数目的影响,测试耗时长,尤其是与外部I /O 之间的时序难于控制,是研究的重点和难点。

3. 3 扩展边界扫描测试

针对基于边界扫描技术的测试系统实现难度大、故障覆盖率低等问题,提出了MERGE 法边界扫描技术。将一个完整的数字电路分为非边界扫描芯片簇、边界扫描芯片簇和混合芯片簇。通过边界扫描扩展卡,构造UUT 的边界扫描结构,然后通过边界扫描技术进行测试[3]。

该方法无法在现有ATE上实现自动测试,需要构建新的测试系统。

4 基于功能建模的含FPGA电路板测试

以上方法无法完成整板功能的测试,本文通过含FPGA 电路板功能建模,结合LASAR( Logic Automatic Simulate and Response) 仿真软件,在某型ATE上实现含FPGA 电路板的自动测试。

4. 1 基于LASAR 的含FPGA 电路板测试方案

LASAR 作为数字电路测试开发和逻辑分析的仿真软件系统,已被全球众多国防电子与航空工程所采用,LASAR 的LSRTAP 数据格式已被IEEE制定为标准数字测试交换格式。LASAR 后处理软件可直接加载在ATE 设备上对被仿真电路板进行测试。目前,许多ATE 设备都提供了LASAR 后处理软件及其相关的技术文件。

对于以上平台,完成电路板上各元件的建模是LASAR 仿真及生成后处理文件的关键。在LASAR V6.60 中,VITAL( VHDL Initiative Towards ASIC Libraries)支持建立FPGA 和ASIC 结构模型。

基于VITAL 语言的含FPGA 电路板测试步骤如下:

( 1) 在FPGA 开发环境中,对FPGA 器件进行功能描述;

( 2) 编译FPGA 器件的功能描述文件,输出FPGA的配置文件和VITAL 标准格式数据,建立FPGA器件的软件模型;

( 3) 将VITAL 标准格式数据导入LASAR,建立FPGA 软件模型,实现FPGA 功能建模;

( 4) 把电路板的网表文件导入LASAR 仿真软件,将仿真的结果导出,经过后处理,应用到ATE上,对电路板进行测试诊断。

对于测试方而言,由于难以得到电路板设计资料,FPGA 功能建模是研究的难点。

4. 2 基于VITAL 语言的FPGA 功能建模

VITAL 是在IEEE std 1076 - 1993 基础上开发的,提供面向ASIC 设计的VHDL 模型基准语言,其目的是促进ASIC 模型库在工业VHDL 描述和模拟中的应用,它为ASIC 库的建立、电路设计的描述提供格式相对固定的描述方法,并为提高VHDL 模拟性能提供依据和基础。

VITAL 语言标准包括时序程序包VITAL_Timing、建立模型用的规范文档和基本元件包VITAL_Primitives,并引进Verilog SDF ( Standard Delay Format)延时机制。VITAL_Primitives 包括基本逻辑元件和实用元件两部分。基本逻辑元件模型执行基本逻辑操作,实现基本元件的功能,实用元件支持多驱动源决断操作和查表操作。时序程序包中定义了VITAL 基本类型,延时计算函数和过程,时序约束检查过程等。VITAL_Primitives 使用VITAL_Timing 程序包中定义的类型和函数。VITAL 中延时和时序约束都定义为VHDL 类属参数,并规定SDF 标准格式与VITAL 间对应关系,允许仿真程序直接读人SDF文件,覆盖类属参数的默认值[9]。

VITAL 模型方法能够将FPGA 器件开发软件的设计输出,转化为LASAR 仿真软件识别的器件模型,大大简化FPGA 器件的功能建模过程。

4. 3 基于LASAR 的含FPGA 电路板仿真

设计网表、SDF 文件和宏单元库是生成LASAR模型所需的重要数据。LASAR 中的VITAL 和Verilog转换器能分别将SDF 文件、VHDL 和Verilog 网表转换为LASAR 模型。

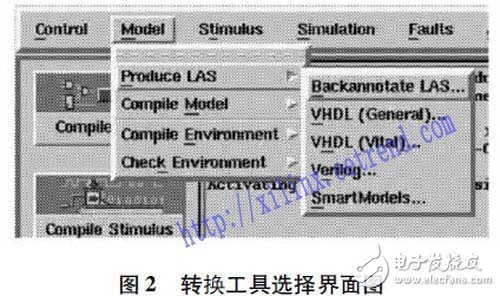

在LASAR 图形界面中“Model”工具栏下的“Produce LAS”中选择相应转换工具,如图2 所示。

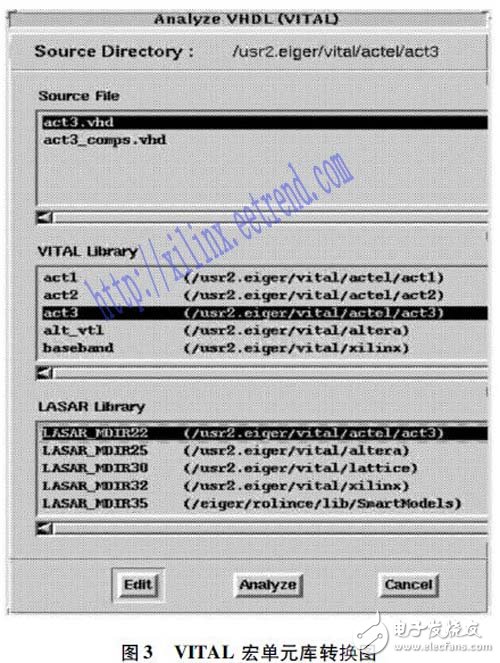

若为第一次使用该系列器件,需要将所有宏单元库转换并保存到所有LASAR 用户的库目录中。如图3 所示,选择VHDL 源文件,确定VITAL 库,然后确定结果保存路径。

器件转换过程分两步执行,首先将VHDL 设计网表转换为LASAR 结构模型,该过程和宏单元库转化过程类似,如图4 所示。选择VHDL 或Verilog 源文件、选择VITAL 库,然后确定目标路径( 通常为library.lib) 。

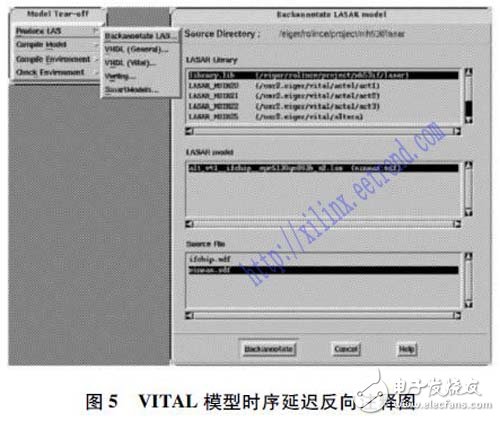

完成以上步骤后,需要将SDF 文件中包含的时序信息需要反向注释成转换设计文件。如图5 所示,通过选择“Produce LAS”下的“Backannotated”选项,确定设计文档和该设计的SDF 文件。LASAR 通过编译器件模型,并启动TIMCHG( 时间转换) 程序。TIMCHG 读取SDF 文件,并为器件节点分配时序属性。其结果是一个插入到本地library. lib 文件中的. BAV 文件( 反向注释模型) 。成功反向注释器件模型后,就可以进行整板模型编译和仿真。

并不是所有的设计100% 兼容VITAL,有一些VITAL 和Verilog 结构不能彻底转换。也可能有一些设计,违反基本的LASAR 限制。文献[5]介绍了这些约束和限制。

4. 4 基于LASAR 后处理的含FPGA 电路板测试

LASAR 后处理LSRTAP 生成的TAP 文件数据包括电路板功能测试、故障字典检测和探笔引导诊断三种可独立或混合的测试数据,该数据格式已被IEEE 制定为国际标准数字测试交换格式( DTIF -Digital Test Interchange Format) ,为基于数字仿真的TPS 的开发和交付提供了一种标准的信息内容和数据格式。

某型电路板自动测试系统完全支持LASAR 生成的后处理文件。首先应用LASAR 数字仿真软件按照上述提到的测试数据开发程序,生成电路板的测试数据,建立标准的“交换测试数据库”结构,然后将39个LSRTAP文件自动转换到对应的标准“交换测试数据库”中。ATE 直接调用数据库中的测试数据,进行测试和诊断。

5 结束语

由边界扫描和非边界扫描器件组成的非完全边界扫描电路板普遍存在,其故障检测与隔离是板级维修测试的难题。本文提出了一种基于功能建模的含FPGA 电路板测试方法。利用FPGA开发环境中生成VITAL 模型并导入LASAR,通过电路板的好板仿真和故障仿真,生成后处理文件,经ATE 调用完成含FPGA电路板的功能测试。该方法利用现有测试系统,实现了该类电路板的测试与故障诊断。

-

印制电路板自动功能测试介绍2014-02-28 0

-

印制电路板自动功能测试概述2018-09-14 0

-

电路板改板设计中的可测试性技术2010-01-23 497

-

电路板制板可测试性技术分析2010-07-10 1305

-

电路板功能测试解决方案2017-11-06 1297

-

针对含DSP电路板的测试方法与诊断分析2018-09-05 8886

-

电路板功能测试系统的测试对象及特点是什么2019-07-26 6180

-

印制电路板怎样实现自动功能测试2019-09-08 1911

-

如何对PCB电路板进行可测试性测试2020-03-27 2470

-

DSP电路板测试中的边界扫描技术研究综述2021-04-13 793

-

电路板振动测试的测试方法2024-02-01 2851

-

电路板测试方法有哪几种2024-05-28 2575

-

如何制作电路板测试架2024-05-28 1445

-

电路板测试步骤有哪些2024-05-28 2395

全部0条评论

快来发表一下你的评论吧 !