基于SRAM结构FPGA逻辑资源的测试编程

FPGA/ASIC技术

描述

1 引言

随着现场可编程门阵列( FPGA) 芯片在商业、军事、航空航天等领域越来越广泛的应用, 其可靠性和可测试性也显得尤为重要。对设计人员来说,FPGA 的使用相当灵活。然而, 正是这种应用的不确定性和重复可编程性, 增加了芯片测试的难度。目前, 已有较多工作集中于基于SRAM 结构的FPGA 测试方法研究[ 1-7] 。其核心问题是建立什么样的测试模型, 以及施加什么样的测试激励, 使故障激活, 同时, 还能在可及端测量出来。因此, 还要确定在什么地方施加激励, 在什么地方进行测量。

根据需求, FPGA 的测试大体可分为面向制造的测试过程( MT P) 和面向应用的测试过程( AT P)两类。MT P 主要是从制造商的角度来测试, 测试成本主要体现在测试向量集长度所决定的测试时间的费用上。MTP 主要针对可编程逻辑块( CLB) 、输入输出单元( IOB ) 、可编程连线( PI ) 及编程用的SRAM 等进行测试。AT P 是在应用级上的测试,也就是把FPGA 配置为特定的功能进行测试, 具有很强的针对性, 测试过程相对简单。但是, 不管是MTP 还是AT P, 都至少有一个{ 测试配置( TC) , 向量实施( TS) } 的过程[ 6] 。完整的测试通常需要反复进行配置和测试。一般来说, 编程比较费时且编程后的配置速度较低。因此, FPGA 测试的关键在于如何在保证故障覆盖率的前提下, 用最少的编程次数, 将FPGA 低速在线配置和高速测试有机地结合起来, 从而实现完整的测试。

本文介绍一种基于SRAM 结构FPGA 逻辑资源的测试编程方法, 并以Xilinx 公司的XC4000 系列[ 8] 为例, 在BC3192V50 数模混合集成电路测试系统上, 通过从串模式, 实现数据的配置和测试。

2 基于SRAM 结构的FPGA

从编程原理来说, FPGA 主要有基于反熔丝( arrtifuse) 结构和基于SRAM 结构两大类。XC4000 系列是基于SRAM 结构的, 其逻辑功能的配置基于内部阵列分布的SRAM 结构, 即通过对这些SRAM 进行不同的加电配置, 确定各个部分的逻辑功能; 也可通过加载不同的配置数据, 实现逻辑功能的不断更新和反复改写。实际上, 就是由加载于SRAM 上的配置数据决定和控制各个CLB、IOB 和PI 等的逻辑功能和相互之间的连接关系。基于SRAM 结构FPGA 的另一个重要特征, 在所谓的逻辑单元阵列( LCA) 结构。正是这个LCA 分布结构, 使之具备门阵列和可编程器件的双重特征。LCA 像一个门阵列, 通过内部可编程连线, 把可编程逻辑块按设计的要求连接起来, 实现阵列中的逻辑功能。

另外, 由于采用了先进的半导体工艺和改进的结构, XC4000E 系列能够支持高达80 MHz 的系统时钟频率和超过150MHz 的内部性能。

3 测试编程

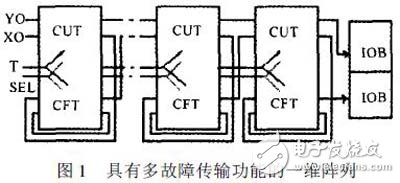

通过编程, 将每一行的CLB 连接起来, 形成一个一维阵列[ 1-2] ; 再将每个阵列作为整体进行测试,如图1 所示。

故障模型采用多CLB 混合故障模型, 即一个FPGA 中可有多个逻辑单元发生故障, 而逻辑单元内的故障对不同的电路采用不同的故障模型。对于查找表结构, 假定其可有固定为"0"或"1"的固定故障; 而对于多路选择器和触发器, 则假定可发生各种功能故障[ 4-5] 。

每个阵列中的CLB 都按图1 所示的连接方式进行编程, 前一个CLB 的输出信号作为后一个CLB 的输入信号, 只有左右两端的CLB 与IOB 相连。所有CLB 都设计编程为相同的电路结构, 既是被测电路( CUT) , 也是故障传递电路( CFT) 。CLB 中的两个查找表G 和F, 均设计为具有一个故障激活端( T) 、两个故障传递端( Yn 和Xn) 和一个故障传递方式选择端

( SEL) 的四输入逻辑结构, 且使用相同的T 输入和SEL 输入。查找表F 的两个输入端( Yn 和Xn) 与此CLB 内两个触发器的输出端( QYn 和QXn) 相连, 用于检测和传递触发器的故障信号。查找表G 和F 的两个输出信号( Yn 和Xn) 作为下一个CLB 中查找表G 的输入信号( Yn+ 1 和Xn+ 1) 。

故障传递电路采用基于与门和或门的电路形式[ 4 ] 。用SEL 输入控制是或门传输还是与门传输。此时, 如果有一个或多个CLB 的输入输出端有正常为1( 0) 、错误为0( 1) 的故障信息, 其输出端总能观察到故障信息0( 1) 。

对所有阵列并行地进行测试, 可以减少测试时间和所需要的IOB。同时, 因为所有CLB 都是同样的编程结构, 因此, 可共用时钟和垂直输入, 不同阵列的输入也可共用, 从而进一步减少了所需的IOB[ 1-2] 。

但是, 由于编程后的阵列是一个时序阵列, 故一定程度上增加了测试此阵列所需要的时间。另一方面, 由于每个CLB 在被测试的同时, 还要用来传递故障信息, 因此, 测试精度相对单独用一行CLB 来传递故障信息的方法[ 3-5] 有所降低。

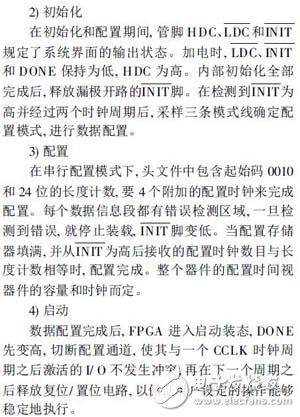

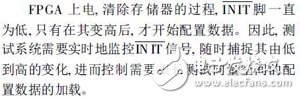

4 FPGA 的配置

通常, 将配置数据存放于FPGA 外附的PROM或EPROM 中, 在系统加电或需要时, 自动载入SRAM 中; 亦可直接由微处理器控制, 载入数据, 且只要一直保持在加电状态, 配置数据就不会丢失。FPGA 的在线配置, 就是把测试系统用作一个处理器, 再通过数字通道, 将配置数据装载到LCA 器件, 从而确定其内部各部分功能和连线方式的过程。

4. 1 配置模式

XC4000 系列FPGA 根据配置模式管脚( M0、M1、M2) 的不同输入, 产生三种是自装载的主模式:主串模式( 000) 、主并向上模式( 100) 和主并向下模式( 110) ; 两种外设模式: 同步外设模式( 011) 和异步外设模式( 101) ; 一种采用菊花链器件的串行从模式: 从串模式( 111) ; 以及一种附加的允许高速并行配置高容量XC4000EX 器件的从模式: 特快模式( 010) 。

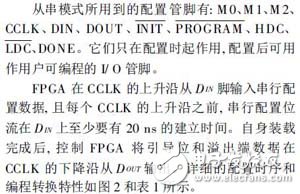

本文采用从串模式, 通过( 111) 模式管脚或缺省模式来选择。此模式为系统加载FPGA 配置程序提供了最简单的接口。串行数据DIN 和时钟CCLK 可同时由一个微处理器的I/ O 口从外部提供。

4. 2 配置数据的格式

从串模式的配置数据以一个40 位的头文件开始, 接着是一些实际的配置数据信息段, 每个信息段以一个0 起始、4 个错误校验位结束, 长度和数目取决于器件的类型。在配置结束时, 提供启动序列的4 个时钟, 要求附加启动的字节数据。具体来说,XC4006E 的配置文件长度为119, 840 位, 实际写入119, 792 位。

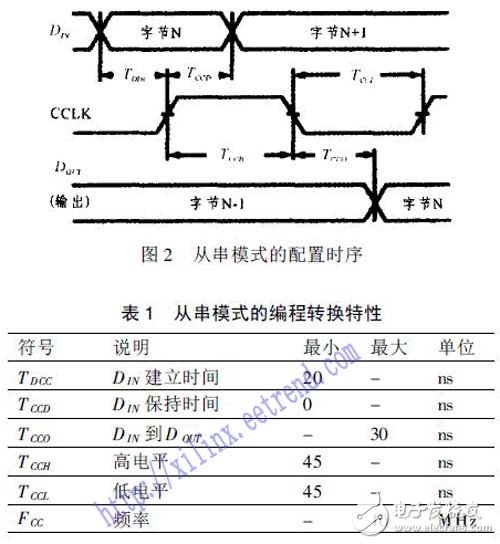

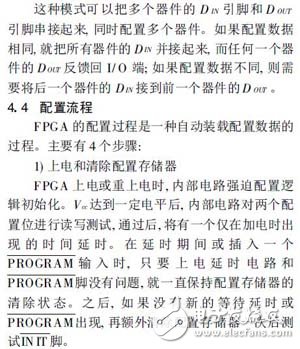

4. 3 配置管脚和时序分析

5 系统的资源分配和测试实现

下面介绍如何用BC3192V50 测试系统实现FPGA 配置数据的加载和测试。该系统是由北京自动测试技术研究所开发研制的VXI 总线型数模混合集成电路测试系统。

5. 1 配置和测试资源

FPGA 的每个配置和测试过程, 需要两个不同的测试程序{ TC, T S} 分别来完成。它们并存于系统内存里, 可随时激活, 但所需要的时钟频率和存储空间不同。

首先, 通过TC程序加载配置数据, 其速度比较低。配置后, 在持续供电的条件下, 通过TS 程序进行高速的功能测试和参数测试。

其次, 配置和测试过程使用的数字通道资源不同, 同一管脚在两个过程的通道定义也有所不同。配置程序只用与配置相关的管脚; 测试程序要根据设计的逻辑功能确定管脚, 且不可以超过芯片的全部用户可编程IOB 数。例如, 对于具体的芯片

XC4006E-4PC84C 来说, 其最大用户可编程IOB 为61 个, 文中的编程方法使用了8 个输入激励数字通道和32 个输出响应通道。

BC3192V50 测试系统最多可配置为8 块通道板256 路高速数字测试通道, 最大测试速率为50MHz( 非复用) , 可选定配置后芯片电源控制方式( 掉电/ 不掉电) 。通过这种模块化结构的系统设计,就可以实现配置和测试过程的多速率、多通道和持续上电等要求。

5. 2 配置程序自动生成

根据设计的逻辑电路结构、CLB 之间连线方式和测试向量等, 用Xilinx 公司ISE 集成综合环境,对FPGA 进行Verilog 设计输入和编译, 生成所需要的位流文件。但由于该文件比较长, 按字节配置需要几十万甚至几百万条向量, 且内容随编程信息的变化而变化。因此, 手工编制向量就显得很不切实际。必须采用自动生成的方法, 实现配置数据的加载。为此, 专门开发了一个测试程序生成软件, 用于将生成的位流文件转化成系统可以识别的文本文件, 通过调用该文件, 实现数据的加载。

5. 3 配置数据加载

BC3192V50 测试系统采用了循环、跳转、子程序调用和嵌套等指令, 数字通道具有归零、归一等激励格式, 且分别有激励、响应和记录存储区, 便于跟踪、调试测试程序, 测试向量深度为256 k( 标准) / 1M( 扩展) / 4 M( 最大) , 内存中最多可以加载256 个测试程序, 等等。通过这些功能, 可以有效控制配置数据顺利快速的加载。

5. 4 功能和参数测试

完成配置后的FPGA 就变成一个具有某种特定功能的器件, 可作为普通逻辑器件进行测试。所不同的是, FPGA 的I/ O 管脚非常多, 且可分别配置为TT L 或CMOS 兼容两种类型。它们的直流参数能直接反映出FPGA 的性能。在功能测试通过后, 必须用精密测量单元( PMU ) , 对所有I/ O 管脚进行参数测试, 才比较完整。但参数测试往往比较费时。

BC3192V50 提供每16 管脚一个PMU 的并行进行参数测试能力, 通过采用这种多PMU 并行测试子系统, 非常有效地节省了测试时间。

综上所述, 在测试系统BC3192V50 上测试FPGA, 实质上就是通过测试系统, 将FPGA 配置成所设计的逻辑结构, 然后施加测试向量, 完成配置后的功能和参数测试, 且根据需要, 可多次重复这种{ T C, T S} 的过程。

6 结束语

本文在国产数模混合集成电路测试系统BC3192V50 上, 实现了以XC4000 系列为例的基于SRAM 结构FPGA 可编程逻辑资源的测试。所阐述的测试系统的配置方法和实现过程具有很强的通用性。适用于支持串行配置, 并可通过{ T C, T S} 程序集, 完成测试过程的FPGA。但是, 当测试方法改变后, 所需要的测试程序集{ T C, T S} 的数量和内容也会改变。

-

如何利用Verilog HDL在FPGA上实现SRAM的读写测试2025-10-22 4563

-

可编程逻辑器件的结构2023-03-24 2133

-

FPGA 结构分析 -IO 资源2022-12-13 3433

-

基于SRAM的FPGA分类介绍2022-10-27 3333

-

基于BIST利用ORCA结构测试FPGA逻辑单元的方法2018-11-28 5201

-

基于测试系统的FPGA测试方法研究与实现2017-11-18 3424

-

可编程逻辑器件FPGA/CPLD结构与应用2016-12-11 917

-

FPGA的基本结构2016-07-16 3851

-

FPGA可重构设计的结构基础2011-05-27 3993

-

FPGA重复配置和测试的实现2010-01-26 724

全部0条评论

快来发表一下你的评论吧 !