多通道大容量的采集存储器的设计与实现

FPGA/ASIC技术

描述

数据采集存储是信号处理过程的一个重要环节, 已经广泛应用于雷达、声纳、瞬态信号测试、无线探伤等领域。在不同的条件下采样速率和采样精度也有所不同, 系统的实现方法也各有差异。通常情况下, 如果采集速率较低, 采集和数据计算机读取可同时进行。但在高速采集或采集源移动的情况下, 如空中飞行体或水下运动体, 这时就需要系统有采集功能的同时应具有存储功能, 存储数据可事后读取, 黑匣子就属于这样的采集存储器。根据目前的发展趋势, 开发体积小、功耗低和存储容量大的系统越来越受到重视。根据实际情况, 我们研制开发了一种用蓄电池就可工作的、能在水下应用的、可回收的小体积低功耗的大容量存储器。

本文就介绍了一种基于FPGA 和FLASH 的多通道大容量的采集存储器的设计与实现方法。

1 系统背景及功能描述

当船舶或潜艇在水中运动时, 要对其运动时的变化参数信号进行瞬态采集记录, 记录存储器要安装于运动的船体或艇体上的。要求采集存储时间不长, 但它必须要满足体积小、功耗低和可重复擦写功能。

此系统要求能对32 路模拟信号同时采集存储, 采样率是每路10KHZ, 总采样数率320K, 事后可对存储数据计算机读取分析。根据此种要求我们设计实现了多路采集存储器, 此种存储其使用FPGA 和FLASH 存储器。满足体积小, 功耗低的要求。用干电池供电就可工作。

2 系统结构设计

整个系统以FPGA 为核心控制器来组织工作, 它控制着整个系统的读、写、擦除等操作。系统主要解决的问题是采集、存储和数据事后读取。

2.1 数据采集

由于要同时对多路信号进行采集, 我们采取了FPGA 对模拟开关进行均等时间推进以实现通道的转换。当转换到某一通道时, FPGA 同时要启动A/D 进行模数转换。为了达到高精度采集的目的, 可采用12 位的AD 转换器。为了达到通道转换、启动A/D 和数据FIFO 存储的时序合理统一, 我们采用全体时钟, 实现过程如下图所示。

2.2 数据存储

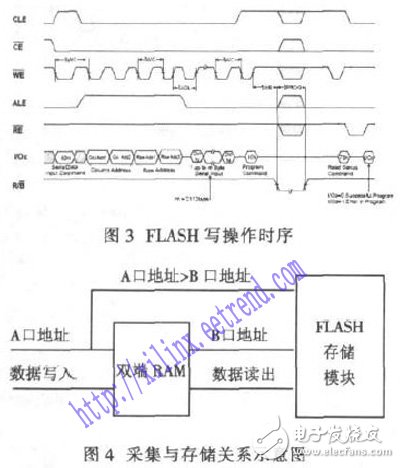

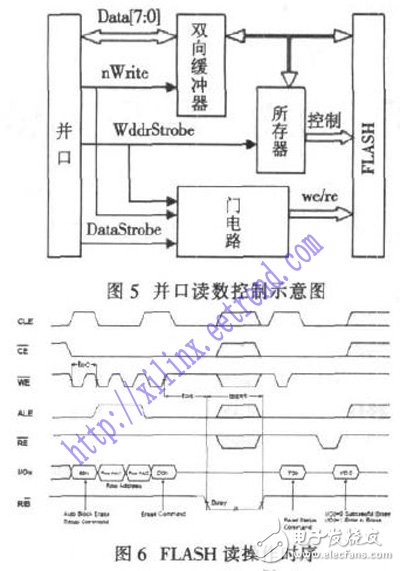

对数据的存储, 我们采用闪存(FLASH Memory)作为存储器, 它具有体积小、功耗低和数据不易丢失的特点。对FLASH的写操作过程有其固定的操作模式, 如图3 所示。由于FLASH是按页存储的, 当一页写完之后要进行下一页的控制字和地址的重新写入, 为了使采集回来的数据能及时准确的写入FLASH, 而不至于在页与页的交替时间内使数据丢失, 所以不可能将采集回的数据直接存入FLASH, 我们利用FPGA 内部提供的RAM来构成双端口RAM作为数据存储过程中的缓存, 采集回来的数据先写入双端口RAM, 然后再导入FLASH。过程是采回数据从A 口写入双端口RAM。双端口RAM中的数据从B口读出, 然后写入FLASH, 在操作的过程中, 要保证双端口RAM的B 口地址推进要小于其A 口的地址推进。因为在采集过程中使用了12 的位的AD, 加之FLASH 存储器是8 位的存储器, 所以就使得每次采集的数据要分2 次存储, 我们采取的方式是高8 位存储一次, 低4 位加补标志码的存储一次。

2.3 数据读取

数据的读取有很多种方法, 目前有串口、并口、USB 口或PCI 总线方式读取。我们这里采用并口读取方式。因为数据存储量大, 我们采取了并口主动读取的方法, 消除了并口从动读取速度慢的问题, 采用EPP 模式, 读取数据速度能达到500K—2Mb/s 的数据量。FPGA 此时的工作是使读数和采集的控制线与数据线的隔离。

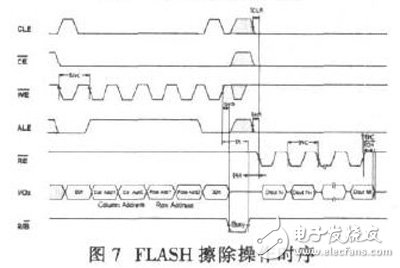

这时并口可直接对FLASH 的控制线和数据线进行操作。对FLASH 的读数操作也有其固定的操作过程。FLASH 数据的擦除是按块擦除的, 所以它的特点是擦除速度快, 一般在几秒钟内就完成了。当一次采集存储完毕后, 数据就长久保持在FLASH 内, 不会丢失, 若要从新采集存储, 则必须要先进行FLASH 擦除。

3 相关问题

3.1 防止数据错位的解决办法

在存储的过程中, 多路信号是同时存储在FLASH 里面的。当采集存储完毕后, 我们要对数据进行事后处理, 为了防止读取或存储数据错位现象, 也是为了便于对错误的跟踪查找, 最后使每路数据能完整的整合到一起。我们采取了相应的措施,在每个数据存储的过程中我们要给每路信号加上标志位, 当多路信号采完一个周期后, 存储一些标志位作为每帧数据的区分

信号。这样即使某帧数据出了问题, 也可以很容易的确定各路信号的数据, 不会出现数据错位现象。

3.2 开关量输入信号闭合时信号抖动的解决

在电路中, 对FPGA 有大量的开关行性操作, 例如控制读、写和擦除的控制信号, 还有FLASH 反馈给FPGA 的高频脉冲状态信号。在开关闭合的过程中, 信号存在抖动现象, 这时的信号是不稳定的, 为了消除这种信号的不稳定性外界因素干扰的不良影响下, 从而防止FPGA 的误操作现象的发生, 我们在FPGA内加了延时子程序, 目的就是对这些敏感信号进行消陡延时预处理, 避免误操作, 使系统在更加可靠稳定的状态下工作。

3.3 灌封技术

因为采集存储器要在水下工作, 所以要对其进行防水处理。经过多次灌封试验, 采用石蜡和三防漆灌封取得了良好的效果。

4 结论

根据本文介绍的采集存储器应用于某系统测试中, 经实验室和水下测试, 系统工作正常, 达到了设计的要求。

文章创新点:本文设计的采集存储器适用于水下作业, 采集可根据实际情况进行扩展, 采集频率可根据实际情况改动, 通用性比较强。它体积小、功耗低的优势更是目前采集存储的发展趋势。他的原理可得到广泛推广。

参考文献:

[1]沈兰荪. 高速数据采集系统的原理与应用. 北京: 人民邮电出版社, 1995.

[2]周明德. 微型计算机硬件软件及其应用. 北京: 清华大学.出版社, 1990.

[3]郭四稳,古乐野. 多通道大容量高速数据采集系统[J ] .四川大学学报,2001 ,38(1) :29~32.

[4]褚振勇, 翁木云. FPGA 设计及应用[M] . 西安: 西安电子科技大学出版社, 2002.

[5]缪云青李永刚. FPGA 器件在嵌入式系统中的配置方式的探讨[J]微计算机信息,2006,161~163.

-

多通道脉冲信号如何快速采集和存储?2023-11-10 1575

-

多通道振弦传感器无线采集仪存储数据如此导出2023-05-06 898

-

磁盘存储器的存储容量怎么算2022-01-29 14408

-

多通道信号采集记录 多通道采集存储 多通道记录存储介绍2021-08-11 1250

-

8051单片机内部程序存储器容量2021-07-19 1842

-

如何使用XCR3032实现大容量FLASH存储器的接口设计?2021-04-29 1658

-

labview多通道数据采集与存储2020-11-10 38323

-

基于FPGA的多通道图像采集存储系统设计2016-08-30 603

-

请问怎么实现多通道连续采集数据的定时存储。2014-08-01 2781

-

存储器容量的理解2012-11-30 3191

-

基于FPGA的多通道同步数据采集存储系统2010-12-27 1136

-

大容量固态存储设备的FPGA实现2010-12-08 643

-

NAS网络存储器的最大存储容量2010-01-09 2602

-

相变存储器:能实现全新存储器使用模型的新型存储器2009-12-31 1334

全部0条评论

快来发表一下你的评论吧 !