字位扩展存储器示意图解析

存储技术

描述

存储器的寻址

1. 线选法

简单微机系统存储容量不大,存储器芯片数也不多,可用单根地址线作为片选信号,每个存储芯片或每个I/O端口只用一根地址线选通。

2. 全译码片选法

将低位地址总线直接连至各芯片的地址线,余下高位地址总线全部参加译码,译码输出作为各芯片片选信号。

3. 局部译码片选法

只对部分高位地址总线译码产生片选信号,剩余高位线或空或直接用做其他芯片片选信号。是介于全译码片选法和线选法间的寻址方法

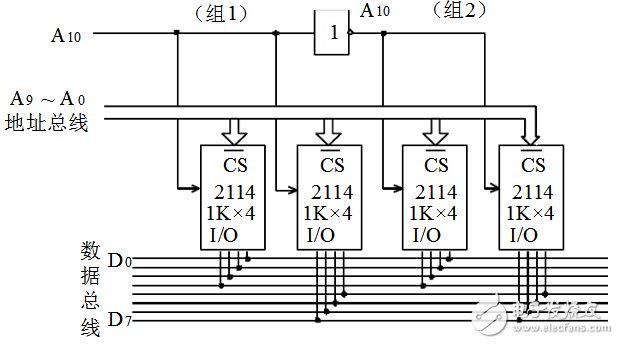

芯片单元数和位数都不能满足存储器的要求,要在字、位两个方向上扩展。如采用2114(1K×4位)组成2K×8位RAM,字、位都不能满足存储器要求,要进行字位同时扩展,如图所示。

位扩展(数据空间扩展)

例1:假定使用8K×1位的RAM存储器芯片,那么如何组成8K×8位的存储器?

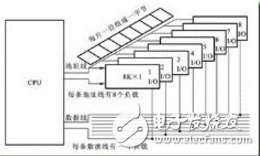

解:可采用图3-5所示的位扩展法。也就是用8片1Mb的存储芯片拼接而成。

存储器的字数与存储器芯片字数一致,所以不需加大字长。图中,每一片RAM是8K×1,故其地址线为13条(A0-A12),可满足整个存储体容量的要求。每一片对应于数据的1位(只有1条数据线),故只需将它们分别接到数据总线上的相应位即可。在这种方式中,对片子没有选片要求,就是说片子按已被选中来考虑。如果片子有选片输入端(CS#),可将它们直接接地。在这种连接时,每一条地址总线接有8个负载,每一条数据线接有一个负载。

例2:用2114(1K×4位的SRAM)构成1K×16位的存储器,试画出该存储器的组成逻辑图。

解:(1)分析2114及存储器

2114:地址线为10位,数据线为4位(1K×4)

存储器:地址线为10位,数据线为16位(1K×16)

所以,要进行位扩展。

(2)所需2114芯片数目:

所以,用4片2114

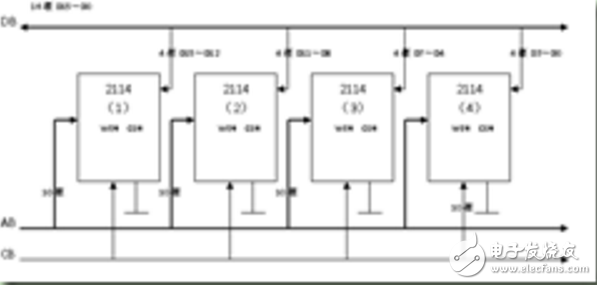

(3)2114组成逻辑图

四片2114地址线并联后与地址总线相连(即四片2114具有相同的1K地址);四片2114数据线拼接为16位后与数据总线相连。

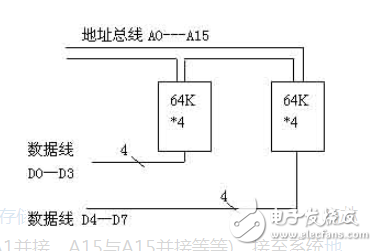

当使用的存储器芯片单元数目符合要求,但每单元的位数较少时,需要进行这种扩充。例如,使用4164(64K*1)扩充64KB存储系统,就需要进行位扩充。

连接示意图如下所示:

如图显示的是将两片64K*4芯片连接成64K*8的存储系统。采用位扩充,其连接要点是:两芯片的地址线分别并接在一起(即A0与A0并接,A1与A1并接,A15与A15并接等等),接至系统地址总线;两芯片的数据线各自提供数据总线的一部分(此例为高4位和低4位),共同组成8位的数据总线。

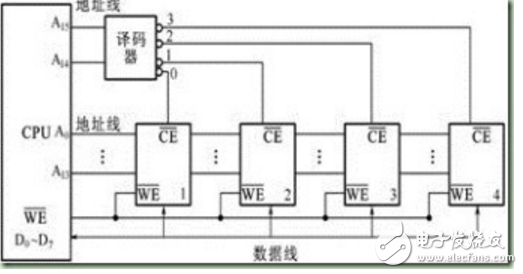

字扩展(地址空间扩展)

如果每片的字数不够,需用若干芯片组成总容量较大的存储器,称为字数扩展。为此将高地址译码产生的若干不同片选信号,按各芯片在存储空间分配中所占的编址范围,分送各芯片。低位地址线直接送往各芯片,以选择片内的某个单元。而各芯片的数据线,则按位并联于数据总线。

例1:图3-6示出用16K×8位的芯片采用字扩展法组成64K×8位的存储器连接图。

解:图中4个芯片的数据端与数据总线D0-D7相连,地址总线低位地址A0-A13与各芯片的14位地址端相连,而两位高位地址A14,A15经译码器和4个片选端相连。

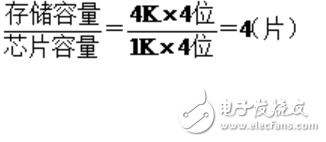

例2:用2114(1K×4位的SRAM)构成4K×4位的存储器,试画出该存储器的组成逻辑图。

解:(1)分析2114及存储器

2114:地址线为10位,数据线为4位(1K×4)

存储器:地址线为12位,数据线为4位(4K×4)

所以,要进行字扩展。

(2)所需2114芯片数目:

所以,用4片2114

002114(1K×4)

012114(1K×4)

102114(1K×4)

112114(1K×4)

(3)2114组成逻辑图(略)

存储器所需的12根地址总线分两部分:

低10根地址总线与每片2114的A0~A9直接相连,称片内地址线;高2根地址总线通过2/4译码器产生4个不同的片选信号,接各芯片的CS#端,称片选地址线。

4根数据总线直接与每片2114的I/O1~I/O3直接相连。

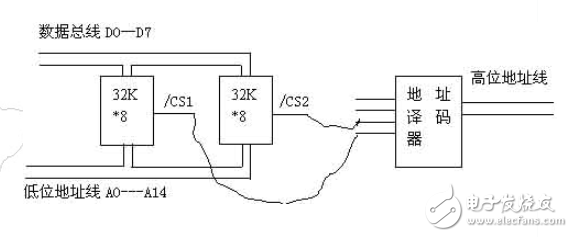

当使用的存储器芯片位数符合要求,但单元数目较少时,需要进行这种扩充。例如,使用6264(8K*8)扩充64KB存储系统,就需要进行字扩充。

连接示意图如下所示:

如图显示的是将两片32K*8芯片连接成64K*8的存储系统。采用字扩充,其连接要点是:两芯片的低位地址线分别并接在一起,接至系统地址总线的低位;两芯片的数据线分别并接在一起,接至系统数据总线;系统高位地址线,进行译码,译码的输出分别接至两芯片的片选端CS1,CS2。

字位同时扩展

在组织实际的主存储器时,可能既有字扩展又有位扩展。一个存储器的容量假定为M×N位,若使用l× k位的芯片(l《M, k《N),需要在字向和位向同时进行扩展。此时共需要(M/l)×(N/k)个存储器芯片。

例1:设CPU有16根地址线,8根数据线,并用/MREQ作访存控制信号,用/WR作读写控制信号(高为读,低为写)。现有下列芯片:1K*4位RAM,4K*8位RAM,8K*8位RAM,2K*8位ROM,4K*8位ROM,8K*8位ROM及74LS138译码器和各种门电路,要求:

① 主存空间分配: 6000H~67FFH为系统程序区; 6800H~6BFFH为用户程序区。

②合理选用上述存储芯片,说明各选几片?

③详细画出存储芯片的片选逻辑图。

解题过程板书

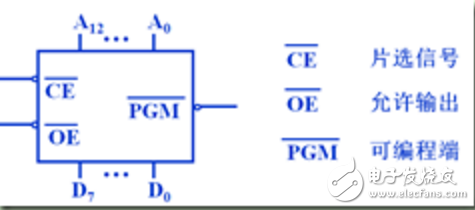

例2:设 CPU 有 20 根地址线,8 根数据线。并用 IO/M 作访存控制信号。RD 为读命令,WR 为写命令。现有 2764 EPROM ( 8K × 8位 ), 外特性如下:

用 138 译码器及其他门电路(门电路自定)画出 CPU和 2764 的连接图。要求地址为 F0000H~FFFFFH , 并

写出每片 2764 的地址范围。

解题过程板书

例3:设CPU的地址总线16根(A15~A0,A0为低位),双向数据总线8根(D7~D0),控制总线中与主存有关的信号有MREQ#(允许访存,低电平有效),R/W#(高电平为读命令,低电平为写命令)。

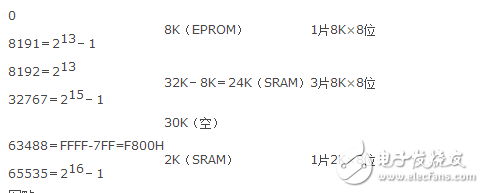

主存地址空间分配如下:0-8191(13个1)为系统程序区,由只读存储器组成;8192-32767(15个1)为用户程序区;最后(最大地址)2K地址空间为系统程序工作区。上述地址为十进制,按字节编址。现有如下存储器芯片:

EPROM:8K×8位

SRAM:16K×1位,2K×8位,4K×8位,8K×8位

请从上述芯片中选择适当的芯片设计该计算机的主存储器,画出主存储器逻辑框图,注意画出选片逻辑(可选用门电路及3-8译码器74LS138)与CPU的连接,说明选择哪些存储器芯片?选多少片?

解:解题过程板书

主存地址空间分布如下图所示。

图略。

扩展位需要增加位选,这个又有很多讲究,要看你现在的片上可用的外部存储地址有没有用完,总得来说可以用译码芯片和不用译码芯片,又分为完全译码和不完全译码,字位扩展就麻烦了 首先是你的芯片输出是多少位的,比如说3位的51的数据线有8位,如果你要多余8位可以用锁存器,如果是很简单的数据,可以自己用命令访问外部芯片,这样比较麻烦,但是可以不用译码器,但是要求对外部存储芯片的工作原理有了解

-

jf_05450020

2024-03-27

0 回复 举报真的讲得特别好特别清楚 我终于懂一些了 请问有没有完整版呀!!! 收起回复

jf_05450020

2024-03-27

0 回复 举报真的讲得特别好特别清楚 我终于懂一些了 请问有没有完整版呀!!! 收起回复

-

什么是存储器的位扩展和字扩展?2021-10-27 0

-

变频器直流母线电路示意图分析2022-10-27 1847

-

氯离子结构示意图和钠离子结构示意图2008-05-28 55615

-

电脑键盘示意图,计算机键盘示意图2009-03-10 127324

-

飞机示意图2009-05-26 2345

-

失会聚示意图2009-07-31 1097

-

顺序传输制示意图2009-07-31 901

-

混合动力汽车示意图2009-11-21 2093

-

5X35023 参考示意图2023-03-14 323

-

9ZX21901 参考示意图2023-03-21 329

-

9ZX21201 参考示意图2023-03-21 301

-

9FGV1006 参考示意图2023-05-19 423

-

9DBL0455 参考示意图2023-07-05 289

-

9FGV1004 参考示意图2023-07-07 290

-

变频器直流母线电路示意图讲解2023-08-10 2120

全部0条评论

快来发表一下你的评论吧 !