以FPGA为基础的脉冲量采集模块设计详解

可编程逻辑

描述

随着脉冲量的采集在传感器、雷达和遥测等系统中的应用越来越广泛.对脉冲信号采集过程中的幅值、频率和精度等参数的要求也不断提高⋯。面对这些问题.所遇到的挑战也越来越大。传统的脉冲信号采集设计是采用分立元件搭建的单稳态电路来实现.这种电路结构简单易于实现.但其输出信号的精度和稳定度低,易受环境因素影响。因此,有必要设计一种高精度、高稳定性的采集模块来适应技术发展的需求。

在硬件设计方案中主控芯片采用FPGA来完成所有的逻辑控制功能。这是因为FPGA具有以下特点:

1)易扩展。本系统功能模块较多,利用大封装FPGA并行输入输出管脚。很容易构成各种规模的应用系统。

2)控制功能强。硬件描述语言VHDL的描述能力和抽象能力很强。用它来描述集成电路的功能和结构.并经过不同级别的验证来形成不同级别的IP内核模块,具有很强的控制功能。

3)集成化程度高。系统将主要逻辑功能通过自下而上的设计方法集成在FPGA芯片内。然后在印制板上布局、布线构成系统模块,大大提高了系统的集成度,使总体设计达到了小型化的要求。为了提高高速采集过程的可靠性和适应市场发展微型化的要求.现提出了一种基于FPGA的脉冲+信号采集模块。

总体设计

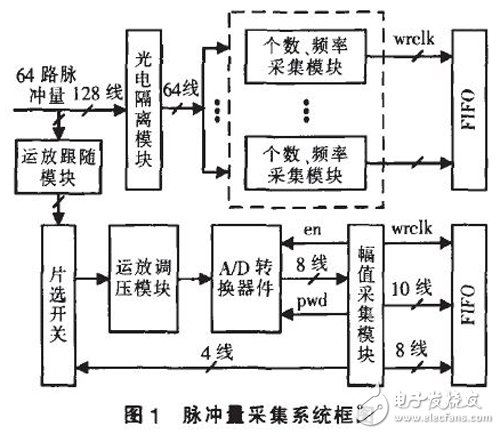

该模块的作用是模拟数字量变换器的接口电路并采集数字量板卡输出脉冲的个数、频率、及幅值.方便用户对数字量输出板卡脉冲量功能模块进行调试与检测.被测板卡采集模块程序包含64路采集进程,其主要功能有:

1)接收通用测试台数字量板卡发出的64路脉冲量信号.并采集脉冲量个数、脉冲幅值、脉冲频率等参数。

2)模拟数字量变换器向数字量板卡提供帧同步信号及移位脉冲信号.并采集数字量板卡发送的数据信息。

下面将详细介绍脉冲量采集模块的电路组成及程序设计思路.整体系统框图如图1所示。

2 脉冲量采集模块电路设计

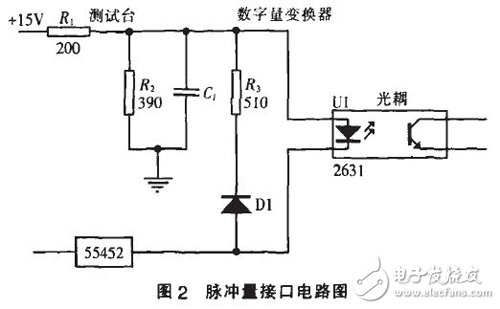

如图2所示的各脉冲量接口电路图可知,每路脉冲信号以正负2路信号输入被测板卡,后经过光电隔离器转换成单端脉冲信号。本模块的主要功能是采集脉冲信号的幅值、个数及频率.此模块的电路设计共分2个部分:采集脉冲信号幅值部分和采集脉冲频率及个数的部分。

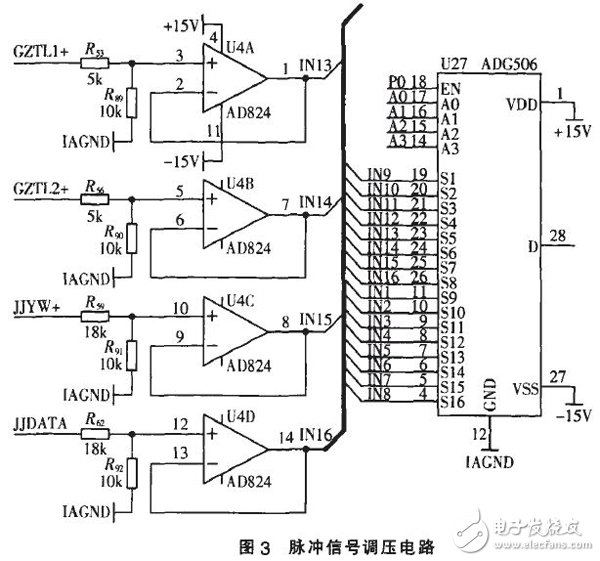

第一部分为采集脉冲信号幅值功能。脉冲信号由通用测试台输入被测板卡后首先经过调压后输入运放AD824.经过电压跟随后再输人模拟开关ADG506。ADG506的最高输入电压为+15V,而箭机计算机字信号源高电平为+28V。因此,箭机计算机字数据源脉冲在进入模拟开关前必须进行调压,详细电路如图3所示。

图3为脉冲信号和箭机计算机字移位脉冲信号和数据源信号调压电路。脉冲信号高电平为15V,经过电阻 调压后变为10V。箭机计算机字数据源的移位脉冲与数据脉冲高电平调压原理与此相同 ,调压后脉冲信号高电平幅值为10V。

脉冲信号经过调压后输入运放AD824.其目的是进行电压跟随。电压跟随即输入电压与输出电压相同.其放大倍数恒小于但接近于1.电压跟随器的输入阻抗高.输出阻抗低。在电路中可以起到阻抗匹配的作用.并可以起到增强电路驱动能力的作用。

本模块需要采集64路脉冲信号的幅值.不可能采用每路脉冲信号配置一片AD转换器的方案.因此本卡采用一片ADG506对应8路脉冲信号.分通道采集的方案。该模拟开关包含16路输入通道,其通道间切换频率高达2.5MHz.而脉冲信号最高频率为500kHz。因此该器件满足需求。

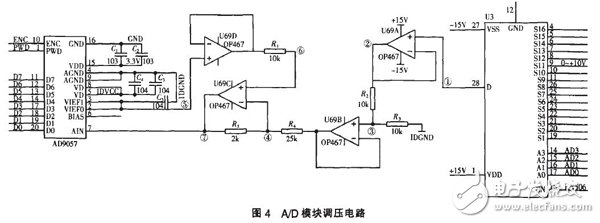

模拟开关输出电压与输入相同.而本板卡采用的AD9057的最高输入电压(基准电压)为2.5V。因此需将模拟开关输出的脉冲信号再次调压。其电路图如图4所示。

模拟开关输出脉冲的幅值在O~IOV之间。在图4中①点输出最高电压为+IOV,通过U69A电压跟随后②点电压也为+10V,经过电阻 ,分压后③点电压为+5V。经过U69B电压跟随后④点电压为+5V。AD9057的基准电压为+2.5V,即⑤点、⑥点电压为+2.5V,根据虚短虚断的原理得:

由式(1)可以推出⑦点电压为2.3V,满足AD9057的电压需求。脉冲信号经过AD9057转换后变为8位并行数据信号送于主控逻辑芯片FPGA.FPGA负责采集AD转换后的数据.并将数据打包后存于外部存储器中。

第二部分为采集脉冲频率及个数的电路.对于采集脉冲频率及个数的电路与脉冲量接口电路相同,在此不做说明。脉冲量信号经过光电隔离器件(HCPL一0631)后,变成单路脉冲,由FPGA采集此脉冲信号,并对脉冲高电平信号进行计数。在判断到脉冲信号发送完成后将数据打包存于外部存储器中。

3 脉冲量采集模块程序设计

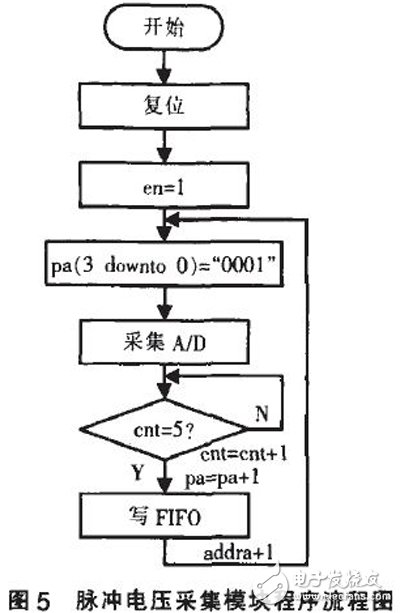

本模块程序共包含2个进程:电压采集进程和频率、个数采集进程。该模块程序逻辑框图如图5所示。

在采集电压信号时.首先由FPGA使能模拟开关,再选择模拟开关8路中的一路。

模拟开关将脉冲信号送于AD9057.由其将脉冲信号转化成8位数据,此时FPGA连续采集5次。然后再选通模拟开关的下一路.以此类推完成所有脉冲信号数的幅值采集工作。FPGA将采集到的数据依据不同的脉冲类型分别打包并加上帧标识存于外部存储器。

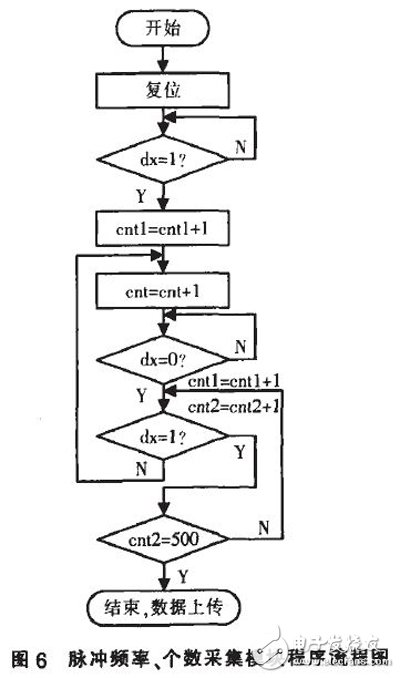

如图6所示.d)【为脉冲信号输入,cntl为频率计数器,cnt为脉冲计数器,cnt2为延时计数器,在采集脉冲频率及个数等参数时.主要采用计数器原理。当判断到脉冲信号的高电平后.计数器cnt、cntl分别加1.然后再判断脉冲信号的低电平,在未检测到脉冲信号的低电平时计数器cntl持续自加.直到检测到脉冲信号的低电平时,cntl停止自加,此时它的值为脉冲信号的半个周期长度,由此可推出脉冲信号的频率。当脉冲信号为低电平时.开始检测脉冲信号的下一高电平.在未检测到脉冲信号的高电平时.计数器cnt2持续自加.若检测到高电平后cnt2清零.cnt加l。反之,若cnt2自加至0X1388H后仍未检测到脉冲信号的高电平则说明脉冲信号已经发送完毕(该进程工作时钟频率为10MHz.而脉冲信号的最小频率为1Hz.因此当计数器cnt2自加至OXl388H.说明在500ms内没有脉冲信号.脉冲信号已经发送完成),则将计数器cnt、cntl所记录的数据打包加上帧标识存储至外部存储器。

利用计算机字数据源需要采集的参数有数据源、移位脉冲的时延等。进程工作时首先判断帧同步信号(该信号为此功能模块另一进程产生),当判断到帧同步信号的下降沿时计数器ent开始计数.当检测到移位脉冲的上升沿时.计数器停止计数。并采集数据位当前数据.存人八位寄存器中的最高位。当八位寄存器存满后存人FIFO.FIFO达到一定深度后加入帧标识存人外部数据存储器。

4 结语

信号采集技术是系统速度和精度等性能提高的关键之一。该基于FPGA的脉冲量采集模块技术提高了采集的速度和精度.具有较强的应用性。仿真和测试验证了系统的稳定性和可靠性.信号采集正常,没有出现漏采集和误采集现象.该设计已在某通用测试台的研制中得到应用,取得了满意的结果。同时.该设计的思想和方法可以应用到更加广泛的信号采集技术领域。

该模块主要采集脉冲信号和发送数据源.对工作时钟要求较高。为了更好地实现通用性,如果对FPGA提供多路不同时钟.在生成不同频率脉冲时采用特定工作时钟.可以大幅提高脉冲频率的精度。

-

脉冲信号采集方案2016-08-15 7647

-

以FPGA为平台怎么测量脉冲宽度的verilog语言2017-03-21 6524

-

基于FPGA的数字量采集模块设计2010-12-16 461

-

脉冲量输入信号调理电路2009-02-09 2121

-

基于FPGA的高速数据采集控制模块设计2012-05-24 814

-

基于FPGA的多功能数据采集模块设计金刚2017-03-19 738

-

基于FPGA的高速采集和深存储的模块设计2017-11-18 3149

-

基于FPGA为核心的多路模拟信号采集模块的设计资料免费下载2018-10-12 1115

-

模拟数字量的采集模块是如何在工业中应用的2019-08-06 1623

-

在工业应用中的数字量采集模块2019-08-29 2839

-

基于ACEXIK系列FPGA器件EPIK10实现8路脉冲量计数系统的设计2020-07-28 2270

-

基于FPGA的X射线脉冲信号数据采集系统2021-06-01 1189

-

PLC/编码器/电机电表脉冲计数信号数据采集模块2022-11-25 2843

-

PLC编程算法:开关量、模拟量、脉冲量2023-02-22 1153

-

plc脉冲量的应用场景有哪些2024-09-16 1522

全部0条评论

快来发表一下你的评论吧 !