关于基于FPGA的高速实时数据采集存储系统的介绍和分析

FPGA/ASIC技术

描述

在传统的数据采集系统中,A /D的控制和数据的转存均通过CPU或者MCU来完成。在这种方式下,将A /D转换的结果读入,然后再转存到片外的存储器中,这一过程至少需要4个机器周期。即使对于ARM芯核的单片机(CPU采用流水线结构, 1个机器周期占1个CLK) ,使用33 MHz的晶振,它的最高转存数据速度也只达到8Mbit/ s. 在高速采样系统中,这种方式一方面占用太多CPU资源,另外也远远不能满足高速采样的速度要求。同时,在数据采集系统的前端数字信号处理(DSP)中,如FFT、F IR、IIR滤波等,以往一般都是利用DSP内部的硬件乘法器加软件控制来实现。DSP 的工作方式是通过内部的CPU 逐条执行软件指令来完成各种运算和逻辑功能的,在排队式串行指令执行方式下,工作速度和效率也将降低。为了提高数字信号处理速度,现在一些实现专用算法的DSP模块和通信接口也由FPGA 或者CPLD 实现。基于上述原因,设计了以Virtex - 5系列的XC5VLX50为核心处理芯片的多路数据采集系统,它以硬件电路方式来提高速度[ 1 ]。

1 高速数据采集系统设计

1.1 高速数据采集系统的基本电路结构

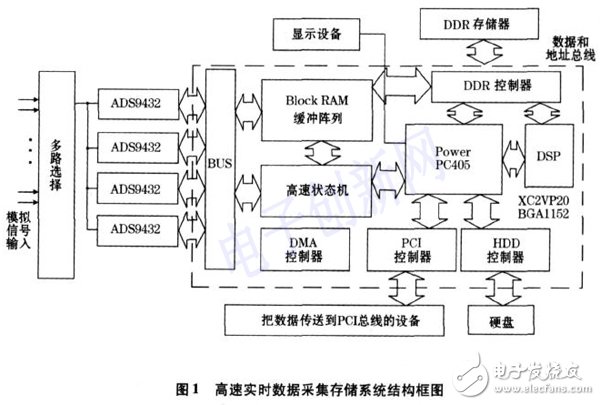

系统中,通过多路数据选择器选定多路信号中的一路进行采集,在高速状态机控制下,将采集到的模拟信号经过多片A /D器件流水转换之后,转换结果直接储存到FPGA XC5VLX50TFFG1136内部由Block RAM构建的高速缓冲RAM阵列中,然后转存至低速存储器( FLASHMEMORY)中,再由FPGA构成的专用数字信号处理单元进行数据处理。在嵌入式硬核CPU Power PC405的控制下又可以将FLASH MEMORY中的数据送入PCI总线设备或者硬盘中长期存储,同时也可以将采样结果在LCD上显示。该系统的结构框图如图1 所示。虚线内部的功能都是通过对FPGA芯片XC5VLX50TFFG1136硬件编程实现。

1.2 FPGA芯片XC5VLX50

XC5VLX50内部有丰富的资源,包括8个数字时钟管理器(DCM, 290 Kbits的分布RAM, 88 ×16KByte 的Block RAM, 88个18 ×18 的专用乘法器(DedicatedMultip liers)单元, 2个Pow2erPC405内核, 564个可配置I/O 引脚达(最多276 对差分I/O,

速度高达31125 Gbit / s,最高内部工作频率540 MHz. Power2PC405内核通过Xilinx提供的IP软核编程实现,文中使用了内

部一个Power PC 405作为主控制器,用来完成高分辨率的液晶显示器的控制和一些外围设备和整个系统的协调性控制[ 2 ]。

2 流水采样实现

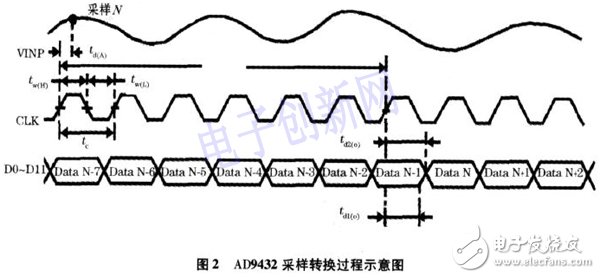

采用高带宽( 1 GHz) 高速( 80 MHz) 低功耗A /D 芯片AD9432 (12bit)作为A /D转换器件,采样时钟由XC5VLX50内部的锁相环实现。AD9432是一种单流水线ADC,它采用多个低精度闪电式ADC对采样信号进行分级量化,然后将各级的量化结果组合起来以构成一个高精度的量化输出。各级电路分别有自己的跟踪保持电路,因此当每级电路把信号传给下级电路时就可以接收上级传过来的数据,每级电路一次采样可在一个时钟周期内完成,但是存在流水线延迟的问题,AD9432采样转换过程如图2所示。

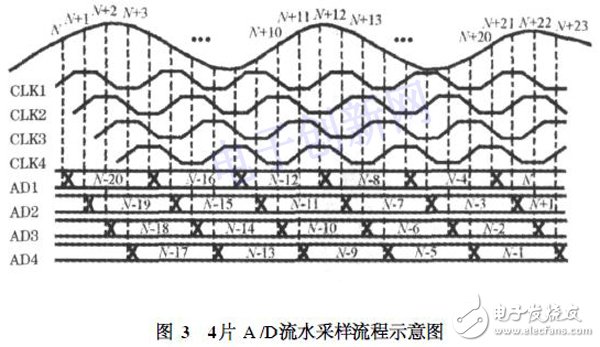

每次采样的最终转换结果要等待6~7个时钟周期后才能出现在输出端。AD9432的控制以及数据的缓冲转存采用状态机控制,当AD9 4 3 2接收到CLK信号后开始采样。由于每块A /D 的最高采样率仅有80MHz,在此采用了4块AD9432进行

流水采样,每块A /D的采样时钟相位延迟90°,这样在每个周期内是由4 块A /D均匀采样的,采样率等效提高了4倍。4块AD9432采样时钟的相位延迟利用FPGA设计的高速状态机以及内部数字时钟管理器(DCM)来实现。采用4片A /D相位延

迟并行流水采集的过程如图3所示,图中CLK1~4是4片A /D的采样时钟,在这种流水采集中,单流水线延迟的影响可以忽

略[ 3 ]。

3 数据的转存设计和分析验证

采集到的信号经过A /D器件转换之后,通过XC5VLX50内部高速缓冲,转存到片外存储器FLASH MEMORY中。系统中

XC5VLX50内部Block RAM阵列的控制比较简单,采用乒乓操作大大降低了采样数据读取处理速度。16块Block RAM分成

2组,时钟和控制信号均独立。系统工作时,高速状态机会不断地往Block RAM中放入采集到的数据。当采样数据放满1组

的8块Block RAM后自动切换到另外一组。同时并行从刚刚放满的8 块Block RAM 中以64 位的并行数据读入FLASH

MEMORY中( FLASH MEMORY内存具有可靠性高、互换性好、容量大等特点) [ 4 ]。

采用流水方式的4片12位的A /D的采样频率为320MHz,则数据流为480 Mbit/ s,但是FLASH MEMORY的最大存储速度为20Mbit/ s(忽略编程时间). 为了实现数据的实时存储,采用面积换取速度的原理,充分利用XC5VLX50的内部逻辑资源和丰富的I/O口资源,设计了2个存储器阵列,每个存储器阵列由24 片FLASH MEMORY,在XC5VLX50 内部进行乒乓操作,把480Mbit / s的数据量分流成20Mbit/ s,分别存储到24片FLASH MEMORY中,当FLASHMEMORY达到编程时间的时候转向第二个存储阵列,这样的外部乒乓操作就达到了FLASHMEMORY的最高存储效率,实现了数据的高速实时采集和存储, 2个存储阵列共享控制总线和数据总线,但是使能总线独立;在一个存储阵列内部,存储芯片控制总线共享,数据总线独立,这样能达到紧密协作和节省FPGA逻辑资源和I/O口资源的效果。而设计的FLASH MEMORY 控制器的速度达480MHz,数据带宽符合转存需要的速度,完全可以实现实时连续采样。数据采集结束后,DSP模块会在Power PC405的控制下对FLASH MEMORY内存中的数据进行高速处理,然后又放回FLASH MEMORY中,处理后的数据也能通过PCI总线传到带有PCI接口的设备中,或者通过USB总线存储到硬盘中,对PCI和硬盘操作均支持DMA66操作[ 5 ] 。

系统的Power PC405采用Xilinx的IP Core实现。FLASHMEMORY Controller、PCI Controller及USB Controller等功能电

路则是根据相应的数据传输协议自行设计,采用VHDL 编程实现,使用ModelSim进行功能仿真, Synp lify进行逻辑综合,将综合结果下载到XC5VLX50 器件中实现相应的系统逻辑功能。

在完成电路的软件与硬件系统设计以后,用Agilent16900Logic Analysis和高速示波器对该电路进行测试验证。16900

LA的多通道眼图的扫描可以迅速发现FLASH MEMORY总线中一些处于比较危险状态的信号线,比如由于阻抗的不匹配而造成Signal Integrity方面的问题。而LA可以验证电路时序是否正确。用示波器可以正确地量测到实际信号的波形,并进行眼图的精确扫描。用16900 Logic Analysis测量了FLASHMEM2ORY控制电路的部分时序,结果表明FLASH MEMORY总线逻辑功能正确,符合FLASH MEMORY总线规范标准。对于PCI Controller、IDE Controller、DMA Controller均采用了相同方式进行量测验证,结果均符合其协议规范标准,可以正常稳定地工作。

4 结束语

介绍了一种基于FPGA控制的,进行多片A /D器件流水采集的高速数据采集系统设计,对流水采样的原理和实现、采集

中的数据转存控制电路和FLASHMEMORY控制电路的设计进行了重点分析。在完成电路的软件与硬件系统设计以后,用Agilent 16900 Logic Analysis和高速示波器进行测试验证。结果表明该系统可以可靠稳定地工作,最高实时采集采样频率可以达到480MHz. 并应用到了雷达信号高速数据采集器中,在多次的实际应用中表现稳定、可靠。

-

基于FPGA的高速实时数据采集系统设计2012-08-20 15917

-

基于FPGA的数据采集存储系统2012-10-29 3460

-

常见的几种不同的高速数据采集存储系统介绍2019-07-04 3090

-

分享一款不错的基于FPGA超高速雷达住处实时采集存储系统2021-04-15 2659

-

求一种多路数据采集存储系统的设计方法2021-05-07 1514

-

实时高速数据采集与存储系统的一种实现方法2009-08-07 781

-

基于FPGA的多通道同步数据采集存储系统2010-12-27 1204

-

基于SAR系统的高速数据采集和存储系统2010-11-29 1661

-

高速数据采集与存储系统技术方案2011-07-07 796

-

基于SATA硬盘和FPGA的高速数据采集存储系统2011-11-15 1703

-

Tera-Store高速数据采集存储系统2017-10-24 1319

-

高速数据采集记录系统2018-11-13 1026

-

如何使用FPGA设计高速实时数据采集存储系统的资料概述2018-12-10 1524

-

PLC实时数据采集如何实现?2022-11-24 3304

-

PLC实时数据采集如何实现2022-12-08 2278

全部0条评论

快来发表一下你的评论吧 !