在FPGA内设计的高阶音频数字均衡滤波器整体设计方案详解

RF/无线

描述

音频均衡器作为高品质音响不可或缺的关键附属调节设备,在音效调整修饰方面起着至关重要的作用。一般音频均衡器有数字和模拟两种实现方法,模拟方法用有源和无源滤波器组实现,受器件温度等特性的影响,难以达到较高的可靠性和一致性,且成本较高。数字实现方法采用数字滤波器,具有较高的灵活性和可靠性。常用的数字滤波器有IIR和FIR两种。IIR滤波器结构简单,所需的存储空间小,但其相位是非线性;FIR滤波器是线性相位滤波器,这对高品质音效处理是必要的。本文通过在FPGA内设计了1 024阶FIR滤波器实现数字均衡滤波,通过系数的重载实现多种频率响应的均衡特性。

1 总体概述

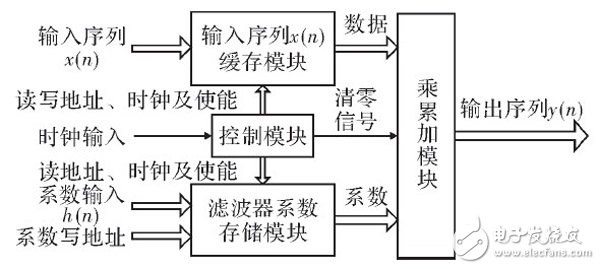

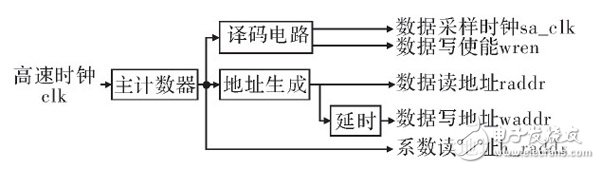

文中设计的FIR音频均衡滤波器采用多相滤波结构,用时间换取空间,节省FPGA内部资源,以达到在固定资源下的最大阶数。实现结构框图如图1所示。

图1 数字滤波器实现结构框图

输入序列以及滤波系数分别存储在缓存阵列中,在时钟同步下由控制模块通过生成相应的读写地址及使能信号,使其按照一定次序输出到乘累加模块进行运算,并输出最终结果。系数可通过外部输入重载,以实现不同的均衡特性。EP1C3系列FPGA共有13个M4K块,每个为256 ×18位,取数据和系数的位宽为16位。为了充分利用有限资源,并考虑处理速度及音频信号速率要求,取每个缓存子模块的存储深度为256,即将乘累加模块复用256次,每256个系统时钟周期运算一个采样点数据,输出一个滤波结果。每个缓存子模块占用一个M4K块,连续4个子模块串联,就可实现256 x4=1 024阶的要求,再考虑系数占用的空间,总共消耗8个M4K块。这也是在有限资源下能实现的最高阶数。

2 各模块实现

2.1 输入序列缓存模块

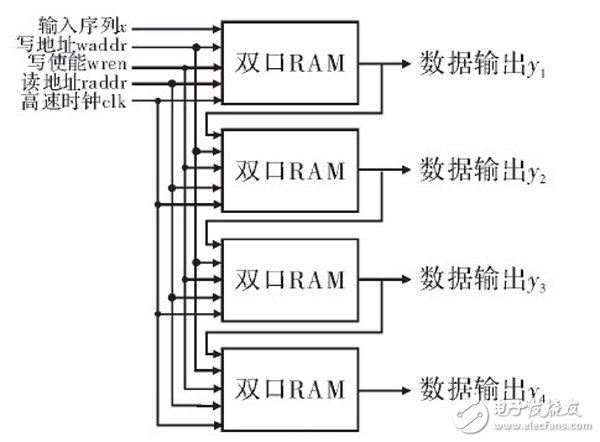

输入序列缓冲模块采用双口RAM模块实现,将4个级联使用,如图2所示。4个子块使用相同的读写地址及使能信号,采样数据从第一个子块输入,第一个子块的数据输出端与下一级子块的输入端直接相连,依次类推。每个缓存子块的数据y1~y4都输出给乘累加模块进行运算。

图2 输入序列缓冲模块实现框图

该模块的关键是读写地址的控制,写地址waddr必须滞后读地址raddr一个时钟周期,这样子块当前输出数据会在下个时钟写入下一个子块的相应单元。256个周期后,子块的数据整体移到下一个子块。

2.2 滤波器系数存储模块

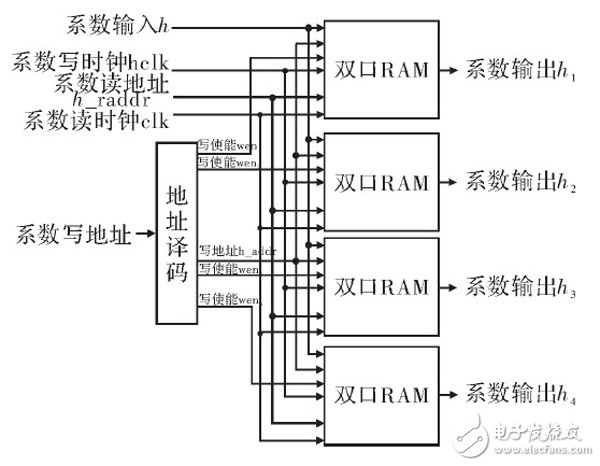

滤波器系数存储模块和输入序列缓存模块相对应,采用双口RAM模块实现,共有4个256深度的双口RAM模块,如图3所示。

图3 滤波器系数存储模块实现框图

4个子块使用相同的输入数据线,通过系数写地址的译码,生成各子块的写使能’wen1~wen4和写地址h_addr,控制输入的系数按照顺序依次存入到RAM中。系数的读地址h_addr由控制模块生成,4个子块共用一个读地址,输出与数据相对应的系数h1~h4到乘累加模块,进行乘累加运算。

2.3 控制模块

控制模块产生输入序列缓存模块的读写地址、使能信号以及滤波系数存储模块的读地址、使能信号,并对乘累加运算进行控制。

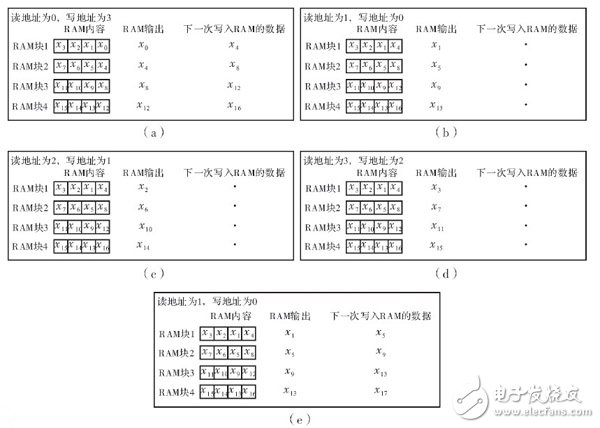

输入序列需要在缓存模块中反复移位输出进行运算,每256个时钟周期输入1个数,输入序列的写地址必须滞后读地址一个时钟周期,才能保证数据的连续、不丢失。这样新写入的数据不在固定的位置,就要求读地址也不是单纯的累加关系。以每个RAM块深度等于4为例研究读写地址的关系,如图4所示。

图4 每个RAM块深度为4时读写顺序

可见此时输入序列的读地址顺序如图5所示。

图5 每个RAM块深度为4时读地址

由此类推可得实际输入序列缓存模块的读地址如图6所示。

图6 输入序列缓存模块读地址

整个控制模块的实现如图7所示。主计数器整体计数,每256个时钟周期,地址产生模块就把计数器的计数值整体加1,作为输人序列的读地址raddr输出,实现了图6所示的地址顺序。写地址waddr由读地址raddr经延时一个时钟周期获得。由于输入序列是按时间顺序输出的,故滤波系数只要从存储阵列中也相应地顺序输出就可以了,将主计数器的计数值直接引出作为滤波系数阵列的读地址h_addr。

图7 整个控制模块的实现

主计数器的输出经过译码电路后,输出数据的低速采样时钟sa_clk,用来同步输入序列。还输出输入序列的写使能wren,每256个时钟周期使能一次,写一次数据。

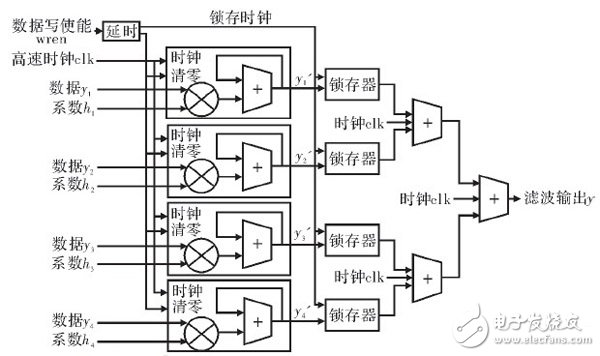

2.4 乘累加模块

乘累加模块负责将输入的数据和系数进行乘累加运算,每256个时钟周期输出一个滤波结果。其实现框图如图8所示。

图8 乘累加模块实现框图

输入序列缓存模块输出的数据y1~y4和滤波器系数存储阵列输出的相应系数h1~h4在该模块进行乘累加运算。每256个时钟周期,计算完1个采样点数据的4个部分y1’~y4’,由锁存器锁存,经两级流水线加法器后得到最终滤波结果y,然后将累加器清零,开始准备下个采样点数据的计算。其中,锁存器的锁存时钟及乘累加器的清零信号都由输入序列的写使能wren经过相应的延时处理后得到。

3 仿真结果

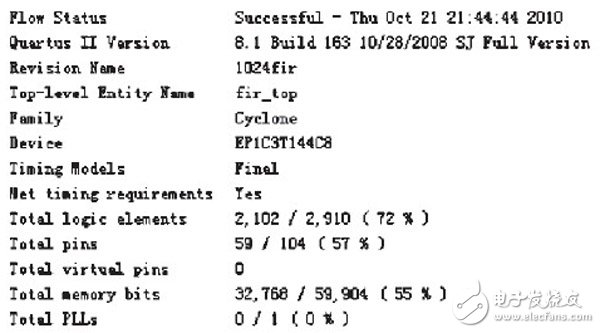

对设计的均衡滤波器进行综合编译,编译报告如图9所示。

图9 编译报告

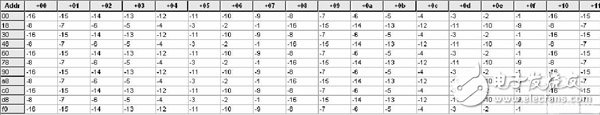

可见该1 024阶FIR均衡滤波器在EP1C3系列FPGA内得以实现,仅占用其约70%的逻辑资源和约50%的存储空间。为了验证该设计功能,将滤波器系数利用存储器初始化文件进行初始化,存储的系数如图10所示。

图10 滤波器初始化系数

为了直观验证,输入序列x取为δ序列,即x中只有1个数据为1,其它为0。根据滤波器及卷积的相关知识,输出结果y=x*h=δ*h=h,即为滤波器系数。仿真结果如图11所示。

图11 滤波器仿真结果

输入序列x只有1个采样时钟周期为数据1,其它全为0,fout为输出的滤波结果。可见结果为-1~-16的重复数据,与图10所示的滤波器系数一致,滤波器工作正常。

4 结束语

利用EP1C3约70%的逻辑单元及约50%的存储空间,设计了1024阶FIR数字滤波器,并通过重载系数,可实现多种频率响应的均衡特性,实现了简易数字均衡滤波器的功能,达到了设计目标。

-

高阶FIR正交镜像滤波器的设计2011-08-29 757

-

高阶音频均衡滤波器的FPGA实现2011-10-19 758

-

基于FPGA的FIR数字滤波器设计方案2013-10-08 9464

-

FIR数字滤波器设计方案2017-12-07 973

-

高阶程控滤波器的研究2009-12-05 0

-

基于FPGA的高阶FIR滤波器设计2012-08-20 0

-

怎么设计基于FPGA的高阶音频均衡滤波器?2019-08-26 0

-

介绍一个声音活动检测功能的音频数字滤波器2022-03-02 0

-

数字滤波器在FPGA中的实现2010-02-09 611

-

高阶滤波器的设计2010-05-23 7357

-

基于FPGA的IIR数字带通滤波器的设计方案及实现2014-02-13 7373

-

使用FPGA构建的数字滤波器设计方案2014-07-24 9049

-

基于FPGA的高阶大位宽超声相控阵滤波器设计_马骏2017-03-19 584

-

高频数字抽取滤波器的设计2018-02-21 2065

-

简易LC滤波器设计方案2021-06-22 1630

全部0条评论

快来发表一下你的评论吧 !