利用FPGA技术能更方便灵活设计出浮点运算器

可编程逻辑

描述

FPGA(现场可编程门阵列)技术的理论研究和实际应用正越来越受到人们的重视。FPGA 技术常常使一些原来比较难解决的技术瓶颈得以轻松实现,从而使产品的开发周期大为缩短,性能价格比大幅提高。运算器作为计算机的加工处理部件,是CPU(中央处理器)的重要组成部分。作为典型的PC机一般都至少具有一个定点运算器。在586 之前的机型中,由于当时硬件条件和工艺的限制,浮点运算器一般以协处理器的形式出现。进入20 世纪90 年代后,随着工艺水平的提高,一个芯片上集成度不断提高,如今浮点运算所要求的一些硬件已可以集成到CPU 中,因此,作为浮点运算器的代表的协处理器也逐渐被集成度很高的CPU 中的一部分所代替。

浮点运算

定点运算器主要是用于实现对定点整数和定点小数的算术运算、对逻辑数据的逻辑运算以及对主存的地址计算等。

浮点数比定点数的表述范围宽,有效精度高,更适合于科学计算与工程计算。浮点运算可分为两类:非规格化和规格化浮点运算。非规格化浮点运算,不要求操作数是规格化数,对运算结果也不要求规格化处理。而规格化浮点运算只能对规格化的浮点数进行操作,并且要求对运算结果加以规格化处理。由于规格化浮点数具有惟一的表示形式,而且在计算机中尾数能获得最大的有效数字,所以在一般的计算机中一般选用规格化浮点运算。

浮点加、减运算

浮点加减法运算规则

设有两个浮点数x 和y,分别为

其中Ex 和Ey 分别为数x 和y 的阶码,Mx 和My 分别是数x 和y 的尾数。

两浮点数进行加减的运算规则是

浮点加减法运算步骤

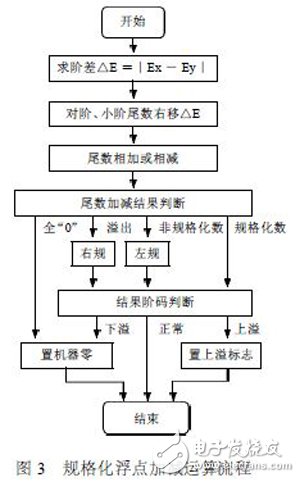

完成两个浮点数加法或减法运算,需要以下几个步骤完成。

(1) 对阶:两浮点数进行加减,必须使它们的阶码相等,这个过程称为对阶。对阶的第1 步是求阶差:

对阶的规则是小阶向大阶看齐,即使阶码小的尾数向右移位,每右移一位阶码加1,直至两数的阶码相等( E=0)为

止。右移的位数等于阶差| E|。当然尾数右移也会发生数码丢失,但这时丢失的仅仅是尾数的低位部分,误差较小,而且

可以通过舍入方法来控制误差。

(2)求和或求差:按定点加减的规则求两尾数的和或差。这个过程中所使用运算逻辑单元与定点运算逻辑单元类似。

(3)规格化:求和之后得到的数可能不是规格化的数,为了增加有效数字的位数,提高运算精度,必须将求和的结果规

格化。

当尾数用二进制表示时,浮点规格化的定义是尾数M 应满足:

(4)溢出判断:在进行运算时,可能出现阶码溢出的情况。当阶码超出上限时,称为阶码上溢,它表示浮点数的绝对值超出表述范围。当阶码小于下限时,称为阶码下溢,它表示浮点数的绝对值已在浮点数表示的分辨率之下。通常阶码上溢时要进行相应的处理,阶码下溢时要当作机械零处理。

浮点乘、除运算

浮点乘除法运算规则

两浮点数乘法的运算规则是

即两浮点数相乘,其乘积的阶码为相乘两数的阶码之和,其乘积的尾数为相乘两数尾数之积。

两浮点数除法的运算规则是

即两浮点数相除,商的阶码为被除数的阶码减去除数的阶码所得到的差,尾数为被除数的尾数除以除数的尾数所得

的商。

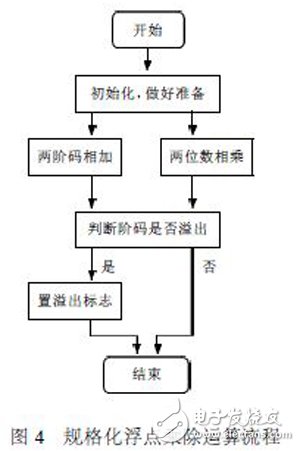

浮点乘除法运算步骤

两个浮点数乘除运算步骤为: 完成两浮点数阶码的加减运算,并判断结果是否溢出; 完成两浮点数尾数的乘除运

算; 根据结果的阶码判断溢出,如果上溢则置溢出标志。

浮点运算器的设计与实现

硬件平台

浮点运算器的设计与实现都是在开发的多功能EDA 实验台上完成的。该EDA 实验台采用FPGA-XC4010EPC84、

62256CPLD 和其它外围芯片(例如74LS244,74LS275)组成。XILINX 公司XC4000 系列是高容量、高成本的FPGA,能够进行无限次重新编程,配合公司的相应软件FOUNDATION 3.1,用户可以设计和调试出具有相当功能的控制逻辑。根据不同的要求,规划不同控制逻辑,通过把控制逻辑下载到FPGA 芯片中构成自己的硬件平台。

基于VHDL 语言方式

VHDL 语言具有极强的描述覆盖能力,在使用VHDL 语言实现的过程中,我们采用自顶向下的方法来实现浮点运算

器。步骤如下:

(1)分析系统的内部结构并进行系统划分,确定各个模块的功能和接口。

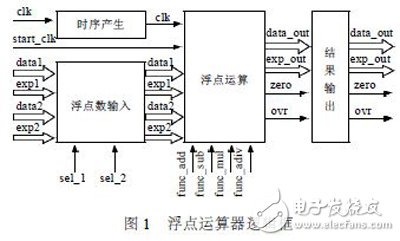

在设计中,根据浮点运算器的功能,将其划分为时序产生模块、浮点数输入模块、浮点运算模块和结果输出模块4 个模

块来实现。浮点运算器逻辑框图如图1 所示。

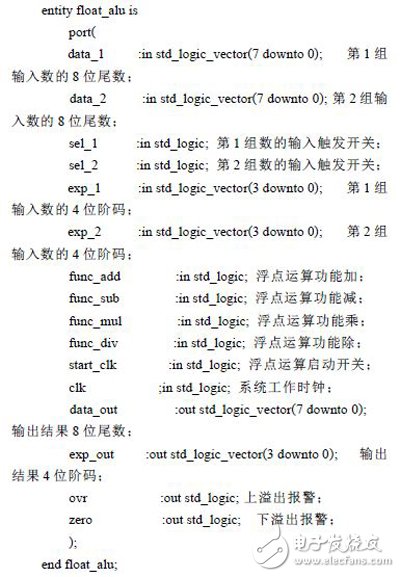

将这4 个模块组合成顶层设计float_alu,该顶层设计的端口定义分别为

(2)根据浮点运算器各模块的功能,分别编写程序,输入VHDL 代码,并将其编译成标准的VHDL 文件。

时序产生模块:该模块功能是对系统时钟进行分频产生相应的时钟信号。本模块中使用计数器级连的方法实现分频。

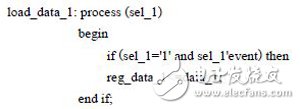

浮点数输入模块:开关sel_1 和sel_2 为输入数据的触发信号。多功能EDA 实验台上其余开关对应于8 位尾数和4 位阶码输入。当sel_1 开关按下,即sel_1=‘1’时,输入开关中的数据作为第1 组输入数的8 位尾数和4 位阶码;当sel_2 开关按

下,即sel_2=‘1’时,输入开关中的数据作为第2 组输入数的8位尾数和4 位阶码。在该模块中用进程process (sel_1)和process(sel_2)来实现。

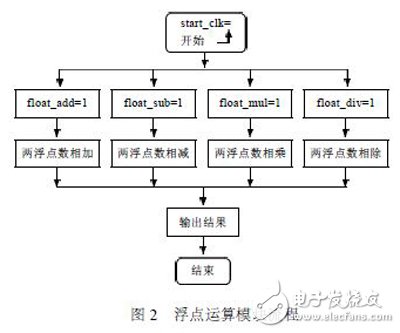

浮点运算模块:该模块主要完成各种浮点运算,是整个系统的核心部分。根据输入功能选择按键,在start_clk 信号上升

沿的触发下,对输入的两组浮点数进行运算。浮点运算模块的流程图如图2 所示。规格化浮点数加减运算流程图如图3

所示,规格化浮点数乘除运算流程图如图4 所示。

结果输出模块:该模块的功能是将浮点运算的结果输出至多功能EDA 实验台相应的发光二极管,以供观测。

(3)VHDL 源代码进行综合优化处理。经过上述分析后,用VHDL 语言对各个模块进行描述和实现,最后对VHDL 源

代码进行综合优化处理。

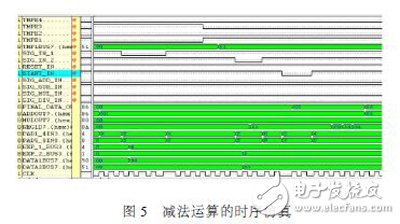

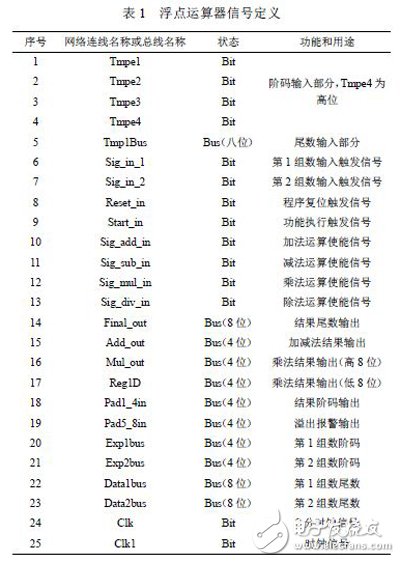

(4)仿真与配置。设计的正确性可以通过仿真来验证。图5 是浮点减法的时序仿真图。图5 中的信号定义如表1 所

示。其它各种运算的时序仿真方法相同,在此不再描述。

综合优化处理后的VHDL程序经仿真正确后再将生成的位流(bit)文件配置到到FPGA 的逻辑单元阵列,以定义器件

内的逻辑功能块和其互连的功能。

(5)下载验证。将步骤(4)得到的器件编程文件下载到目标芯片中,进行硬件的测试。浮点运算的结果显示在多功能

EDA实验台相应的发光二极管上,通过观测,可以证实所设计的浮点运算器是正确的。

基于原理图方式

采用原理图方式设计一个浮点运算器,首先必须分析出运算器的组成,然后使用基本的逻辑门和触发器来实现。

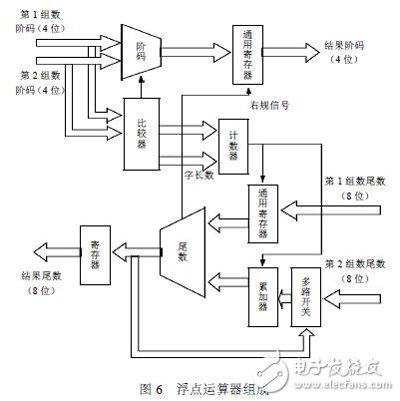

根据前面的分析可知,浮点四则运算比起定点运算来要复杂一些。在浮点运算中,阶码和尾数是分别进行运算的,并

且都是定点数(阶码为定点整数,尾数为定点小数)。因此,可以说,浮点运算器是定点运算器的扩充和强化。一般浮点运算器都至少具有两个定点数逻辑运算单元,一个用于阶码的比较和运算,另一个用于尾数的运算。从运算器结构来讲,不但要有尾数运算器,而且还要有阶码运算器。阶码运算器用来求阶差、修改阶码等操作,一般只进行加减运算。而尾数部件不但有加法器用以求和,还应有左移和右移线路,以实现对尾数的操作。

我们设计的浮点运算器以尾数为8 位,阶码为4 位的浮点数为例,根据实验开发平台资源,其组成如图6 所示。

由于XILINX 公司FOUNDATION 3.1 软件本身提供的器件相当丰富,小到逻辑门,大到全加器,类型丰富,所以我们开

发软件选用XILINX 公司的FOUNDATION 3.1。在FOUNDATION3.1 原理图编辑环境中设计出如图5 所示浮点运算器的

具体原理电路,规定器件的输入/输出,并定义好相应的网络名称和总线名称。在整个浮点运算器的设计过程中,核心部

件是加法器、移位寄存器和计数器。

计数器选择Foundation3.1 的标准库中CB4CLED(4-Bit Loadable Cascadable Bidirectional Binary Counter with Clock Enable and Asynchronous Clear)。移位寄存器选择Foundation3.1的标准库中SR8CLED(8-Bit Shift Register with Clock Enable and Asynchronous Clear)。

计数器开始工作后,根据相应的计数器输出信号,分别对移位寄存器进行操作。当功能选择的是加法或减法时,对阶的结果是为了移位,在实现过程中,我们假定为浮点数1大于浮点数2,则对浮点数2 的尾数进行右移。当计数器中的阶码差减为0 时,表示右移结束,接下去便是两浮点数的尾数相加或相减。当功能选择的是乘法或除法时,计数器的初始值是字长的值,在这里是8。开始计数过程前,乘法累计器被清零。计数开始后,乘法累加器、乘数寄存器和被乘数寄存器分别根据前面所说的定点数相乘所规定的操作进行运作。当计数器计数结束后,乘法结果分别存放于乘法累加器(高8 位)和乘数寄存器中。

当尾数计算和阶码计算都结束后,分别把结果的阶码、尾数和溢出标志送往EDA 实验台上的发光二极管。

与其它电路不同,浮点运算器在实现过程中必须注意时序问题。时序仿真是考虑了各个门的时延,设计出相应的逻辑。经过仿真和测试,其方法同VHDL 语言方式,确认相应的逻辑正确无误后,生成BIT 流文件,经下载板下载到实验系统上。

结论

在计算机应用、仪器仪表等领域的电子系统设计中,FPGA 技术的含量正以惊人的速度增加。浮点运算器是现代计算机中一个重要组成部分,利用FPGA 技术,能方便灵活地设计出浮点运算器。

-

cpu控制器和运算器组成的部件有哪些2024-06-30 5082

-

优秀的Verilog/FPGA开源项目-浮点运算器(FPU)介绍2024-04-26 6574

-

基于multisim的加减运算器2022-06-09 1917

-

运算器的相关资料下载2022-01-25 1286

-

求一种在FPGA上实现单精度浮点加法运算的方法2021-04-29 1251

-

浮点运算的FPGA实现2018-04-10 2037

-

基于FPGA的嵌入式处理器的浮点系统2017-11-22 2066

-

什么是运算器_运算器由什么组成2017-11-15 32627

-

基于FPGA高精度浮点运算器的FFT设计与仿真2011-12-23 997

-

浮点运算与浮点运算器2010-04-15 7290

-

定点运算器的基本结构(图解篇)2010-04-13 12148

-

运算器,运算器的作用和原理是什么?2010-03-24 33031

-

基于FPGA的实时互相关运算器2009-09-19 8515

全部0条评论

快来发表一下你的评论吧 !