以软件无线电为核心的在FPGA基础上的DQPSK调制解调系统设计方案详解

可编程逻辑

描述

一、引言

软件无线电提供了一种建立多模式、多频段、多功能无线设备的有效而且经济的方案,可以通过软件升级实现功能的提高。软件无线电可以使整个系统采用动态的软件编程对设备特性进行重配置。软件无线电软加载切换的实现,需要设计相应的功能波形组件。以下设计了一种差分四相相移键控(DQPSK) 的调制解调系统,该系统可以将软件加载到芯片上。

在数字信号的调制方式中,由于QPSK (四相移键控) 具有频谱利用率较高,抗干扰性较强,而且在电路上实现也较为简单等特点,使得它在卫星数字信号调制方式、数字电视技术、HFC 网络的用户线缆等方面得到了广泛的应用。在实际应用中,为了克服QPSK 解调时的相位模糊现象,在调制时对基带信号进行了差分编码,即DQPSK。

二、DQPSK 调制解调的系统方案

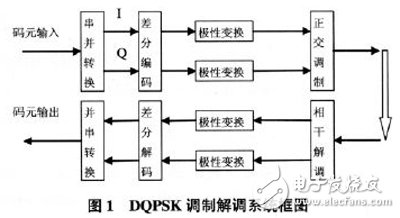

具体的DQPSK 调制解调系统框图如图1 所示,其中上半部分为调制系统,下半部分为解调系统。两个系统之间还要有相应的射频发送处理和射频接收处理。

以下主要按图1 的系统框图,基于FPGA 设计DQPSK 调制解调系统,采用Xilinx 公司开发的系统生成器为设计工具,特殊功能模块的实现采用Verilog HDL 语言编程实现。系统生成器具有强大的模块化设计功能,多个小功能模块让设计人员可以自由搭建所设计的系统。而且,系统生成器可以直接生成位流文件下载到FPGA,也可以生成工程文件,采用ISE 的开发环境可以对工程进行综合、仿真、下载。

1. DQPSK 调制解调的关键技术

(1) 差分编解码技术:QPSK 调制方式是一种四相位的调制方式。在实现上通常有正交调制法,相位选择法,脉冲插入法。其中,应用得最多的是正交调制法。本设计采用的是正交调制法。输入码元首先要进行串并转换,将串信信号变为两路I、Q 信号。假设I、Q 两路的组合用{a,b} 来表示,四相输入码元与调制的相位见表1。

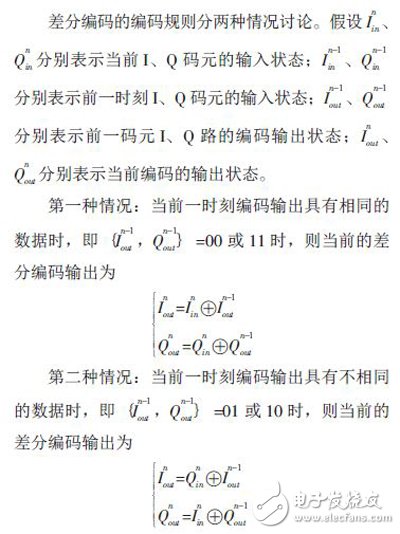

对于QPSK 信号来说,没有经过编码,直接采用输入的I、Q 两路码元来调制载波的相位,在解调时,由于基带数字处理载波跟踪环的鉴相特性,会出现四重相位模糊的现象。为了克服相位模糊的出现,基带调制时,要经过差分编码处理,再用差分编码后的码元按表1 的规则进行调相,这就是DQPSK。差分编解码是DQPSK 调制方式的特点,也是在设计基带调制时的一大难点。这里做详细的分析。

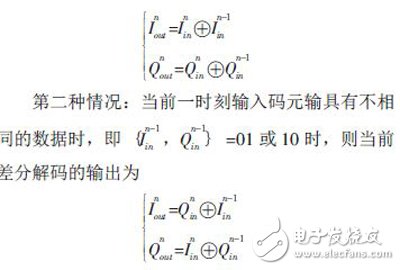

差分解码是编码的逆过程,也分为两种情况来分析。它主要由当前的输入状态和前一时刻的输入状态来决定当前的解码输出。

第一种情况:当前一时刻输入码元具有相同的数据时,即

或11 时,则当前的差分解码输出为

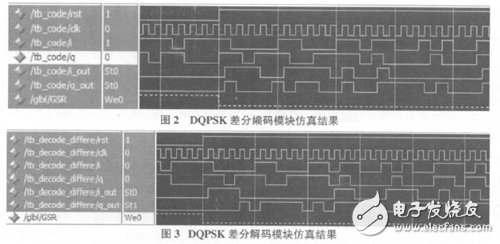

本设计中,差分编解码模块的实现采用VerilogHDL 语言在ISE 开发环境中设计仿真成功后,再采用黑盒子工具调用到系统生成器设计的调制解调系统中。采用Verilog HDL 设计成功后的差分编码模块用Modelsim 仿真后的的结果如图2 所示,差分解码的仿真结果如图3 所示。由图2 和图3 可看出,设计的差分编解码模块达到了预期的效果。

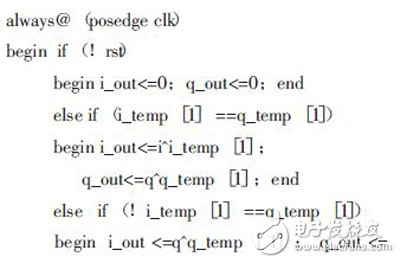

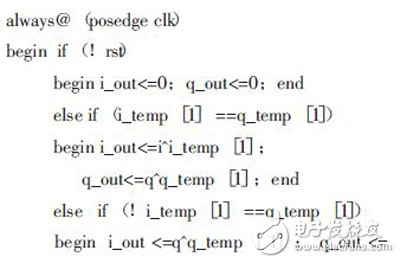

采用Verilog HDL 语言实现差分编码的关键代码为:

其中,i_out 和q_out 分别为I、Q 两路的编码输出。采用Verilog HDL 语言实现差分解码的关键代码为:

其中,i_temp 和q_temp 分别为2 位的寄存器,用来保存I、Q 两路当前和前一时刻的输入。

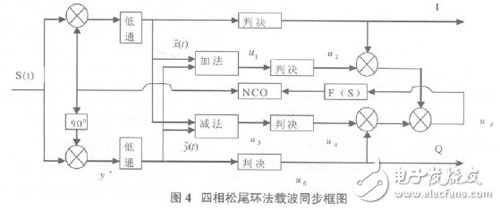

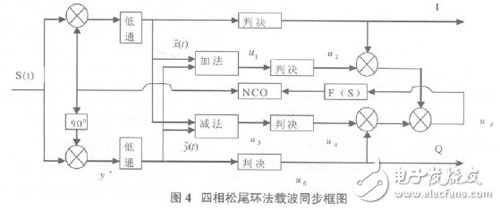

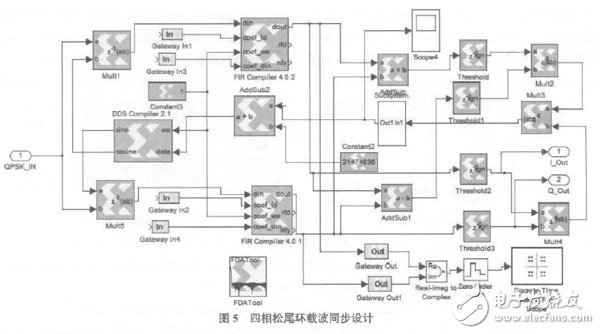

(2) DQPSK 载波同步的设计:DQPSK 的解调方法通常用相干解调法。采用相干解调法关键在于实现载波的同步。从已调信号中恢复出与发送载波同频同相的本地载波信号,是解调技术的难点。载波同步的方法通常有插入导频法、平方环法和科斯塔斯环法。科斯塔斯环法在实际的应用中有许多种改进的方案,本设计采用其中的一种改进方案四相松尾环法。四相松尾环的结构组成如图4 所示。图4 中,假设输入的信号为

式中,x(t)、y(t)分别为同相分量I 和正交分量Q 的基带信号。NCO 用于产生本地载波,其本振频率和发送频率一样。F (S) 为二阶环路滤器。判决器的数学表达式规定为

则经过之前各个模块的处理后,最终输入环路滤波器的误差信号为

误差信号ud 仅与发送载波与本地载波之间的相位差θ 有关。显然,四相松尾环的鉴相特性是一个周期性的方波。ud 经环路滤波器进行平滑,送到数控振荡器,迫使本地载波与发送载波达到同频同相。

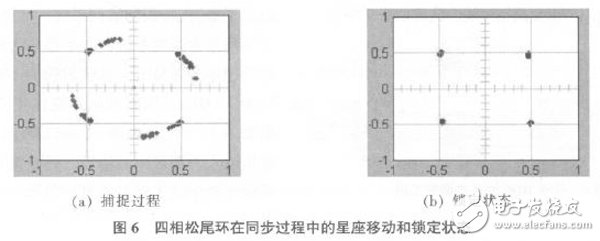

四相松尾环载波同步设计如图5 所示。松尾环对DQPSK 信号载波同步过程中的星座移动过程和最终锁定的状态如图6 所示。由图5 和图6 可以看出,一开始星座并不在对角线上。经过一定时间的捕捉过程后,星座最终收敛于四个点,且都在对角线上,抖动很小。

2. 其它模块的设计

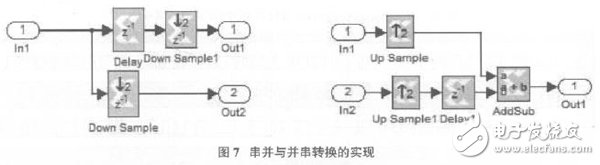

在调制端,串并模块的功能主要是实现将基带的串行数据转换为并行数据。转换后的并行数据为2 位。其原理是将输入串行数据分为两路后降2下采样。其中一路加入一个单位延时,实现错开的下采样,实现串并转换。解调端的并串模块相反,将两路数据上采样后相加实现。串并转换和并串转换功能的实现如图7 所示。

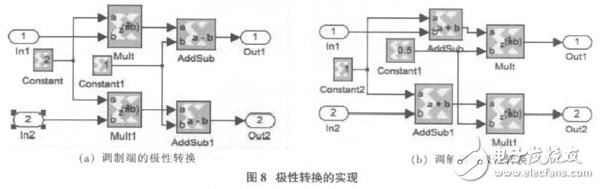

经差分编码后的信号需要进行极性转换,以便接下来做调制处理。极性转换将0、1 跳变的单极性信号转变为+1、-1 跳变的双极性信号。解调端的设计思路相反。极性模块的组成如图8 所示,其中图8 (a) 为调制端的极性转换,图8 (b) 为解调端的极性转换。

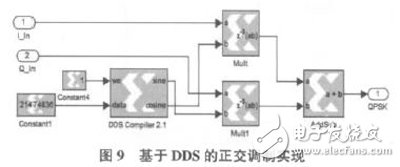

极性转换后的信号输入到调制模块。正交调制的实现,由可产生两路正交载波的DDS 和两个乘法器,一个加法器构成。I、Q 两路输入信号分别与DDS 产生的两路正交信号相乘,然后输入到加法器,随后输出。正交调制模块的构成如图9 所示。

其中,DDS 的频率控制字由系统时钟和载波频率所决定。

3. DQPSK 系统的仿真

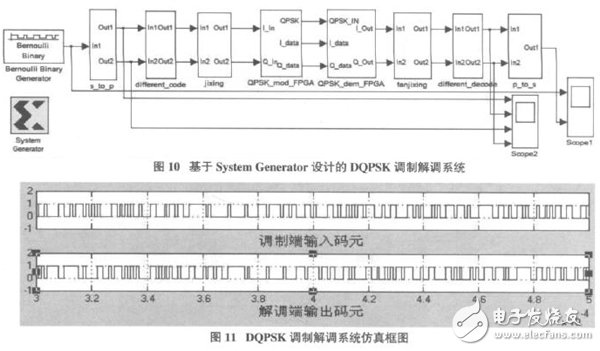

将各个功能模块按图1 的系统框图联在一起,组成了DQPSK 调制解调系统,如图10 所示。图中左半部分为调制系统,右半部分为解调系统。基带信号速率为1 MHz,系统时钟为100 MHz。载波频率为10 MHz。调制解调系统连在一起后的仿真结果如图11 所示。由图11 可以看出,解调端最终恢复出输入的基带原始信号。只要将调制系统和解调系统单独生成工程,即可下载到FPGA 芯片上实现独立的调制功能和解调功能。当然,在实际应用中调制系统输出的信号还要进行DA 数模转换,再进行射频处理,然后才发射出去。相应的,在输入解调端之前,也要进行相应的前端处理。

三、结束语

以上基于软件无线电的应用背景,采用系统生成器设计工具并结合Verilog HDL 编程的方法,设计实现了基于FPGA 的DQPSK 的调制解调系统。重点设计分析了DQPSK 差分编解码的实现,以及载波同步的实现。最终的仿真结果表明,设计的系统能够实现。

-

什么是软件无线电?2022-04-15 12989

-

分析一款不错的中频软件无线电系统的FPGA实现方案2021-04-29 1397

-

软件无线电中调制解调的实现AM-FM讲解2021-04-28 1303

-

一种适用于软件无线电的数字调制与解调算法的详细说明2020-08-04 1084

-

如何使用软件无线电实现QDPSK调制解调算法的硬件2020-06-30 1146

-

基于FPGA的软件定义无线电参考设计2019-07-04 1870

-

软件无线电助力3G通信发展2019-05-28 2234

-

基于软件无线电的高速QPSK调制器的设计与实现2017-08-02 2454

-

认知无线电中自适应调制解调器的FPGA实现2011-10-13 669

-

DSP无线电调制器的设计与实现2010-04-01 457

-

FPGA在软件无线电中的工程应用之数字调制解调篇2010-02-09 614

-

基于软件无线电技术的信号识别与调制解调系统2009-08-15 531

-

一种基于软件无线电的通用调制器的设计和实现2006-03-11 1294

全部0条评论

快来发表一下你的评论吧 !