基于Verilog HDL语言设计用于数字通信系统中的HDB3编解码器

可编程逻辑

描述

1 引言

数字通信系统的某些应用可对基带信号不载波调制而直接传输,其中传输线路对码型的要求如下:信码中不宜有直流分量,低频分量应尽可能的少,码型要便于时钟信号提取。根据这些要求,ITU-T(国际电联)在G.703建议中规定,对于2 MHz、8 MHz、32 MHz速率的数字接口均采用HDB3(三阶高密度双极性)码。HDB3码具有无直流分量,低频成分少,连零个数不超过3个等特点,便于时钟信号的提取和恢复,适合在信道中直接传输。这里利用Verilog HDL语言设计用于数字通信系统中的HDB3编解码器。

2 HDB3编码模块设计

要设计一个实用的编码模块,首先要深入研究其编码规则及其特点,然后根据编码规则设计符合电路特性的编码流程。HDB3码的编码规则包括:①将消息代码变换成AMI码,AMI码的编码规则是对码流中的非“0”符号进行正负交替;②检查AMI码中的连零情况,当连零的个数小于4个时,保持AMI的形式不变;当连零的个数达到4个或超过4个时,则将非零码后的第4个“0”替换成V码,其中V码的极性与前一非零码(+1或-1)的极性保持一致,例如,前面的非零码是+1,则将V码记为+V;③完成插V操作后,检查2个相邻V码之间非零码的个数是否为偶数,若为偶数,则再将相邻2个V码中后一个V码的前一非零码后的第一个“0”变为B码,B码的极性与前一非“0”码的极性相反,同时B码后面的非“0”码极性再次进行交替变换,保证极性交替反转特性。

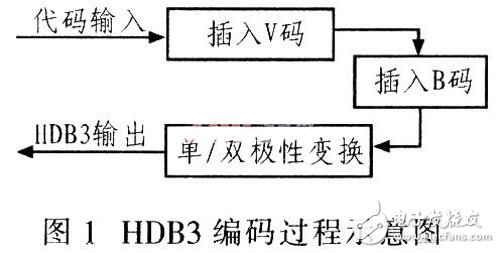

编码规则中出现的V码、B码只是作为标识符,最终的电路实现还是“0”和“1”这两种逻辑电平,因此需要采用二进制编码对“1”、“0”、V、B进行编码,“00”表示“0”、“0l”表示“1”,“10”表示B,“11”表示V。根据编码规则和利用FPGA实现的特点,将编码过程:首先插入V码,然后插入B码,最后是单双极性变换。如果按照编码规则的顺序设汁.应该首先进行单双极性变换,在完成插V和插B后,还需根据编码规则变换当前B码之后的非零码的极性,这需要大量的寄存器来保存当前数据的状态,导致电路非常复杂,占用大量的FPGA内部逻辑单元,实现难度大,且成本高。HDB3编码过程示意图如图l所示。

2.1 插入V码过程

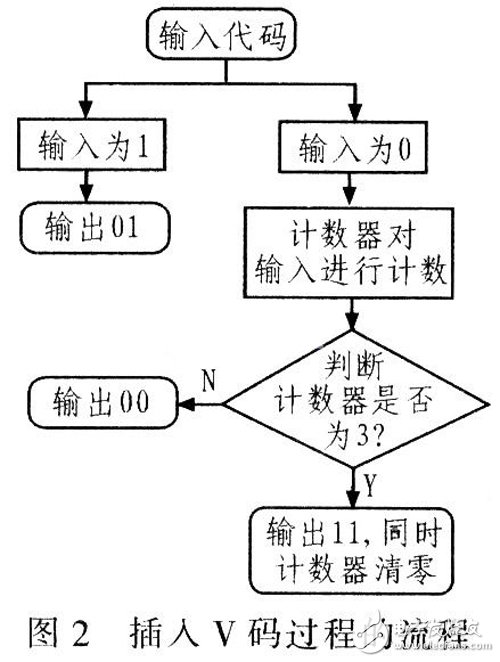

插入V码过程是对消息代码里的连零串进行检测,一旦出现4个连零串的时候,就把第4个“O”替换成破坏符V,其他情况下消息代码原样输出。输入的代码经插V操作后全部转换成双相码,即“0”变换成“00”,“1”变换成“01”,V变换成“ll”。图2是插入V码过程的流程,代码输入到插V模块后,如果输入是“l”,则输出为“01”,同时计数器清零;如果输入是“O”.则对输入“O”的个数进行计数,当计数器计数到第4个“O”时,输出“11”作为V码,同时计数器要清零用于下一轮检测;计数器未满4个“0”,则输出“00”。

2.2 插入B码过程

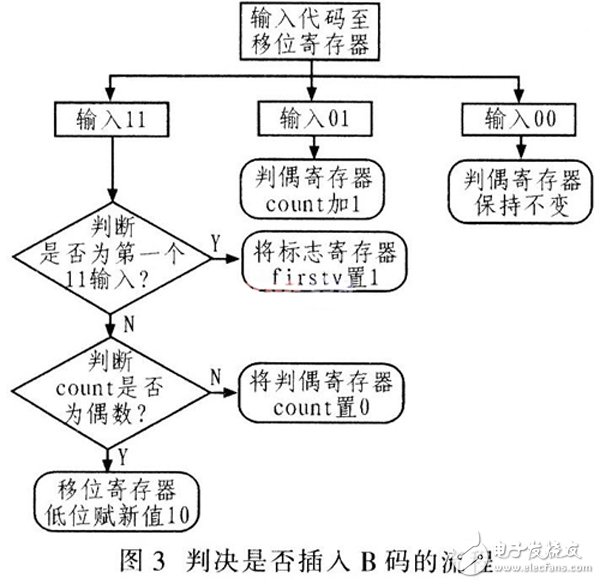

当相邻两个V码之间有偶数个非“0”码时.则把后一个V码之前的第1个非“0”码后面的“0”码变换成B码。该模块设计的难点在于插入B码的过程中涉及一个由现在事件的状态控制过去事件状态的问题,按照实时信号处理的理论,这是无法实现的,这里使用两组4位移位寄存器。采用4位移位寄存器是根据HDB3编码规则的特点确定,经插V后,连零串中的第4个“0”变成V码,代码中连零个数最多是3个,而插入B码操作是把在后一个V码之前的第1个非零码之后的“O”变换成B码,这个长度不超过3个“0”,因此只需4位寄存器就可通过判断现在的输入状态来决定是否应插入B码。图3是判断是否插入B码的流程.2组4位移位寄存器在时钟的作用下逐位将数据移出,在移位的同时还需对寄存器的最低位进行操作,即判断是否需插入B码。这部分功能的实现需设置一个检测当前V码状态的标志位firstv。

2.3 单双极性变换过程

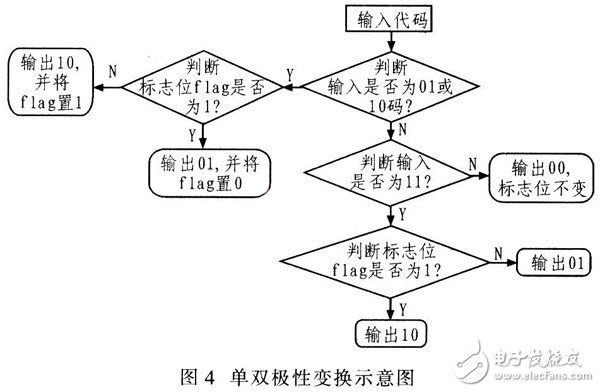

分析HDB3码的编码规则,发现V码的极性是正负交替的,余下的“1”和B码的极性也是正负交替的,且V码的极性与V码之前的非零码极性一致。因此可以将所有的“1”和B码取出来做正负交替变换,而V码的极性则根据“V码的极性与V码之前的非零码极性一致”这一特点进行正负交替变换。具体操作是设置一个标志位flag,通过检测判断标志位的状态来确定是否进行单双极性变换,标志位要交替变换以实现“l”和“B”正负交替,V码的极性也根据标志位变换。图4是单双极性变换过程的流程,“10”表示输出正电平,“Ol”表示输出负电平,“00”表示输出为零电平。

3 HDB3解码模块设计

根据编码规则,V码是为了解决4连零现象而插入的,而B码总是出现在V码之前,且只相隔2个“0”,因此只要在接收到的信号中找到V码并将其和前面的3位代码全部复原成“0”即可完成解码过程。

3.1 HDB3解码模块建模

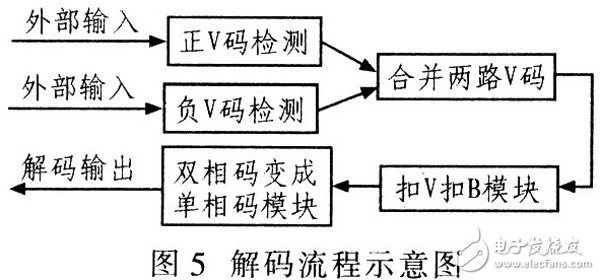

首先外围电路从HDB3码中提取出时钟、正整流信号和负整流信号,将这3路信号送到FPGA中,解码模块所用的时钟是从HDB3码中提取出来的时钟。从正整流信号和负整流信号中可以检测出2路包含V码的信号,将2路V码合成一路信号,然后对该路信号进行解码,最后将双相码变成单相码,图5是解码过程的流程。

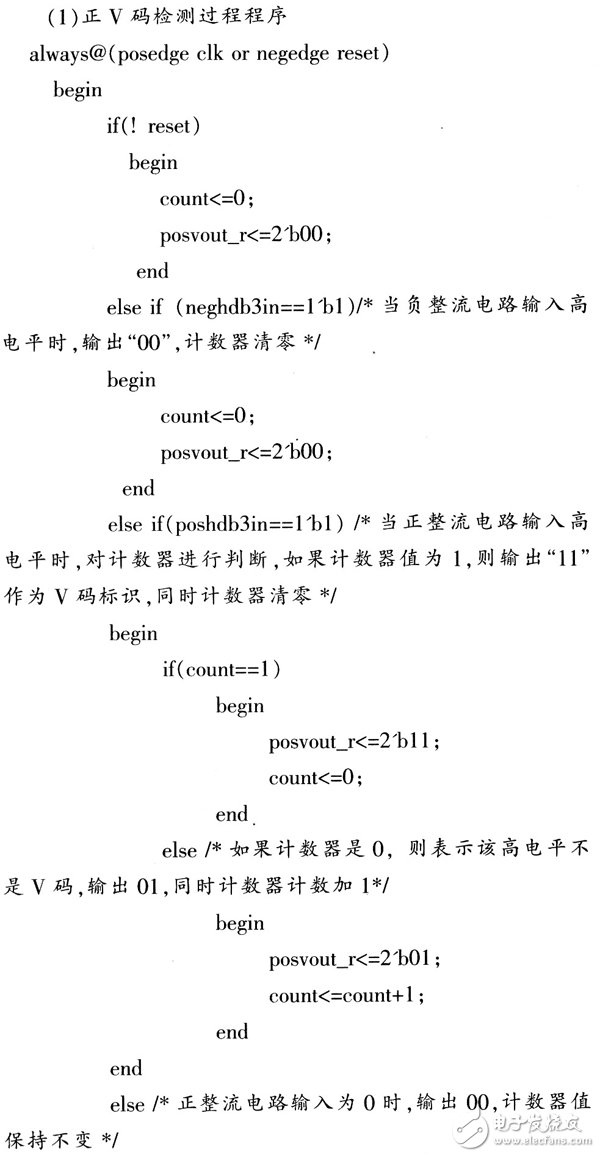

3.1.1 V码检测过程

V码检测同时进行正V码检测和负V码检测,这两个检测模块的设计思想类似,这里对正V码检测模块进行详细说明。为了方便描述,假设从正整流电路输入的信号为+P,从负整流电路输入的信号为-N。+V码检测模块是在-N的控制下,对输入的+P进行检测。其原理是:当+P的上升沿到来时,对输入的+P脉冲进行计数,当计数到1时,输出一个脉冲作为+V脉冲,同时计数器清零,在计数期间,一旦检测到-N信号脉冲,计数器立即清零,计数器重新从零计数。这是因为在两个+P脉冲之间,存在-N脉冲,说明第2个+P脉冲不是+V码,只有在连续两个+P脉冲之间无-N脉冲,才能说明这两个P脉冲在HDB3码中是真正同极性的,才可以判断第2个P脉冲实际上是+V码,达到检测+V码的目的。-V码检测原理与+V码检测类似,所不同的是,-V码检测电路是在+P控制下,对-N信号进行计数、检测和判定。

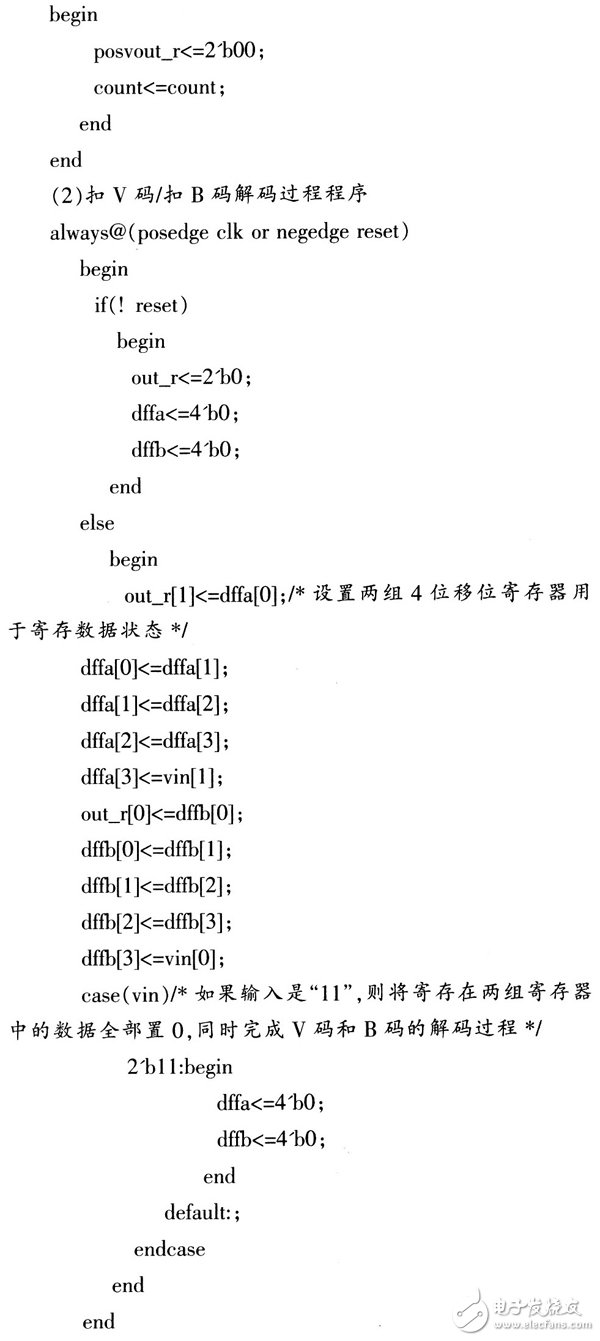

3.1.2 V码和B码解码过程

检测V码后,根据HDB3编码规则,只需将V码及之前3位码全部置零就可同时完成扣V/扣B操作。这又会涉及到一个由现在事件状态决定过去事件状态的情况,仍可采用两组4位移位寄存器解决。根据编码规则,V码是取代连“0”串中的第4个“0”,而B码总是出现在V码之前,且只相隔两个“O”,当输入是V码后,只需同时将4位移位寄存器置零,即可同时完成V码和B码的解码过程。扣除V码和B码后,还需将双相码变换成单相码,即当输入是“00”时输出“0”,输入是“01”时输出“l”,至此便完成了HDB3解码。

3.2 HDB3解码的Verilog HDL实现

以下利用硬件描述语言实现解码功能,这里只给出正V码检测模块和扣V码/扣B码模块的关键程序。

4 仿真分析

设计的编解码模块是误码检测仪的组成部分,采用Cy-clone系列FPGA(EPlC3T144C8)实现电路的核心功能,该器件拥有近3 000个逻辑单元,可满足整个系统设计的要求。

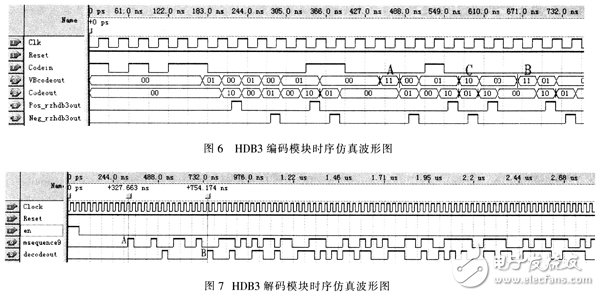

4.1 HDB3编码模块仿真分析

对该HDB3编码模块进行仿真验证,图6是仿真波形图,仿真时钟频率为32 MHz,Codein表示待编码的输入信号,输入的二进制代码为:101011000001100001;VBcodeout是插入V码和B码后的输出,观察波形发现,在A和B位置插入“11”作为V码,在C位置插入B码:Codeout是单双极性变换后波形,“10”表示正电平,“01”表示负电平.从波形可看出实现了正负交替;Pos_rzhdb3out和Neg_rzhdb3out是最终的归零码输出。该HDB3编码模块正确实现编码功能。

4.2 HDB3解码模块仿真分析

采用一个伪随机序列发生器产生测试数据,仿真时钟频率为32 MHz。将HDB3编码模块和解码模块相连接,观察输入和输出波形。

图7是仿真波形,其中msequence9是一个周期为511的伪随机序列码,在A时刻产生第1个高电平;将该码输入到HDB3编码模块,完成编码后输入到解码模块中进行解码,decodeout是解码后的输出,从B时刻开始输出解码后的数据,可以发现其波形与输入数据完全相同,因此解码模块实现了HDB3解码功能。

5 结论

所设计的HDB3编解码模块简单实用,利用FPGA实现HDB3编解码功能具有很强的灵活性,可以集成到不同的通信系统中,提高系统设计的速度。这里所涉及的仿真均为带有时序信息的仿真,仿真时钟频率设为32 MHz,该频率是HDB3码应用的最高频率。目前该编解码模块已成功应用于误码检测仪中,性能稳定可靠。

-

基于VHDL语言的HDB3码编解码器设计2023-10-13 483

-

怎样去设计一种基带HDB3编解码系统2021-08-09 1751

-

编解码器的工作原理是什么?2020-04-06 3208

-

基于FPGA的HDB3编解码的实现2016-04-15 4133

-

基于FPGA的HDB3编解码系统2013-04-07 2342

-

音频编解码器技术2012-02-03 5477

-

基于FPGA的曼彻斯特编解码器设计2011-12-28 1194

-

数字视频编解码器HUSS手册2011-04-22 1640

-

E1接口音频编解码器(立体声/AES数字)2011-03-02 3425

-

基于FPGA的HDB3编解码器设计2010-07-28 810

-

基于CD22103的AMI/HDB3编解码电路设计2010-04-13 2549

-

基于CPLD的HDB3码编解码电路的设计2010-02-24 842

-

什么是音频编解码器?2009-05-03 4267

-

用XC9572实现HDB3编解码设计2009-03-28 1925

全部0条评论

快来发表一下你的评论吧 !