怎么在FPGA或ASIC系统中实现高效高速USB 2.0接口?

可编程逻辑

描述

通用串行总线已经很普遍了,这是由于其使用简单,随插即用,并具有鲁棒性的优点。USB已经找到了进入曾经使用串口、并口作为其hoST接口的计算机外设的方式,需要接口到host计算机的产品现在也把USB作为其主要选择。USB提供多种带宽选择--低速、全速、高速、和现在的超高速--迎合了各种计算机外设以及工业和医疗设备的需要。

USB提供的吞吐量足够大,适合高带宽应用,如硬盘驱动器和扫描器。事实上,对于大部分计算机外设,如键盘,鼠标,PDA,游戏键盘,操纵杆,扫描仪,数码相机,打印机,USB已经是互连标准。

除了简单的电脑外围设备,FPGA应用也广泛存在,其可以受益于高速USB接口的增加。数字信号示波器、心电图、摄像机和数据采集系统是其中的一些例子。将USB接口添加到设备里将会大大扩展其能力。例如,在数据记录系统中(如数字储存示波器和心电图),得到实时数据可以通过主机实时传输,也可以通过网络传输这个数据,如图1所示。对于远程数据采集应用,将数字记录仪设备通过USB连接到主机也可以使设备进行远程控制,主机可以位于几英里以外,通过网络连接到USB主机。本文将探讨其设计方法,可以在FPGA或ASIC系统中实现高效高速USB 2.0接口。

图1 基于USB的分布式数据采集系统

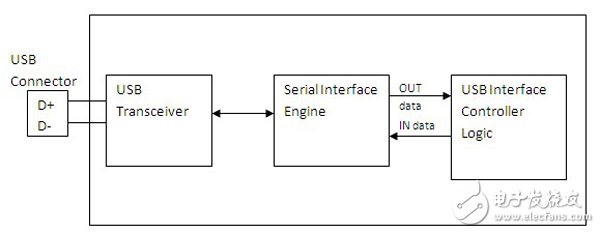

在介绍整合通用串行总线接口到FPGA或ASIC系统的各种方法之前,我们需要了解一下典型USB系统的工作原理。典型的USB系统由收发器,串行接口引擎(SIE),和接口控制器构成,如图2所示。

图2 典型的USB系统

收发器实现了USB协议的物理层。收发器形成了主设备和从设备之间数据连结的两端。USB接收器会有差分和单端两种输出。SIE进行串行数据的编码和解码,位填充,错误校验和其他信号级处理任务。它还将并行数据转换成串行数据,反之亦然。SIE应该连接到智能master,其通过控制端点相应主设备请求实施高级USB协议。master也将实现器件功能所需的应用级任务。

在这篇文章中,我们将讨论三种不同的方法,实现USB接口添加到FPGA或者ASIC系统。

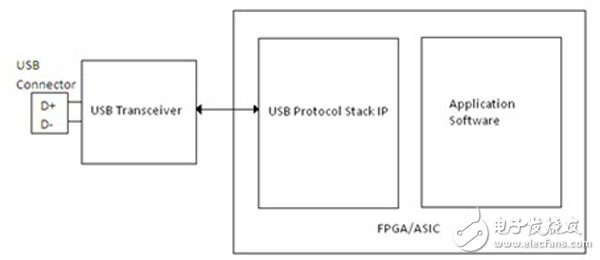

使用USB协议栈知识产权(IP)及外部收发器

在第一种方法中,我们可以在FPGA或ASIC中实现SIE(见图3)。

图3 FPGA + USB协议栈IP + USB收发器

SIE IP的主要功能是要执行数据编码和解码,CRC生成和错误校验,位填充,数据包ID生成,串到并以及并到串转换。这个IP可以自己开发或者可以从第三方供应商购买。FPGA也要执行上层USB协议。外部要使用一个收发器IC,比如赛普拉斯的TX2UL收发器芯片。这款收发器是USB 2.0认证的符合收发器红单元接口(UTMI)相关标准。所需的所有终端,包括Dplus 线上的1.5 K欧姆的上拉电阻,都是在芯片里内置了。

该方法的优点是所需外部硬件最少。使用这种方法的缺点是开发复杂的USB堆栈IP需要时间以及工程资源。SIE IP执行,上层协议和应用功能也占用了FPGA的大量资源。使用第三方的IP成本会很昂贵。

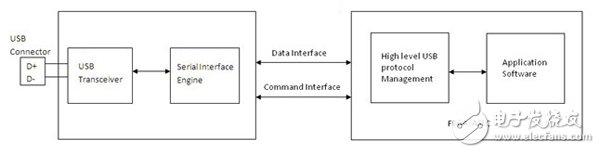

使用集成SIE和收发器芯片的USB桥

另一种把USB接口整合到FPGA设计的方式是连接一个外部串行接口引擎IC和收发器(见图4)。

图4. FPGA +桥芯片(SIE+ PHY)

在这里,FPGA只需要实现上层USB协议。任何从USB主设备收到的命令都会通过SIE传递到FPGA.FPGA需要包含逻辑来对这些命令进行恰当的响应。例如,在枚举过程中,USB外设会从主设备得到一个命令,请求它的描述符。在这个实现中,外部硬件,即收发器和SIE,会收到封包,并通过一个中断通知FPGA命令已收到。FPGA就会在STE读寄存器,并了解到外设已收到来自主设备的GET描述符命令。它会把正确的描述符发送给SIE.和使用外部收发器的SIE IC 不同,USB桥芯片如赛普拉斯的Mobl-USB芯片内置了SIE以及收发器。该控制器有两个双缓高速端点,其共享2 KB FIFO空间,最大化了灵活度和吞吐量,还有控制端点0.

这种实现的最大好处是,减少了FPGA一半的复杂性(例如,信号级协议管理)。然而,即使在这种情况下,还要占用一定数量的FPGA资源来执行上层USB协议。在这种情况下,需要做的决定是,要分析要分析所需外部硬件成本 vs. 节省的FPGA资源。

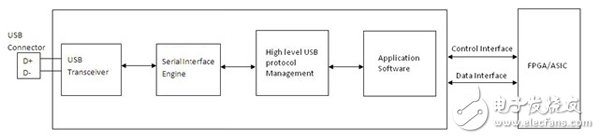

使用USB控制器与FPGA

图5. USB控制器+ FPGA

最后一种方式是,连接全功能 USB控制器到FPGA(见图5)。在这种情况下,所有的USB协议管理都会发生在FPGA以外。专门的USB控制器IC包含PHY,SIE,协议控制逻辑。

控制器可以提供灵活的端点可配置数量,FIFO大小,甚至可能包含一个微控制器来处理上层USB协议管理。这种外设控制器可以处理一些应用功能,从而不再需要FPGA或ASIC处理这些事务。如果他们包含RAM架构,开发人员还可以进行灵活的现场固件升级。

现在FPGA只需要掌握和这个芯片的逻辑接口。USB控制器和FPGA之间的接口可以是任何的标准接口,例如SPI,I2C,或HPI.还可能是自定义的接口,这在USB控制器IC中很普遍。

赛普拉斯的FX2LP 是专门的外设控制器芯片,其可以减少将USB集成到FPGA或ASIC系统的开发时间。它包含了一个简单的“从FIFO”接口,使得和FPGA系统互联很简单。从FIFO接口功能具备从读和从写信号,可以读或写数据到FX2LP 4 K FIFO空间。

对于与ASIC系统互联,FX2LP包含一个GPIF或通用可编程接口逻辑接口,可以为ASIC处理或通讯的任何标准接口生成接口波形。GPIF还可以通过USB接口配置FPGA,这样就不需要一个单独的配置芯片,例如PROM或处理器。通过USB配置FPGA也不再需要JTAG.因此,通用的专用的USB控制器可以不仅仅作为一个数据通道,还可以减少线路板尺寸和成本。

这篇文章里提到的这三种设计方法都有自己的优点和缺点。选择时要进行仔细分析,要权衡成本,线路板空间,和FPGA资源。

-

FPGA + USB2.0 PHY USB3300 实现高速USB2UART2024-09-02 8281

-

如何在FPGA和ASIC设计中结合高速USB功能2012-11-22 2968

-

USB2.0控制器CY7C68013芯片与FPGA芯片接口的Verilog HDL实现2019-05-10 2052

-

采用USB协议实现DSP高速上位机接口设计2019-05-31 2043

-

一种基于SOPC和USB2.0接口的高速数据采集系统及虚拟仪器设计2019-07-05 2015

-

怎么实现USB2.0 SIE的ASIC设计?2021-05-28 1494

-

基于Verilog的FPGA与USB 2.0高速接口设计2021-06-24 2913

-

USB2.0 接口和DSP 构成的高速数据采集系统2009-05-16 487

-

基于USB2.0与FPGA技术的高速数据采集系统的设计2009-04-22 2017

-

IR-UWB通信系统高速USB接口的设计与实现2010-03-13 2639

-

FPGA的嵌入式系统USB接口设计2010-04-03 2241

-

基于FPGA的高速USB2.0数据采集系统主控电路设计2016-01-04 590

-

基于Verilog的FPGA与USB 2.0高速接口设计资料下载2021-04-12 1404

-

FPGA_ASIC-MAC在FPGA中的高效实现2021-08-04 917

-

利用FPGA实现USB 2.0通信接口2024-12-30 4309

全部0条评论

快来发表一下你的评论吧 !