d锁存器cd4042的正确使用

电子常识

描述

什么是锁存器

锁存器(Latch)是一种对脉冲电平敏感的存储单元电路,它们可以在特定输入脉冲电平作用下改变状态。锁存,就是把信号暂存以维持某种电平状态。锁存器的最主要作用是缓存,其次完成高速的控制器与慢速的外设的不同步问题,再其次是解决驱动的问题,最后是解决一个 I/O 口既能输出也能输入的问题。锁存器是利用电平控制数据的输入,它包括不带使能控制的锁存器和带使能控制的锁存器。

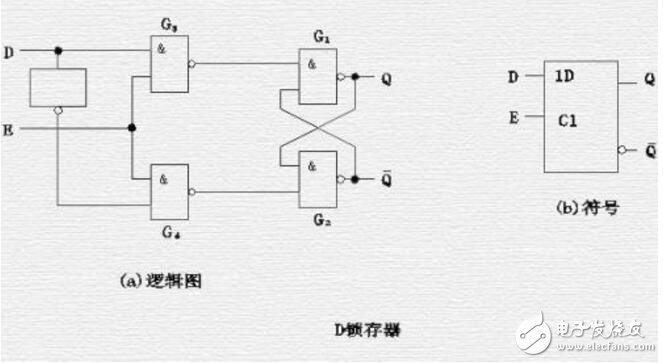

锁存器原理

CMOS反相器的功能是可以使输出获得跟输入相反的逻辑值,那如果把两个反相器的输入跟输出连接在一起会出现什么情况呢?我们来看下图,假设某个时刻反相器A的输入是1,那么其输出会是0;因为A的输出连接到B的输入端,即反相器B的输入为0,那么其输出会变为1;又因为B的输出连接到A的输入端,即B输出的1反馈回A的输入,对刚才假设的“A的输入为1”进行了确认和加强。此时A的输入确实为1,按A和B的输入输出连接关系,又走了一遍刚才的路程,如此循环,结果是反相器A的输出稳定为0,反相器B的输出稳定为1。这个结构的电路有两个稳定的状态,一般称之为双稳态电路。可见类似的双稳态电路可以稳定地保持其节点中的值(数据),具有记忆功能,这就是锁存器工作的原理。

锁存器应用

所谓锁存器,就是输出端的状态不会随输入端的状态变化而变化,仅在有锁存信号时输入的状态才被保存到输出,直到下一个锁存信号到来时才改变。

锁存器多用于集成电路中,在数字电路中作为时序电路的存储元件,在某些运算器电路中有时采用锁存器作为数据暂存器。封装为独立的产品后也可以单独应用,数据有效延迟于时钟信号有效。这意味着时钟信号先到,数据信号后到。

在某些应用中,单片机的I/O 口上需要外接锁存器。例如,当单片机连接片外存储器时,要接上锁存器,这是为了实现地址的复用。假设,MCU端口其中的 8 路的 I/O 管脚既要用于地址信号又要用于数据信号,这时就可以用锁存器先将地址锁存起来。

8051访问外部存储器时P0口和P2口共同做为地址总线,P0口常接锁存器再接存储器。以防止总线间的冲突。而P2口直接接存储器。因为单片机内部时序只能锁住P2口的地址,如果用P0口传输数据时不用锁存器的话,地址就改变了。

看看8051单片机总线操作的时序图对我们很有帮助。由于数据总线、地址总线共用P0口,所以要分时复用。先送地址信息,由ALE使能锁存器将地址信息锁存在外设的地址端,然后送数据信息和读写使能信号,在指定的地址进行读写操作。使用锁存器来区分开单片机的地址和数据,8051系列的单片机用的比较多,也有一些单片机内部有地址锁存功能,如8279就不用锁存器了。

CD4042介绍:

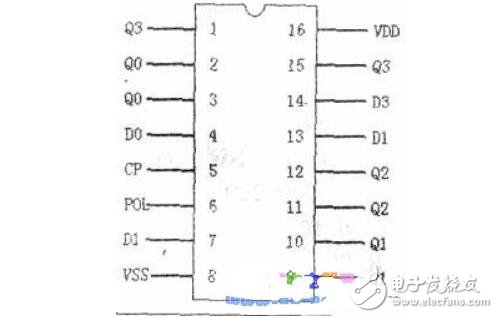

CD4042为时钟控制锁存D型触发器,逻辑单元相当于主一从型D型触发器中的其中一级触发器,因此数据从D端送到输出端Q只要一个电乎就可以了。当锁存器内部时钟为“L”低电平时传送数据,为“H”高电平时锁存数据。对于一个完整的四D锁存器,锁存器的时钟端CP和极性控制端POL经异或门后作为锁存器的内部时钟,因此,存人数据的条件发生在时钟CP和极性POL同相时,异相时位锁存。下图为它的引出端功能图。

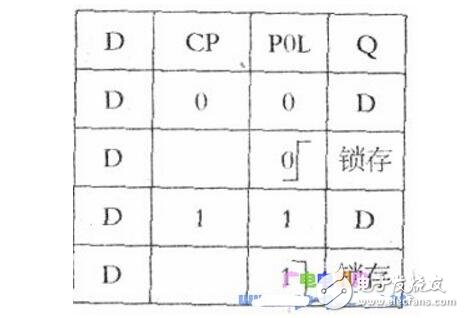

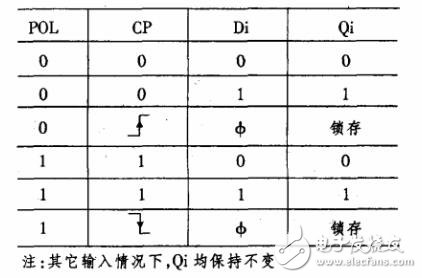

CD4042的主要特点是时钟脉冲CP的有效触发极性可以选择,这是由极性控制POL功能来实现的。CP和POL的信号成为异或门的两个输入信号,只有CP和POL逻辑状态相同时,D端数据才被传输至Q端,否则数据被锁存。POL为“O”,CP上升沿使数据D被锁存;POL为“1”,CP下降沿使数据D被锁存,如附表(真值表)。

d锁存器cd4042的正确使用

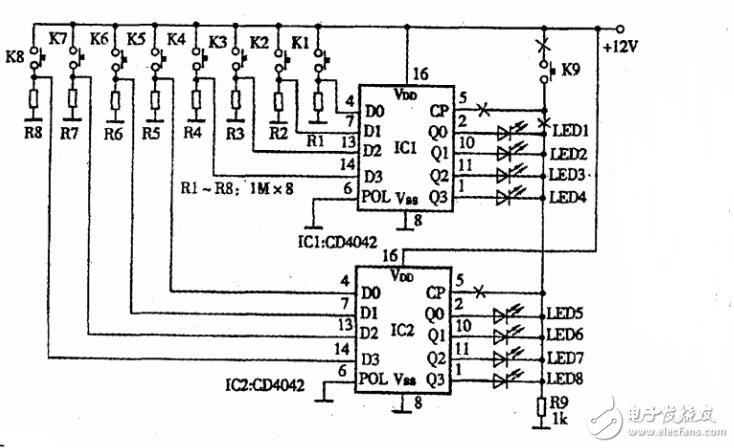

本文对此抢答器电路分析如下。CD4042是CMOS四-D锁存器,共16个引脚,其中DO、D1、D2、D2为数据输入端,Q0.Q1.Q2.Q3为相应的数据输出端,CP端为时钟脉冲,POL端为时钟脉冲极性控制。CD4042内部为四个主从结构的D触发器。当POL=O时,锁存器在CP的低电平期间开通,D0~D3的数据分别传送到Q0~Q3端,当CP的上升沿来到时数据被锁存,所以这时锁存的是CP上升沿来到前瞬间的数据;反之,当POL.=1时,锁存器在CP的高电平期间开通,当CP的下降沿来到时数据被锁存,这时锁存的是CP下降沿来到前瞬间的数据。其逻辑功能如附表所示。

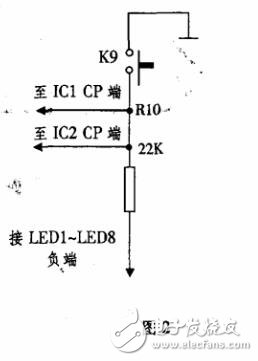

该款抢答器的抢答输入设计是成功的,工作原理原文已阐明,本文不再赘述。但为什么电路不能复位呢?这是因为复位前IC1、IC2的Q0~Q3共8个输出端必有一个为高电平(设IC1的QO端为高电平)。这时LED1亮,其导通压降约2V,所以CP端电位被LED1拉高;按下K9时,CP端接12V,仍为高电平,而POL恒接地,锁存器无法开通,原锁存数据不变,IC1的QO端仍保持高电平。尽管当K9按下时LED1两端因几乎无压差(实测)而熄灭,但K9一断开,LED1又会再亮。

由附表可知,要让锁存器在POL端接地时开通,并将D0-D3的数据“0”分别传送到Q0-Q3端,CP应接地才行。所以将复位开关K9的上端由原接电源+12V改为接地。k9的下端仍与两CP端相连。此外,K9的下端与LED1-LED8公共负极之间加串了一只限流电阻R10,其作用是避免在K9按下瞬间(原有一输出端呈高电平)电流对输出端及相应LED的冲击。

具体修改如下:断开图1右侧的4个打“x”处,再将围2的电路按标示接入图1即可。修改后的电路经实验工作正常。

-

CD4013锁存器的异或门输出信号是什么2019-04-30 2727

-

4042 CMOS 四时钟控制D锁存器2009-08-08 1425

-

常用CD系列触发器2006-04-17 4131

-

CD4042B-MIL CMOS 四路时钟“D”锁存器2018-11-02 833

-

CMOS 四时钟“D”锁存器CD4042B TYPES 数据表2024-05-20 464

-

CD4724B CMOS 8位可寻址锁存器数据表2024-06-03 343

全部0条评论

快来发表一下你的评论吧 !