modelsim仿真没有波形或看不到波形的原因及解决方法

嵌入式设计应用

描述

关于modelsim仿真时出现 No objects found matching ‘/*’ 问题在Modelsim6.2系列版本中仿真时,点击start simulateion后,出现Objects空白的问题,导致执行 add wave al l时出现“# (vish-4014) No objects found matching ‘/top_tb/*’。“的报错选项。尽管输入run后,可以运行仿真,但却无法察看wave窗口的波形。

这是优化的问题。

解决方法:

1. 点击工具栏中的“simulate”按钮,调出start smulation窗口,把窗口中最下边optimization栏中的Enable optimization项目前的钩钩去掉,然后选择仿真的文件,点击OK,就一切正常了,能看到objects了。

Quatus ii联合modelsim仿真无法产生波形或波形一直为Hiz状态原因分析

最近用用modelsim仿真Quatus写的testbench,遇到了波形无法产生的问题,一直卡在这里很久都没找到原因,经过一番分析和各种乱试,终于找到原因了。

在设置编译的test bench的时候,一定要把顶层模块设置为xx_vlg_tst(),就是启动test bench template writer的时候,软件给你自动产生的那个test bench的模块名。因为在仿真的时候,这个模块才是真正的顶层模块,是它实例化测试模块,并给与测试模块激励信号的。设置方法如下:

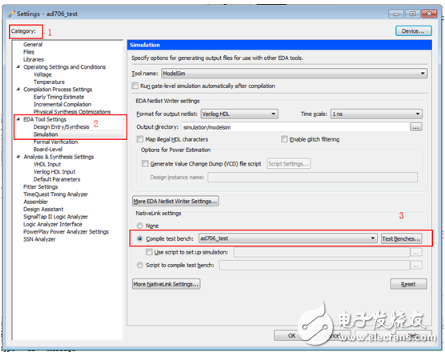

点击主界面菜单栏的Assignment——》Settings,出现Settings对话框,然后在Category栏选择EDA Tool Settings——》Simulation,出现以下界面,

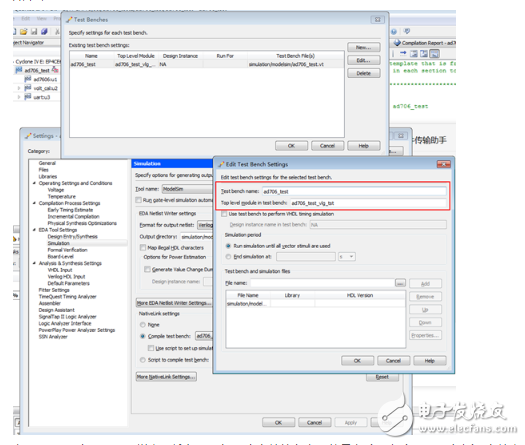

点击3右边的Test Benches按键,出现Test Benches对话框,然后点击该对话框右边的New按键,出现了Edit Test Bench Settings对话框,如下,

在Test Bench name一栏中,输入test bench文件的名字,就是在simulation/modelsim文件夹中那个后缀为.vt的文件的名称,而Top level module in test bench一栏则要输入test bench文件中那个模块的名称,这个是自动产生的,名字都是xx_vlg_tst,xx为test bench文件的名称,记住,这里一定要设置好顶层模块是xx_vlg_tst,因为默认情况下它是和test bench name是一样的,如果这样设置,是无法产生波形的。

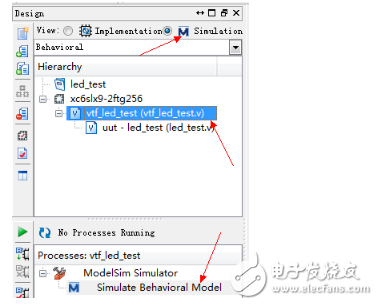

之前一直用ise联合modelsim仿真,ise里面就没有这些繁琐的步骤,在写test bench的时候,软件自动把test bench设置为了顶层模块,如图:

仿真的时候只需要点击vtf_xx.v文件,然后双击Simulate Behavioral Model就会调用modelsim,仿真test bench文件了。

modelsim仿真波形窗口小技巧

在编写verilog模块后,很重要的一部分就是对所编写的模块进行仿真。而在仿真过程中,很重要的一部分就是观察波形。这里所谈的技巧其实是对于我个人而言,可能大部分人都已经知道。但还是记录下来,算是对我自己的提醒吧。

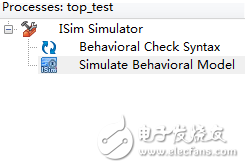

现在想想还是觉得好笑,以前每次打开波形窗口的时候,都是点击下图的Simulate Behavioral Model.每次修改了代码,都是关掉原来的波形窗口,然后再重新点击打开,麻烦程度不言而喻(好吧,当初因为程序简单,其实还不觉得很麻烦。)

现在明白了,对于这种情况,肯定是会有简单的操作的,否则这用户体验也太差了。

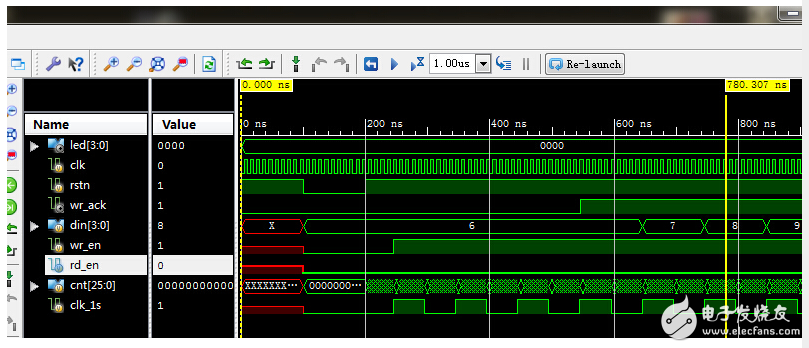

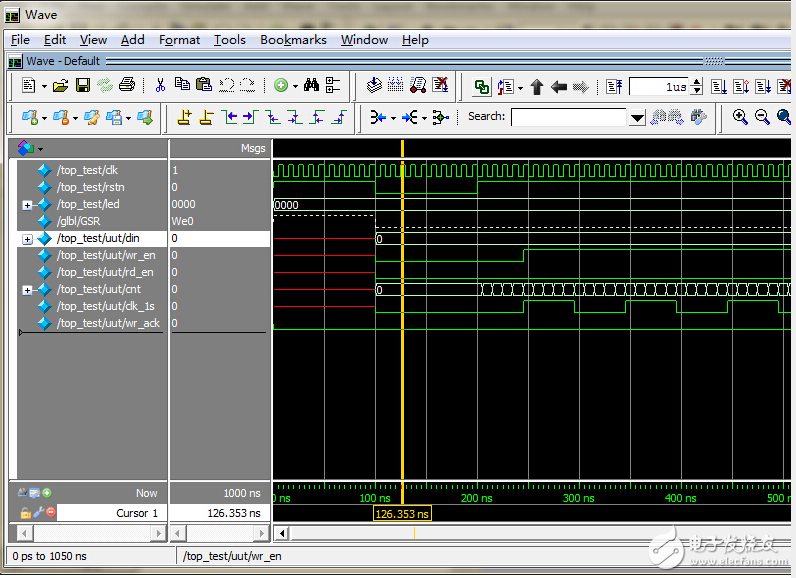

当然,第一次仿真打开波形窗口时,还是老方法,点击上图的Simulate Behavioral Model。添加内部信号以及修改数值进制后结果如下图(这里采用的是一个FIFO读写程序,程序不是这里需要在意的问题,我们只关心软件的操作)。

下面我们通过修改din[3:0]的初始值来反映这个过程,由上图可知,din[3:0]的初始值为6.接下来我把代码中din[3:0]的初始值改为0后重新观察波形,那该如何操作呢?千万不要像我以前那么傻的关掉现有窗口然后重新仿真打开了。这样我们又要重新添加内部信号以及修改数值显示了。

方便的步骤应该是,首先,将该波形保存,这部很简单就不贴图了,保存的其实就是你对该窗口的各种配置,哪怕以后你重新打开软件,也可以通过打开之前保存的波形配置来查看仿真波形,而不用重新配置了。

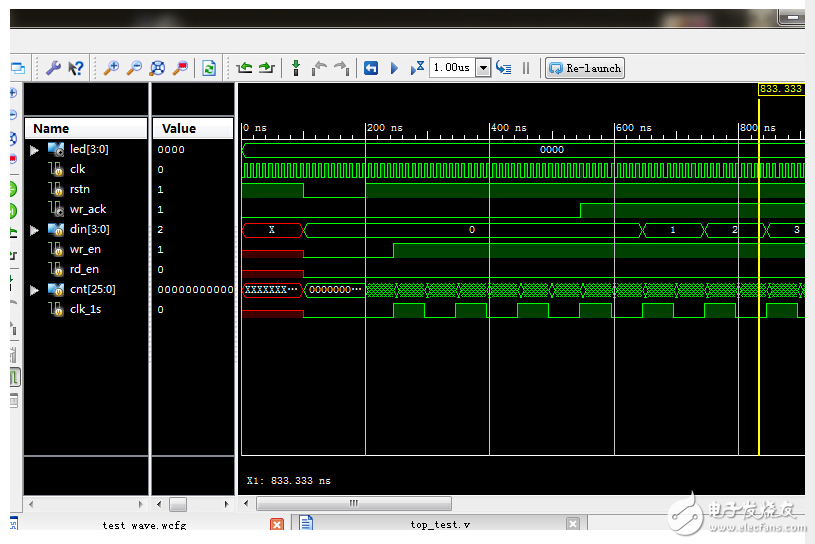

保存后,修改完代码(这里我把din[3:0]的初始值改为0,另外,代码要记得保存,保存后代码才能生效),然后点击波形窗口的re-launch(如果之前没进行保存操作的话,点击re-launch后软件也会提示你保存的)。就可以看到仿真波形发生了变化,din[3:0]的初始值由之前的6变成了0.

另外,关于re-launch边上的那几个按钮,也都是很有用处的,尤其仿真时间设置的,甚至有的时候还会因为这些设置的问题导致老是不能出现预期结果,这些操作很简单,就不一一解释了,大家稍微用用就知道了。

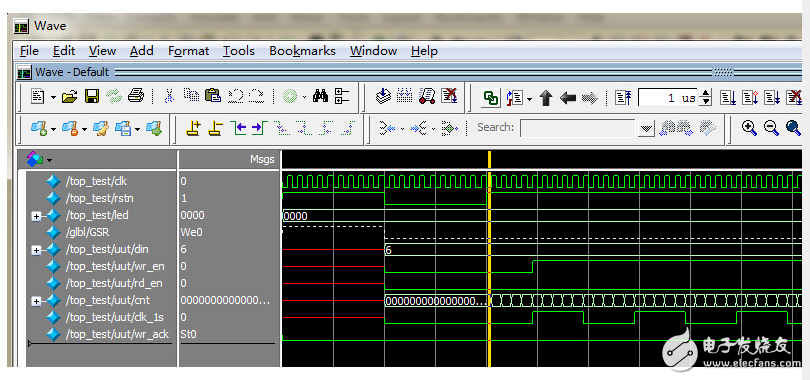

上面提到的是采用ISE自带的ISim进行仿真,但大多数时候我们还是采用modelsim来进行仿真,因为它功能更强大,速度也更快。但两者操作其实是有很多类似的地方的,不过通过ise启动modelsim再修改程序再仿真的操作还是挺麻烦的(可能还有更简便的方法我不知道吧,知道可以通过脚本的方法,把命令编成程序,然后自动执行操作,但此方法还不太会。)。还是以上面的程序为例。用ise启动modelsim,设置好参数后如图

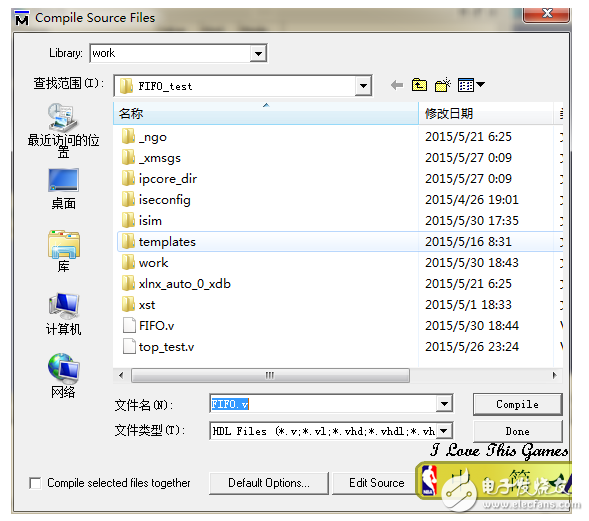

可以看到din初始值为6。当我们修改代码并保存后,在modelsim中要重新编译,点击compile,出现下面的对话框:

由于修改的是FIFO.v文件,因此重新编译该文件就好。

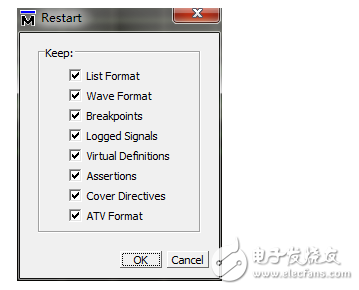

之后来到波形窗口,点击restart,

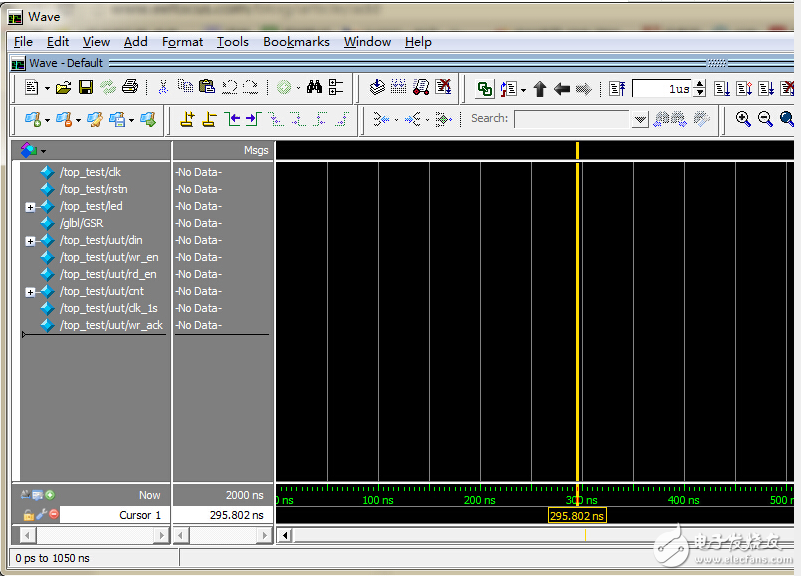

再点击OK,此时波形窗口无信号

此时只需要再点击一下run就好了

此时可以看到din的初始值已经变成0了。

其实这个过程还是有点麻烦,这就需要通过脚本操作了。或者我们不要通过ISE调用modelsim,而是直接使用modelsim,这样会方便并且快速许多。

-

FPGA开发:modelsim仿真流程及波形2020-09-30 12096

-

STM32 USART的配置完全按照书上的写的,但是仿真就是看不到波形是为什么?2024-05-13 262

-

TINA虚拟示波器看不到输出波形是为什么?2024-08-14 526

-

请问AFE4900EVM看不到ECG波形怎么办?2024-12-11 298

-

rom 的modelsim 仿真 问题 和 解决方法2014-03-06 14382

-

我这个哪里出问题了 仿真出来波形怎么看不到2015-01-07 3311

-

为什么示波器看不到完整波形?2016-04-18 27063

-

Proteus仿真用示波器看波形,看不到0电平在哪里,请问如何设置可以显示0电平线?2017-01-18 10780

-

ISE webpack看不到测试台波形选项2019-05-28 1600

-

【Modelsim常见问题】仿真不出波形,波形窗口无内容2020-02-13 8811

-

modelsim保存波形操作方法解析2017-11-24 18715

-

怎样利用modelsim仿真波形图案来显示字符?2021-06-26 4004

-

如何夹带modelsim的仿真波形白底黑线2021-08-26 5017

-

keil5软件仿真没有实时波形2021-11-23 1090

-

modelsim波形仿真的基本操作了解2022-11-29 4883

全部0条评论

快来发表一下你的评论吧 !