modelsim显示模拟波形详解

嵌入式设计应用

描述

虽然Modelsim的功能非常强大,仿真的波形可以以多种形式进行显示,但是当涉及到数字信号处理的算法的仿真验证的时候,则显得有点不足。而进行数字信号处理是Matlab的强项,不但有大量的关于数字信号处理的函数,而且图形显示功能也很强大,所以在做数字信号处理算法的FPGA验证的时候借助Matlab会大大加快算法验证的速度。

ModelSim显示模拟波形

问题是,要看一个振幅调制的输出波形,ModelSim默认的是数字输出,想直接看波形。

这个问题应该不难,想想看ModelSim肯定支持这种功能,只是要摸索一下。一般都是点右键,果然有一个Format,里面有一个Analog选项,点上它,弹出了对话框,先用默认的试试看,输出波形感觉显示的幅度太小,看起来不方便,再回过头来把对话框里的值调整一下,得到了一个比较好的波形。不过问题就出现了,出来的波形上下重叠了。

菜单栏里逐个找了一遍,发现也有一个Format,里面有height这个选项。打开看,默认是17,改大一点看,比如50,输出显示的信号之间的间距就拉大了,就不会再重叠了。

很多朋友都不知道怎样用Modelsim仿真模拟波形。下面是我的一些心得

1 需要查看正弦波的变量必须为多比特变量。

2 关于Analog选项

Analog step ——应该是显示锯齿波形

Analog Interpolated ——按插值显示

Analog Backstep ——分段显示模拟波形

scale——按比例显示

offset——偏移量

modelsim中显示正弦波

在一般情况下,我们仅仅需要看到数据的二进制或者十六进制,但是当信号为方波正弦波信号或者为频谱信号时候,在仿真过程中,如果能够显示出波形信号,那么仿真结果将更加直观,由于公司不能上网,所以在家实现该仿真功能,结果如下:

第一步:生成sin波形文件(sin.txt)

这一步使用matlab完成,matlab中的代码如下:

fc = 10e6;

n = 1/fc/256;

t = [0:255]*n;

x = sin(2*pi*fc*t);

xx = fix(128+(2^7-1)*x);

y = dec2hex(xx);

解释:

在一个周期采样256个点,fix函数是将数据向0取整,例如1.1变成1,1.2也变成1.这里先将正弦波幅值变成128.最后将数据变成16进制。最后将y的值存到sin.txt文件中,结果如下图所示:

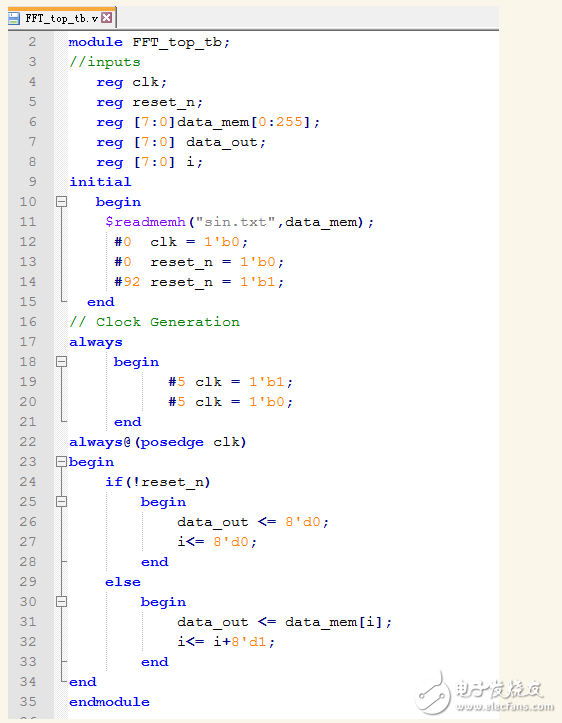

第二步:编写testbench文件

编写testbench的原理不解释,如下图所示:

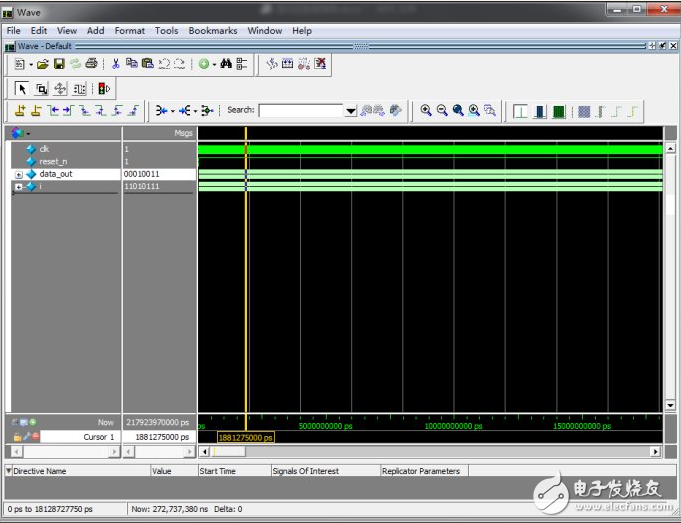

第三步:运行modelsim

对于这样只有tb文件而没有其他模块的仿真对于我还是第一次,首先新建工程,添加文件后,编译,仿真,添加信号,结果如下图所示。

这时候信号显示为二进制,其中data_out就是正弦波信号,如果要将这个信号在modelsim中显示为正弦波图形,需要进行下面设置:

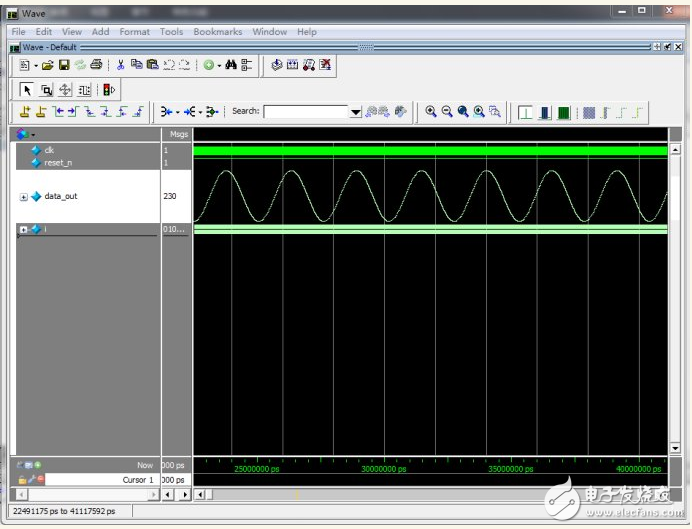

1、选择data_out信号,右击—》Radix—》Unsigned

2、选择data_out信号,右击—》Format—》Analog(automatic)

设置好后,就可以显示正弦波,如下图所示。

其实这个仅仅是为了后面做FFT的仿真做铺垫,后期将会对其频谱进行图形显示。

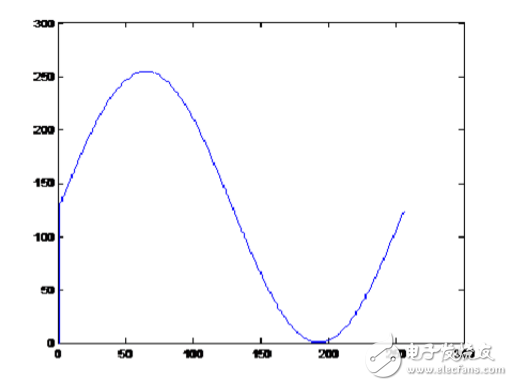

下面一段Matlab的程序是将数据读取,并通过图形显示出数据的波形。

fid = fopen(‘data_out.txt’,‘r’);

num(i) = fscanf(fid, ‘%x’, 1); %

这句话的意思是从fid所指的文件以16进制方式读出一个数据。

第一:保证读取的数据格式和文件中保存的数据格式是相同的,例如这里文件中保存的格式是十六进制所以读取的时候也应该以十六进制的形式读出。

第二:要保证文件中数据的个数和设定的读取的数目(这里是256)保持一致。例如,要将生成文件data_out.txt中多余的换行符去掉(一般最后会多出一行),否则Matlab会将空的行也当做一个数据,从而两个数目不一致,导致Matlab报错。

当然,有了Matlab这个强大的工具,也就可以很方便的看信号的频谱等信息了。

另外在说一点,就是关于通过Verilog将数据写入文件有多种方法,上面用的是$fdisplay这个系统函数,当然还有$fmonitor和$fwrite等几个命令,下面简单说一下这几个命令的不同。 $fdisplay

这个命令需要有触发条件,才会把数据写入文件,例如,上例的触发条件就是always(i),当i变化的时候才写入。每写入一次数据会自动增加一个换行符。 $fmonitor

关于Matlab的函数有:fopen, 关于Modelsim的函数有:$fopen, $fclose,$readmemh,$readmemb,$fmonitor,$fdisplay,$fwrite。

这个命令不需要触发条件,只要有变化就可以将数据写入文件。例如可以通过以下语句: initial $fmonitor(w_file,“%h”,data_out);

这样可以将整个仿真过程产生的data_out数据都写入文件中。 $fwrite

这个命令和$fdisplay基本相同,也是需要触发条件才会写入,不同的是每写入一个数据不会自动添加换行符。例如可以通过以下语句: always @(posedge clk) begin

$fwrite(w_file,“%h ”,data_out); end

关于这几个命令的详细介绍,大家可以参考Verilog的相关数据。

- 相关推荐

- 热点推荐

- ModelSim

-

FPGA开发:modelsim仿真流程及波形2020-09-30 12096

-

请教在ISE自带的ISIM中怎么让数据显示成模拟波形.2014-09-12 13408

-

signaltap波形模拟出错2018-01-24 4572

-

ModelSim软件详解2019-04-11 2097

-

modelsim仿真$display的打印结果没有显示2019-10-16 3327

-

【工程源码】基于FPGA的Modelsim修改波形显示颜色2020-02-20 2077

-

Modelsim仿真模拟波形问题,数值有差距但在波形上显示如同一条直线,如何解决?2020-02-28 9319

-

modelsim仿真的模拟波形显示问题2020-03-17 2863

-

数字波形详解2009-04-06 20553

-

使用 ModelSim 进行设计仿真详解2015-12-24 983

-

modelsim保存波形操作方法解析2017-11-24 18714

-

怎样利用modelsim仿真波形图案来显示字符?2021-06-26 4004

-

探究Modelsim仿真--波形状态机名称显示2021-07-23 2790

-

如何夹带modelsim的仿真波形白底黑线2021-08-26 5017

-

modelsim波形仿真的基本操作了解2022-11-29 4883

全部0条评论

快来发表一下你的评论吧 !