Modelsim软件如何仿真,怎么能添加输入信号?

嵌入式设计应用

描述

Modelsim软件介绍

Modelsim是Mentor公司开发的专业仿真软件,支持VHDL、VerilogHDL和混合仿真的全系列流程。作为目前最流行的仿真工具之一,Modelsim提供了图形界面和命令行两种工作模式,既可以方便地使用鼠标和对话框完成大部分的仿真操作,也可以通过编写宏指令执行由文件驱动的工作流程以提高效率。

Modelsim的仿真方法

Modelsim的仿真分为前端仿真和后端仿真,下面简单介绍一下两者的区别。

前端仿真:也称为功能仿真,主旨在于验证电路的功能是否符合设计要求,其特点是不考虑电路门延迟与线延迟,主要是验证电路与理想情况是否一致。

后端仿真:也称为时序仿真或者布局布线后仿真,是指电路已经映射到特定的工艺环境以后,综合考虑电路的路径延迟与门延迟的影响,验证电路能否在一定时序条件下满足设计构想的过程,是否存在时序违规。其输入文件为从布局布线结果中抽象出来的门级网表、Testbench和扩展名为SDO或SDF的标准时延文件。SDO或SDF的标准时延文件不仅包含门延迟,还包括实际布线延迟,能较好地反映芯片的实际工作情况。一般来说后仿真是必做的。

用verilog,写生成信号的模块,称为testbench, 把testbench和待仿真的模块一起放在一个顶层里一起跑,波形就来了

IP核生成文件:(Xilinx/Altera 同) IP核生成器生成 ip 后有两个文件对我们比较有用,假设生成了一个 asyn_fifo 的核,则asyn_fifo.veo 给出了例化该核方式(或者在 Edit-》Language Template-》COREGEN 中找到verilog/VHDL 的例化方式)。asyn_fifo.v 是该核的行为模型,主要调用了 xilinx 行为模型库的模块,仿真时该文件也要加入工程。

调试方便。在 ISE/Quartus 中调用 modelsim仿真只能看到输入输出信 号,而对于设计的中间信号/变量,特别是ip核的内部信号/变量无法观测。而在modelsim中直接仿真可以观测设计中出现的任何信号/变量无和 ip 核内的任何信号/变量,这样我们设计的数据流向就可以很清楚的表示出来,还可以检测不同编程方式的处理效果,极大的方便了调试。

modelsim中输入信号的波形如何设置?

做好仿真(仿真波形之前保存了,如果正在仿真,那更好),那么打开波形文件。找到tools-edit preferences。找到by windows-wave windows,可以看到一系列可以更改颜色的列表。

比如想把波形的背景颜色变成白色的,那么选择wavebackground,然后把它选择成白色的,确认后波形就变成白色的了。

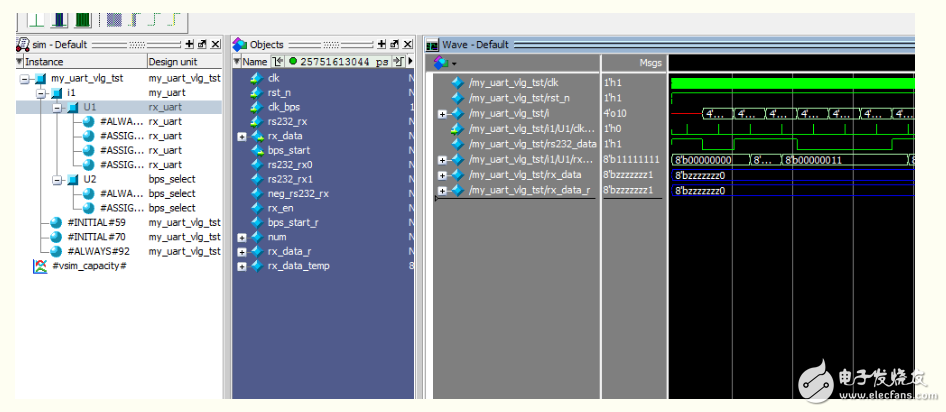

Modelsim仿真如何查看内部信号

一般Modelsim看的信号波形都是test bench中定义的默认信号。有时候需要看模块内部信号。

可以选择sim窗口,查看internal,一般选择需要查看的信号在Objects窗口出现的信号,根据需要直接拖到Wave窗口即可。

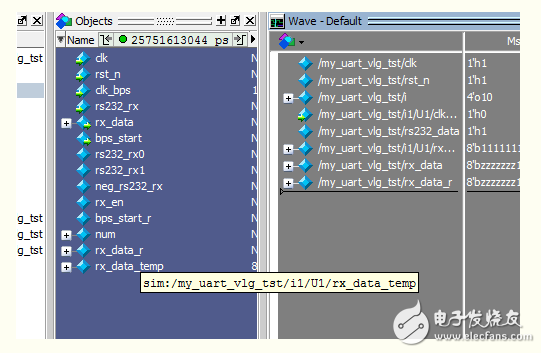

还可以采用的方法是在Transcript窗口输入命令add wave /testbench_name/design_unit_name/signal_name。该名字为其选择信号的路径。若不太清楚可以在Object窗口在需要信号的上面悬浮鼠标可以显示器路径,如图所示。

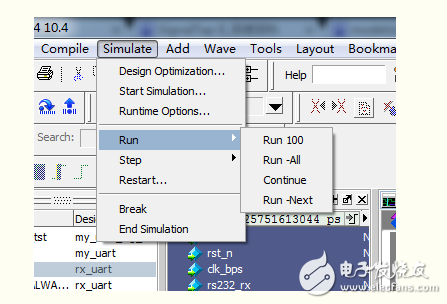

但是上述方法查看波形比较麻烦,因为每次从Quartus中调用Modelsim时都会进行默认配置,这就需要你每次查看内部信号,都得新添加该信号,而却还得选择simulate -》start simulation,添加信号后,在选择 run -》run-all。还存在个问题就是,仿真波形,只能显示此刻开始以后的。不能查看先前的。

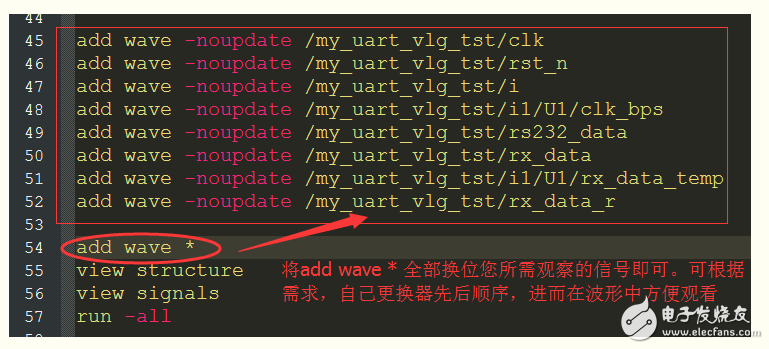

若果要从开始查看波形信号变化情况,建议添加信号放在脚本文件(.do)文件中,然后在quartus仿真配置中,勾选use script to set up simulation,选择 (.do)文件路径。这样每次仿真就会按照文件中的命令逐条执行。

关于脚本写法如图所示

这样只要在quartus中设置好这个(.do)文件,modelsim就会按照自上而下产生所需波形。而且每次调试仿真不必再退出modelsim,直接在Transcript中,输入quit -sim,可退出当前仿真结果,再输入do **.do(及所需的.do文件),即可进行调试仿真。

-

jintama

2018-03-22

0 回复 举报真的太有用了!! 收起回复

jintama

2018-03-22

0 回复 举报真的太有用了!! 收起回复

-

【产品介绍】Modelsim:HDL语言仿真软件2025-11-13 780

-

如何在ModelSim中添加Xilinx仿真库2024-07-03 802

-

vivado软件和modelsim软件的安装方法2023-08-07 9597

-

Vivado调用Modelsim仿真2023-07-24 5970

-

ModelSim手动仿真教程2022-07-11 6693

-

Vivado调用Questa Sim或ModelSim仿真小技巧2021-09-02 10640

-

基于ModelSim使用二联合Quarus自动仿真教程2021-07-23 3360

-

Modelsim与MATLAB的联合仿真2021-06-01 1175

-

Modelsim仿真教程Modelsim的基础入门基础教程免费下载2019-04-30 1667

-

仿真软件ModelSim及其应用,ModelSim的仿真流程2018-12-29 10816

-

在ModelSim中添加xilinx仿真库2018-09-12 2308

-

【锆石A4 FPGA试用体验】ModelSim(二) 手动仿真2016-09-06 4208

-

使用 ModelSim 进行设计仿真详解2015-12-24 1001

-

Altera ModelSim 6.5仿真入门教程2012-08-15 2639

全部0条评论

快来发表一下你的评论吧 !